Frequency Multipliers

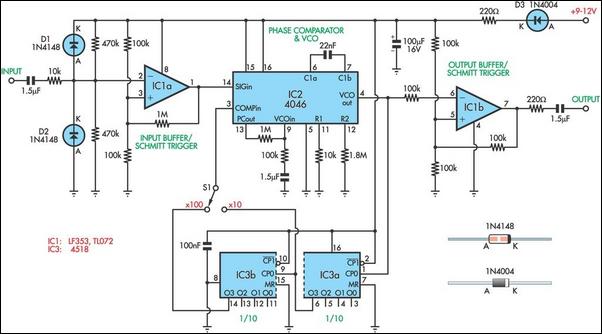

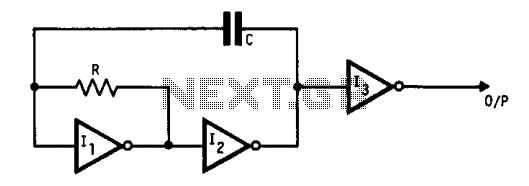

J1 and J2 are a matched pair of J310s (alternatively, U310s or a U431 matched pair can be used). R2 is chosen to bias the two FETs with a small drain current in the absence of RF input. The turns ratio of the input transformer is selected to achieve an approximate 50-ohm impedance match at the transformer primary (L1). The combined drain current waveform is a rectified sine wave superimposed on a small DC offset. At UHF frequencies, it is beneficial to reduce the drain load impedance and the impedance observed by the JFET sources; therefore, higher Idss low-capacitance JFETs are necessary. Higher frequency operation is feasible if Guanella baluns are used in place of the input and output transformers. For clarity, no parasitic suppression components are included in the schematic. The simulated waveforms in LTSpice indicate that the drain current waveform is a rectified sine wave with a small DC current superimposed. A small, predominantly second harmonic component of drain current flows through the drain-gate capacitance of the JFET, particularly noticeable when the source current of each JFET is cut off. The JFETs achieve frequency doubling primarily through switching action rather than the square law input characteristic. The output frequency spectrum of the doubler for a 10 MHz +13 dBm input is displayed below (reference level is 1V RMS). The output level of the frequency-doubled component (20 MHz) is slightly above +13 dBm. The low phase noise common base BJT frequency doubler shown is capable of excellent performance despite using inexpensive transistors. The low DC gain from base to collector of the dual transistor, combined with emitter degeneration, ensures low phase noise. This circuit is designed for input frequencies of 5 MHz or 10 MHz. Like all frequency doublers, it exhibits the lowest output phase noise with higher input signals, designed for an input of +13 dBm and intended to drive a 50-ohm load (higher load impedances may cause the transistors to enter saturation). The combined collector current waveform is a rectified sine wave with a small DC offset. The lowest signal phase instability is achieved when a low-pass filter with minimal phase shift at the desired output frequency (2f) is used in conjunction with relatively high Q series tuned circuits connected between the common collectors and ground. These tuned circuits suppress unwanted frequency components in the output (fundamental (f), 3f, 4f, etc.). Components at f, 3f, 5f, etc. arise from inevitable transistor and transformer mismatches; however, they will have relatively low amplitudes. The high Q series resonant tuned circuits (at f, 3f, 5f, etc.) contribute negligible phase shift and associated instability at the desired 2f output frequency.

The described circuit employs a pair of JFETs (J1 and J2) to facilitate frequency doubling, specifically utilizing J310, U310, or U431 devices. The biasing resistor R2 is critical for establishing a small drain current under no RF conditions, which aids in maintaining linearity and stability of the FETs during operation. The input transformer (L1) is designed with a specific turns ratio to ensure a 50-ohm impedance match, optimizing power transfer and minimizing reflections.

In terms of performance at UHF frequencies, the circuit benefits from the use of JFETs with higher Idss values and lower capacitance, which are essential for maintaining efficiency and reducing losses. The substitution of Guanella baluns for transformers enhances frequency response and allows for better handling of high-frequency signals.

The LTSpice simulation results provide insight into the operational characteristics of the circuit, revealing a rectified sine wave current profile with a DC offset. This waveform behavior is indicative of the frequency doubling action, where the JFETs switch at twice the input frequency, producing a second harmonic output. The phase noise characteristics are notably improved through careful design choices, such as the inclusion of emitter degeneration in the BJT frequency doubler, which mitigates the effects of noise and instability.

To further refine the output signal, the incorporation of low-pass filters and high Q tuned circuits is essential. These components work collectively to filter out unwanted harmonics and maintain signal integrity at the desired output frequency. The design is particularly sensitive to load impedance, with a specified optimal load of 50 ohms to prevent saturation of the transistors, ensuring consistent performance across varying operating conditions. Overall, the circuit is engineered for high efficiency and low phase noise, making it suitable for applications requiring reliable frequency doubling at UHF frequencies.J1 And J2 are a matched pair of J310`s (can also use U310`s or a U431 matched pair). R2 is selected to bias the 2 FETs with a small drain current with no RF input. The turns ratio of the input transformer is selected for an approximate 50 ohm impedance match at the transformer primary (L1). The combined drain current waveform is a rectified sinewave superimposed on a small dc offset (see below).

At UHF it is desirable to reduce the drain load impedance and the impedance seen by the JFET sources, thus higher Idss low capacitance JFETs are required. Higher frequency operation is possible if Guanella baluns are substituted for the input and output transformers.

N. B. for clarity no parasitic suppression components are shown in the schematic. As shown in the (LTSpice) simulated waveforms shown above the drain current waveform is a rectified sinewave with a small dc current superimposed. There is also a small predominantly 2nd harmonic component of drain current flows via the drain gate capacitance of the JFET.

This is particularly evident when the source current of each JFET is cutoff. NB the JFETS perform the frequency doubling principally by switching action and not due to the JFET square law input characteristic. The output frequency spectrum of the doubler for a 10MHz +13dBm input as seen at the load is displayed below (reference level is 1V rms).

The output level of the frequency doubled component (20MHz)is slightly more than +13dBm. The low phase noise common base BJT frequency doubler shown above is capable of very good performance despite the fact that it uses inexpensive transistors. The low dc gain from base to collector of the dual transistor coupled with the emitter degeneration ensures low phase noise.

The circuit is intended for use with 5MHz or 10MHz input frequencies. Like all frequency doublers it has lowest output phase noise with higher input signals. it is designed for an input of +13dBm and is intended to drive a 50 ohm load (higher load impedances may cause the transistors to enter saturation). The combined collector current waveform is a rectified sinewave superimposed on a small dc offset. Lowest signal phase instability is obtained when a low pass filter with low phase shift at the desired output frequency(2f) is combined with relatively high Q series tuned circuits connected between the common collectors and ground.

These tuned circuits suppress the unwanted frequency components in the output (fundamental (f) 3f, 4f etc). The components at f, 3f, 5f etc are due to inevitable transistor and transformer mismatches, however they will have relatively low amplitudes.

The high Q series resonant (at f, 3f, 5f etc) tuned circuits will contribute little phase shift and associated instability at the desired 2f output frequency. 🔗 External reference

The described circuit employs a pair of JFETs (J1 and J2) to facilitate frequency doubling, specifically utilizing J310, U310, or U431 devices. The biasing resistor R2 is critical for establishing a small drain current under no RF conditions, which aids in maintaining linearity and stability of the FETs during operation. The input transformer (L1) is designed with a specific turns ratio to ensure a 50-ohm impedance match, optimizing power transfer and minimizing reflections.

In terms of performance at UHF frequencies, the circuit benefits from the use of JFETs with higher Idss values and lower capacitance, which are essential for maintaining efficiency and reducing losses. The substitution of Guanella baluns for transformers enhances frequency response and allows for better handling of high-frequency signals.

The LTSpice simulation results provide insight into the operational characteristics of the circuit, revealing a rectified sine wave current profile with a DC offset. This waveform behavior is indicative of the frequency doubling action, where the JFETs switch at twice the input frequency, producing a second harmonic output. The phase noise characteristics are notably improved through careful design choices, such as the inclusion of emitter degeneration in the BJT frequency doubler, which mitigates the effects of noise and instability.

To further refine the output signal, the incorporation of low-pass filters and high Q tuned circuits is essential. These components work collectively to filter out unwanted harmonics and maintain signal integrity at the desired output frequency. The design is particularly sensitive to load impedance, with a specified optimal load of 50 ohms to prevent saturation of the transistors, ensuring consistent performance across varying operating conditions. Overall, the circuit is engineered for high efficiency and low phase noise, making it suitable for applications requiring reliable frequency doubling at UHF frequencies.J1 And J2 are a matched pair of J310`s (can also use U310`s or a U431 matched pair). R2 is selected to bias the 2 FETs with a small drain current with no RF input. The turns ratio of the input transformer is selected for an approximate 50 ohm impedance match at the transformer primary (L1). The combined drain current waveform is a rectified sinewave superimposed on a small dc offset (see below).

At UHF it is desirable to reduce the drain load impedance and the impedance seen by the JFET sources, thus higher Idss low capacitance JFETs are required. Higher frequency operation is possible if Guanella baluns are substituted for the input and output transformers.

N. B. for clarity no parasitic suppression components are shown in the schematic. As shown in the (LTSpice) simulated waveforms shown above the drain current waveform is a rectified sinewave with a small dc current superimposed. There is also a small predominantly 2nd harmonic component of drain current flows via the drain gate capacitance of the JFET.

This is particularly evident when the source current of each JFET is cutoff. NB the JFETS perform the frequency doubling principally by switching action and not due to the JFET square law input characteristic. The output frequency spectrum of the doubler for a 10MHz +13dBm input as seen at the load is displayed below (reference level is 1V rms).

The output level of the frequency doubled component (20MHz)is slightly more than +13dBm. The low phase noise common base BJT frequency doubler shown above is capable of very good performance despite the fact that it uses inexpensive transistors. The low dc gain from base to collector of the dual transistor coupled with the emitter degeneration ensures low phase noise.

The circuit is intended for use with 5MHz or 10MHz input frequencies. Like all frequency doublers it has lowest output phase noise with higher input signals. it is designed for an input of +13dBm and is intended to drive a 50 ohm load (higher load impedances may cause the transistors to enter saturation). The combined collector current waveform is a rectified sinewave superimposed on a small dc offset. Lowest signal phase instability is obtained when a low pass filter with low phase shift at the desired output frequency(2f) is combined with relatively high Q series tuned circuits connected between the common collectors and ground.

These tuned circuits suppress the unwanted frequency components in the output (fundamental (f) 3f, 4f etc). The components at f, 3f, 5f etc are due to inevitable transistor and transformer mismatches, however they will have relatively low amplitudes.

The high Q series resonant (at f, 3f, 5f etc) tuned circuits will contribute little phase shift and associated instability at the desired 2f output frequency. 🔗 External reference