Frequency tripler

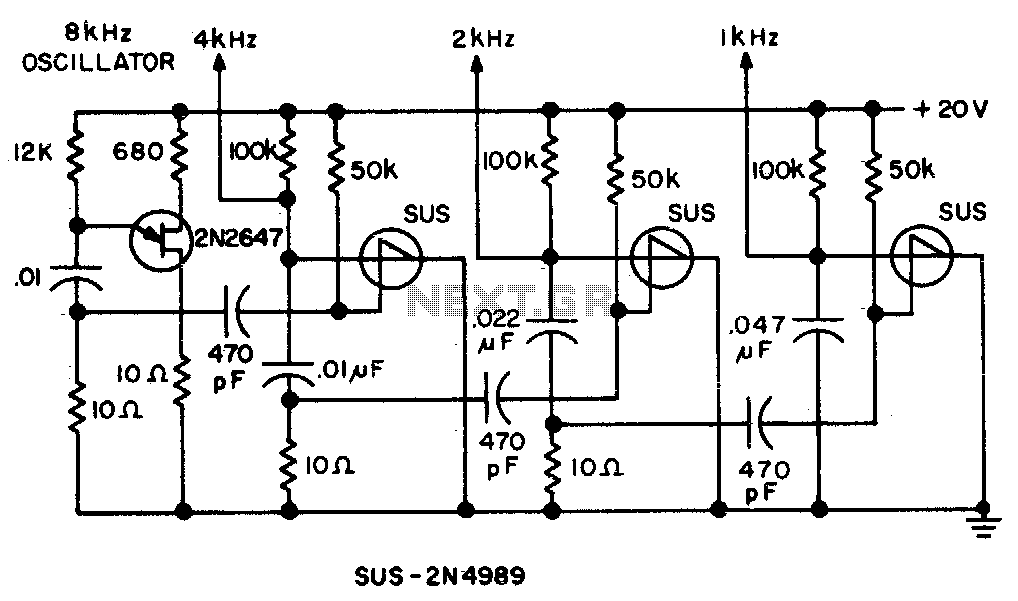

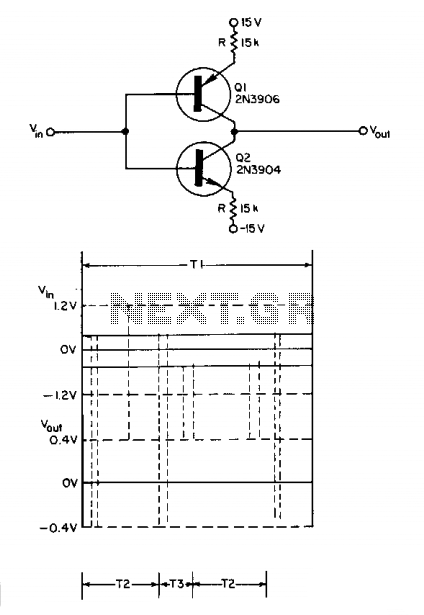

The turn-on and turn-off characteristics of two complementary transistors can be combined to achieve nonselective frequency tripling. The resulting circuit processes any periodic waveform with non-vertical edges. Each peak of the input signal generates three output signal peaks. The extra peaks arise when the input signal causes one of the two transistors to reach saturation. This circuit functions across a frequency range from direct current (DC) to the upper limits of the complementary transistor pair.

The primary function of this circuit is to utilize the switching characteristics of complementary transistors, typically a PNP and an NPN transistor, to achieve frequency tripling. The design leverages the unique turn-on and turn-off behavior of the transistors to manipulate the input waveform effectively. When a periodic signal is applied, the transistors alternately saturate and cut off, resulting in the generation of additional peaks in the output waveform.

The circuit can be visualized as having an input stage where the periodic waveform is fed into the base terminals of the transistors. As the input signal rises, one transistor turns on while the other turns off, allowing current to flow through the collector-emitter path. This action creates a corresponding output peak. When the input signal reaches a certain threshold, the first transistor saturates, causing the second transistor to turn on, which generates the second output peak. This process continues, resulting in the tripling of the frequency of the original input signal.

The output waveform will contain three distinct peaks for every cycle of the input waveform, effectively tripling the frequency. However, the circuit's performance may be compromised by the asymmetry of the output peaks, which can lead to distortion in the final signal. This lack of symmetry arises from the inherent differences in the turn-on and turn-off times of the complementary transistors, which can be influenced by factors such as transistor characteristics and circuit design.

This circuit's operational frequency range extends from DC up to the maximum frequency that the selected complementary transistor pair can handle, making it versatile for various applications in signal processing. The design can be further optimized by selecting transistors with matched characteristics to minimize output asymmetry and improve overall performance.The turn-on and turn-off characteristics of two complementary transistors can be combined to attain nonselective frequency tripling. The resulting circuit handles any periodic waveform with nonvertical sides. Each input signal peak produces three output signal peaks. The additional peaks occur where the input signal causes saturation of one of the two transistors. The circuit operates over a frequency range from dc to the upper limits of the complementary transistor pair.

About the only disadvantage of the circuit is the lack of symmetry of the output signal peaks. 🔗 External reference

The primary function of this circuit is to utilize the switching characteristics of complementary transistors, typically a PNP and an NPN transistor, to achieve frequency tripling. The design leverages the unique turn-on and turn-off behavior of the transistors to manipulate the input waveform effectively. When a periodic signal is applied, the transistors alternately saturate and cut off, resulting in the generation of additional peaks in the output waveform.

The circuit can be visualized as having an input stage where the periodic waveform is fed into the base terminals of the transistors. As the input signal rises, one transistor turns on while the other turns off, allowing current to flow through the collector-emitter path. This action creates a corresponding output peak. When the input signal reaches a certain threshold, the first transistor saturates, causing the second transistor to turn on, which generates the second output peak. This process continues, resulting in the tripling of the frequency of the original input signal.

The output waveform will contain three distinct peaks for every cycle of the input waveform, effectively tripling the frequency. However, the circuit's performance may be compromised by the asymmetry of the output peaks, which can lead to distortion in the final signal. This lack of symmetry arises from the inherent differences in the turn-on and turn-off times of the complementary transistors, which can be influenced by factors such as transistor characteristics and circuit design.

This circuit's operational frequency range extends from DC up to the maximum frequency that the selected complementary transistor pair can handle, making it versatile for various applications in signal processing. The design can be further optimized by selecting transistors with matched characteristics to minimize output asymmetry and improve overall performance.The turn-on and turn-off characteristics of two complementary transistors can be combined to attain nonselective frequency tripling. The resulting circuit handles any periodic waveform with nonvertical sides. Each input signal peak produces three output signal peaks. The additional peaks occur where the input signal causes saturation of one of the two transistors. The circuit operates over a frequency range from dc to the upper limits of the complementary transistor pair.

About the only disadvantage of the circuit is the lack of symmetry of the output signal peaks. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713