Interfacing to LVDS with the NI 655X Digital Waveform Generator/Analyzer

The NI 655X is a versatile high-speed digital product capable of interfacing with various technologies. This application note illustrates how to connect the NI 655X to Low Voltage Differential Signaling (LVDS) devices. LVDS is an emerging differential digital standard utilized in numerous communication and mixed-signal applications. The electrical characteristics of an LVDS signal can lead to significant performance enhancements compared to single-ended standards. For instance, since the received voltage is the differential between two signals, the voltage difference between the logic high and low states can be minimal, facilitating faster rise and fall times. Another distinctive feature of LVDS is its current-driven nature, necessitating proper termination and current-return paths in applications. A current source at the driver delivers approximately 3.5 mA of current, with the direction of current flow across the transmission line determined by whether the driver is outputting a logic high or low level. At the receiver end, a 100-ohm terminating resistor connects the two ends of the transmission line, providing a return path for the current. A differential voltage of approximately 350 mV is established across the two input terminals of the differential receiver, which can be either positive or negative based on the current direction. The receiver interprets the signal as high or low level depending on the polarity of this voltage. As previously mentioned, LVDS operates on a differential, current-driven principle, while the 655X functions as a single-ended, voltage-driven digital waveform generator and analyzer. However, the 655X product family is designed to seamlessly interact with LVDS devices. LVDS signals can be generated using two DIO channels to create the two ends of the differential signal. The output terminals of the 655X devices have a 50-ohm source impedance that must be accounted for when configuring voltage levels for generation. Setting the generation voltage high level to 1.7 V and the low level to 0.7 V is effective, resulting in a current of 5 mA through the circuit and generating a voltage of 500 mV at the receiver. The LVDS specification permits an input voltage range from 0 to 2.4 V, allowing for a broad spectrum of acceptable values. In this scenario, the common-mode voltage at the receiver is 1.2 V, which falls within the ideal range for LVDS. Programming the 655X for this generation process resembles programming for a standard single-ended operation. As depicted in the figures, two channels are configured for generation. After setting the clock rate, the voltage levels are adjusted to the appropriate values, and the device downloads the waveform. It is important to note that the data for the two channels are always inversely related. Additionally, the NI 5421 is another product capable of generating 16 channels of LVDS output, with either of its higher memory options supporting this functionality. For context on potential issues, if both ends of an LVDS signal were directly connected to two input terminals on the NI 655X, each with a 50-ohm input impedance, the resulting circuit would be problematic. In this case, the driver's constant current source would attempt to push 3.5 mA through the positive wire. With a 50-ohm terminating resistor connected to ground, the voltage at the receiver would drop to 175 mV, significantly lower than the desired LVDS common-mode voltage of 1.2 V. The negative leg would be pulled to ground by the other 50-ohm resistor, resulting in a voltage of 0 V, which many LVDS drivers would interpret as an open fault.

The NI 655X is designed to facilitate the generation and analysis of LVDS signals effectively, leveraging its digital capabilities to interface with low voltage differential signaling technology. The ability to configure the output voltage levels and current appropriately is critical for ensuring reliable communication between devices. The integration of a 100-ohm terminating resistor at the receiver is essential for maintaining signal integrity, allowing for accurate voltage readings that align with LVDS specifications. Furthermore, the importance of maintaining proper impedance matching throughout the system cannot be overstated, as mismatched impedances can lead to signal reflections and degraded performance. The differential nature of LVDS allows for improved noise immunity and reduced electromagnetic interference, making it suitable for high-speed data transmission in various applications, including telecommunications and data acquisition systems. The NI 655X's flexibility in generating LVDS signals opens up a wide range of possibilities for engineers and designers looking to implement high-speed digital communication in their projects.The NI 655X is a versatile high-speed digital product that can interface to many different technologies. This application note shows how to interface the NI 655X to LVDS devices. Low Voltage Differential Signaling (LVDS) is an emerging differential digital standard used in several communication and mixed-signal applications.

The electrical charact eristics of an LVDS signal can facilitate significant performance improvements compared to single-ended standards. For example, since the received voltage is a differential between two signals, the voltage difference between the logic high level and low level state can be small, allowing for faster rise and fall times.

Another unique characteristic of LVDS is that it is a current-driven technology. Therefore, you must ensure your application has the correct termination and current-return paths. A current source at the driver provides approximately 3. 5 mA of current. The direction of the current across the transmission line depends on whether the driver is driving a logic high level or low level. When the current reaches the receiver, a 100 © terminating resistor connects the two ends of the transmission line to provide a return path for the current.

In addition, a voltage of approximately 350 mV is established across the two input terminals of the differential receiver. This differential voltage is either positive or negative, depending on the direction of the current. Based on the polarity of the voltage, the receiver recognizes the signal as either a high or low level.

As discussed in the introduction, LVDS is a differential, current-driven technology. The 655X, on the other hand, is a single-ended, voltage-driven digital waveform generator and analyzer. However, the flexibility of the 655X family of products allows you to easily interact with LVDS devices.

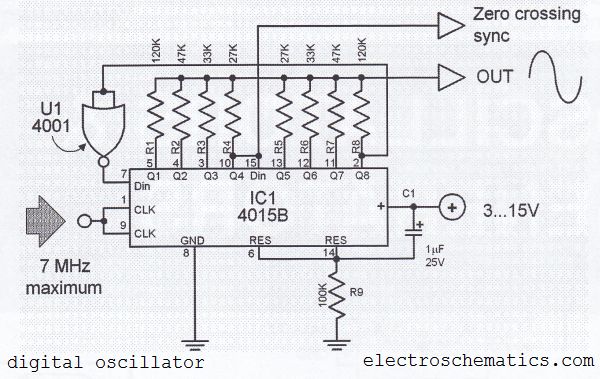

You can easily generate LVDS signals using two DIO channels to generate the two ends of the differential signal. The 655X devices have a 50 © source impedance on their output terminals that must be considered when configuring the voltage levels of a generation operation.

The NI 655X generation voltage levels must be set so that the appropriate current and voltage are seen at the receiver. Setting the generation voltage high level and generation voltage low level to 1. 7 V and 0. 7 V, respectively, works well. Those settings cause 5 mA to flow through the circuit, causing a voltage of 500 mV at the receiver (see Figure 3).

The LVDS specification allows for an input voltage range from 0 to 2. 4V, so a wide range of acceptable values are available. The common-mode voltage seen at the receiver in this case is 1. 2 V, which is within the ideal range for LVDS. Programming the 655X to perform this generation is similar to programming a regular single-ended operation. As shown in figure 4, two channels are configured for generation. After you set the clock rate, set the voltage levels to the appropriate values, and then the device downloads the waveform.

Notice that the data for the two channels are always inverse of one another. Another product, the NI 5421 is also capable of generating 16 channels of LVDS output. Either of the two higher memory options of the 5421 have this capability. See NI 5421 link at the bottom of this page for more information. For an example of what happens if the correct settings are not used, assume both ends of an LVDS signal were wired directly to two input terminals on the NI 655X, each with 50 © input impedance. The circuit would look like Figure 5. In this example, the driver`s constant current source attempts to push 3. 5 mA through the positive wire. With a 50 © terminating resistor to ground, the voltage at the receiver is 175 mV, well below the desired LVDS common-mode voltage of 1.

2 V. The negative leg is pulled to ground by the other 50 © resistor, forcing the voltage to be 0 V. Many LVDS drivers consider this to be an open-fault co 🔗 External reference

The NI 655X is designed to facilitate the generation and analysis of LVDS signals effectively, leveraging its digital capabilities to interface with low voltage differential signaling technology. The ability to configure the output voltage levels and current appropriately is critical for ensuring reliable communication between devices. The integration of a 100-ohm terminating resistor at the receiver is essential for maintaining signal integrity, allowing for accurate voltage readings that align with LVDS specifications. Furthermore, the importance of maintaining proper impedance matching throughout the system cannot be overstated, as mismatched impedances can lead to signal reflections and degraded performance. The differential nature of LVDS allows for improved noise immunity and reduced electromagnetic interference, making it suitable for high-speed data transmission in various applications, including telecommunications and data acquisition systems. The NI 655X's flexibility in generating LVDS signals opens up a wide range of possibilities for engineers and designers looking to implement high-speed digital communication in their projects.The NI 655X is a versatile high-speed digital product that can interface to many different technologies. This application note shows how to interface the NI 655X to LVDS devices. Low Voltage Differential Signaling (LVDS) is an emerging differential digital standard used in several communication and mixed-signal applications.

The electrical charact eristics of an LVDS signal can facilitate significant performance improvements compared to single-ended standards. For example, since the received voltage is a differential between two signals, the voltage difference between the logic high level and low level state can be small, allowing for faster rise and fall times.

Another unique characteristic of LVDS is that it is a current-driven technology. Therefore, you must ensure your application has the correct termination and current-return paths. A current source at the driver provides approximately 3. 5 mA of current. The direction of the current across the transmission line depends on whether the driver is driving a logic high level or low level. When the current reaches the receiver, a 100 © terminating resistor connects the two ends of the transmission line to provide a return path for the current.

In addition, a voltage of approximately 350 mV is established across the two input terminals of the differential receiver. This differential voltage is either positive or negative, depending on the direction of the current. Based on the polarity of the voltage, the receiver recognizes the signal as either a high or low level.

As discussed in the introduction, LVDS is a differential, current-driven technology. The 655X, on the other hand, is a single-ended, voltage-driven digital waveform generator and analyzer. However, the flexibility of the 655X family of products allows you to easily interact with LVDS devices.

You can easily generate LVDS signals using two DIO channels to generate the two ends of the differential signal. The 655X devices have a 50 © source impedance on their output terminals that must be considered when configuring the voltage levels of a generation operation.

The NI 655X generation voltage levels must be set so that the appropriate current and voltage are seen at the receiver. Setting the generation voltage high level and generation voltage low level to 1. 7 V and 0. 7 V, respectively, works well. Those settings cause 5 mA to flow through the circuit, causing a voltage of 500 mV at the receiver (see Figure 3).

The LVDS specification allows for an input voltage range from 0 to 2. 4V, so a wide range of acceptable values are available. The common-mode voltage seen at the receiver in this case is 1. 2 V, which is within the ideal range for LVDS. Programming the 655X to perform this generation is similar to programming a regular single-ended operation. As shown in figure 4, two channels are configured for generation. After you set the clock rate, set the voltage levels to the appropriate values, and then the device downloads the waveform.

Notice that the data for the two channels are always inverse of one another. Another product, the NI 5421 is also capable of generating 16 channels of LVDS output. Either of the two higher memory options of the 5421 have this capability. See NI 5421 link at the bottom of this page for more information. For an example of what happens if the correct settings are not used, assume both ends of an LVDS signal were wired directly to two input terminals on the NI 655X, each with 50 © input impedance. The circuit would look like Figure 5. In this example, the driver`s constant current source attempts to push 3. 5 mA through the positive wire. With a 50 © terminating resistor to ground, the voltage at the receiver is 175 mV, well below the desired LVDS common-mode voltage of 1.

2 V. The negative leg is pulled to ground by the other 50 © resistor, forcing the voltage to be 0 V. Many LVDS drivers consider this to be an open-fault co 🔗 External reference

%2Bwith%2Banimation%2Bsimulation%2Bcircuit.png)