Latching Ac Solid-State Relay

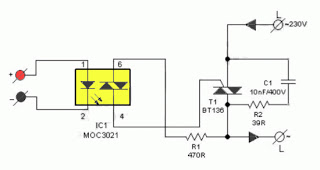

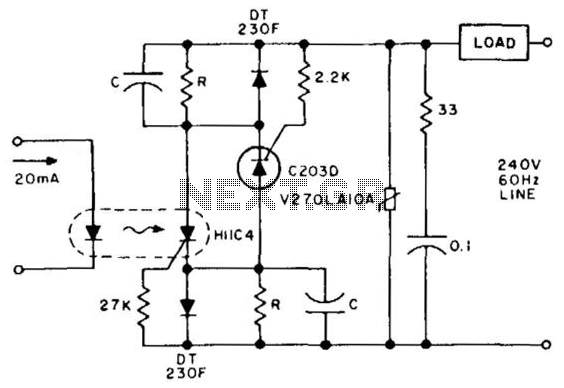

Latching is achieved by storing the gate trigger energy from the preceding half-cycle in capacitors. Power must be interrupted for more than one full cycle of the line to ensure turn-off. Resistor R and capacitor C are selected to minimize dissipation while ensuring the triggering of the respective SCRs for each cycle. A pulse of current, lasting over 10 ms into the H11C4 IRED, guarantees the triggering of the latching relay into conduction.

In this electronic circuit, the latching mechanism is established through the strategic use of capacitors that store energy from the gate trigger during the preceding half-cycle of the AC signal. This approach allows for the control of the power supply to a load by employing silicon-controlled rectifiers (SCRs) which require proper triggering to maintain conduction.

To effectively implement this design, the resistor (R) and capacitor (C) values must be carefully calculated to minimize energy dissipation while ensuring that the SCRs receive adequate triggering in each cycle of operation. The choice of these components directly influences the efficiency and responsiveness of the circuit.

The H11C4 optoisolator plays a crucial role in this configuration. By delivering a current pulse of over 10 ms into the infrared LED (IRED) within the optoisolator, it effectively triggers the latching relay. This relay, in turn, controls the power to the load. The timing of the current pulse is critical, as it must be sustained long enough to ensure reliable triggering of the relay while avoiding unnecessary power loss.

Overall, this circuit design emphasizes the importance of component selection and timing in achieving efficient latching control of power loads, ensuring that the system operates reliably under varying conditions. Latching is obtained by storing the gate trigger energy from the preceding half cycle in the capacitors. Powe r must be interrupted for more than one full cycle of the line to ensure turn-off. Resistor R and capacitor C are chosen to minimize dissipation, while assuring triggering of the respective SCRs for each cycle. A pulse of current, over 10 ms duration into the H11C4 IRED, ensures triggering the latching relay into conduction.

🔗 External reference

In this electronic circuit, the latching mechanism is established through the strategic use of capacitors that store energy from the gate trigger during the preceding half-cycle of the AC signal. This approach allows for the control of the power supply to a load by employing silicon-controlled rectifiers (SCRs) which require proper triggering to maintain conduction.

To effectively implement this design, the resistor (R) and capacitor (C) values must be carefully calculated to minimize energy dissipation while ensuring that the SCRs receive adequate triggering in each cycle of operation. The choice of these components directly influences the efficiency and responsiveness of the circuit.

The H11C4 optoisolator plays a crucial role in this configuration. By delivering a current pulse of over 10 ms into the infrared LED (IRED) within the optoisolator, it effectively triggers the latching relay. This relay, in turn, controls the power to the load. The timing of the current pulse is critical, as it must be sustained long enough to ensure reliable triggering of the relay while avoiding unnecessary power loss.

Overall, this circuit design emphasizes the importance of component selection and timing in achieving efficient latching control of power loads, ensuring that the system operates reliably under varying conditions. Latching is obtained by storing the gate trigger energy from the preceding half cycle in the capacitors. Powe r must be interrupted for more than one full cycle of the line to ensure turn-off. Resistor R and capacitor C are chosen to minimize dissipation, while assuring triggering of the respective SCRs for each cycle. A pulse of current, over 10 ms duration into the H11C4 IRED, ensures triggering the latching relay into conduction.

🔗 External reference