Microprocessor RS-232 Reset

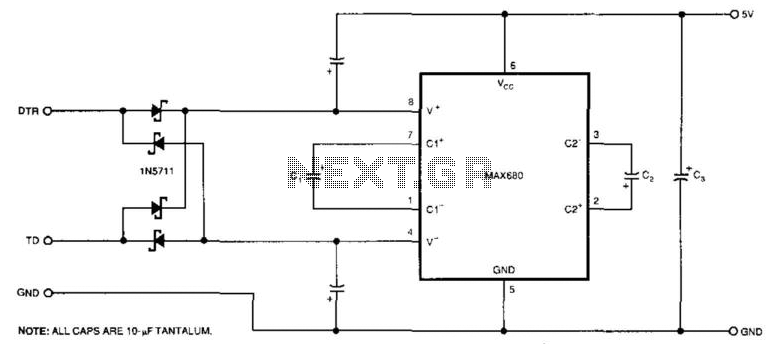

This circuit enables a remote microprocessor to be reset by a controlling host via a remote RS-232 or similar protocol serial line. Utilizing a program loader on the remote host, a program can be downloaded and executed. This functionality allows the target processor to run various code in RAM, eliminating the necessity of burning multiple EPROMs. The circuit is typically employed for code development on a target processor but can also be utilized for permanent applications where the target program resides on a host system's disk. A program loader for the Z80 CPU is available, and the circuit has also been implemented with the Motorola 68HC11 EVB and the BUFFALO monitor program. This circuit detects long-duration zero-level signals (breaks) on a non-return to zero (NRZ) serial data line. Standard serial characters remain in the zero state briefly and do not trigger a reset. However, break characters persist long enough to switch the output of the circuit. The 10K/1N4148 components maintain the charge of the 2.2uF capacitor. Low input signals pass through the 10K resistor, gradually discharging the 2.2uF capacitor. High input signals rapidly recharge the capacitor via the 1N4148 diode. A break signal discharges the 2.2uF capacitor sufficiently to change the state of the following gate. The 1N4148 diode on the right permits the use of a manual break switch on the target CPU, ensuring that pressing the switch does not short out the preceding 74HC14 gate. This circuit could be constructed with just two Schmidt trigger non-inverting buffers; the 74HC14 was selected due to its commonality. The parallel inverters are optional, as single inverters function adequately.

The circuit design facilitates seamless communication and control between a host and a target microprocessor, making it particularly useful in development environments and applications requiring dynamic code execution. The RS-232 interface provides a robust protocol for serial communication, ensuring reliable data transfer. The ability to download and execute programs remotely enhances flexibility and efficiency in code testing and deployment.

In terms of operation, the circuit's sensitivity to long-duration zero-level signals is critical for distinguishing between standard data transmission and reset commands. The use of a 2.2uF capacitor in conjunction with the 10K resistor and 1N4148 diode creates a timing mechanism that effectively differentiates between typical serial communication and intentional breaks. The choice of the 74HC14 as the primary logic gate allows for high-speed operation and noise immunity, which is essential in digital signal processing.

The inclusion of a manual break switch expands the functionality of the circuit, allowing for immediate resets without interfering with the circuit's normal operation. This feature is particularly beneficial during debugging sessions, where quick resets may be required to test different code iterations. The optional parallel inverters provide design flexibility, allowing engineers to tailor the circuit to specific application requirements while maintaining performance.

Overall, this circuit exemplifies an effective solution for remote microprocessor management, providing essential capabilities for both development and operational contexts. Its design can be adapted for various microcontroller architectures, ensuring broad applicability across different projects and applications.This circuit allows a remote microprocessor to be reset by a controlling host over a remote RS-232 or similar protocol serial line. With the use of a program loader on the remote host, a program may be downloaded and run. This allows a target processor to run different code in RAM, thus getting rid of the need to burn multiple EPROMs.

The circuit i s usually used for developing code on a target processor, but it can also be used for permanent applications where the target program lives on a host system`s disk. A program loader for the Z80 CPU is available below. The circuit has also been used with the Motorola 68HC11 EVB and the BUFFALO monitor program. See my Linux Cross Assemblers page for more info. This circuit detects long duration zero level signals (breaks) on a NRZ (non return to zero) serial data line.

Normal serial characters spend a short time in the zero state, and do not cause a reset. Break characters last long enough to cause the output of the circuit to switch. The 10K/1N4148 parts keep the 2. 2uF capacitor charged up. Low input signals go through the 10K resistor and slowly pull the charge on the 2. 2uF capacitor down. High input signals quickly recharge the capacitor through the 1N4148 diode. A break signal lasts long enough to discharge the 2. 2uF capacitor to the point where the following gate changes state. The 1N4148 on the right allows a manual break switch to be used on the target CPU, pressing such a switch does not short out the preceding 74HC14 gate. This circuit could be built with just 2 schmidt trigger non inverting buffers, the 74HC14 was chosen because it is a common part.

The parallel inverters are also optional, single inverters work fine. Be the first of your friends to get free diy electronics projects, circuits diagrams, hacks, mods, gadgets & gizmo automatically each time we publish. Your email address & privacy are safe with us ! 🔗 External reference

The circuit design facilitates seamless communication and control between a host and a target microprocessor, making it particularly useful in development environments and applications requiring dynamic code execution. The RS-232 interface provides a robust protocol for serial communication, ensuring reliable data transfer. The ability to download and execute programs remotely enhances flexibility and efficiency in code testing and deployment.

In terms of operation, the circuit's sensitivity to long-duration zero-level signals is critical for distinguishing between standard data transmission and reset commands. The use of a 2.2uF capacitor in conjunction with the 10K resistor and 1N4148 diode creates a timing mechanism that effectively differentiates between typical serial communication and intentional breaks. The choice of the 74HC14 as the primary logic gate allows for high-speed operation and noise immunity, which is essential in digital signal processing.

The inclusion of a manual break switch expands the functionality of the circuit, allowing for immediate resets without interfering with the circuit's normal operation. This feature is particularly beneficial during debugging sessions, where quick resets may be required to test different code iterations. The optional parallel inverters provide design flexibility, allowing engineers to tailor the circuit to specific application requirements while maintaining performance.

Overall, this circuit exemplifies an effective solution for remote microprocessor management, providing essential capabilities for both development and operational contexts. Its design can be adapted for various microcontroller architectures, ensuring broad applicability across different projects and applications.This circuit allows a remote microprocessor to be reset by a controlling host over a remote RS-232 or similar protocol serial line. With the use of a program loader on the remote host, a program may be downloaded and run. This allows a target processor to run different code in RAM, thus getting rid of the need to burn multiple EPROMs.

The circuit i s usually used for developing code on a target processor, but it can also be used for permanent applications where the target program lives on a host system`s disk. A program loader for the Z80 CPU is available below. The circuit has also been used with the Motorola 68HC11 EVB and the BUFFALO monitor program. See my Linux Cross Assemblers page for more info. This circuit detects long duration zero level signals (breaks) on a NRZ (non return to zero) serial data line.

Normal serial characters spend a short time in the zero state, and do not cause a reset. Break characters last long enough to cause the output of the circuit to switch. The 10K/1N4148 parts keep the 2. 2uF capacitor charged up. Low input signals go through the 10K resistor and slowly pull the charge on the 2. 2uF capacitor down. High input signals quickly recharge the capacitor through the 1N4148 diode. A break signal lasts long enough to discharge the 2. 2uF capacitor to the point where the following gate changes state. The 1N4148 on the right allows a manual break switch to be used on the target CPU, pressing such a switch does not short out the preceding 74HC14 gate. This circuit could be built with just 2 schmidt trigger non inverting buffers, the 74HC14 was chosen because it is a common part.

The parallel inverters are also optional, single inverters work fine. Be the first of your friends to get free diy electronics projects, circuits diagrams, hacks, mods, gadgets & gizmo automatically each time we publish. Your email address & privacy are safe with us ! 🔗 External reference