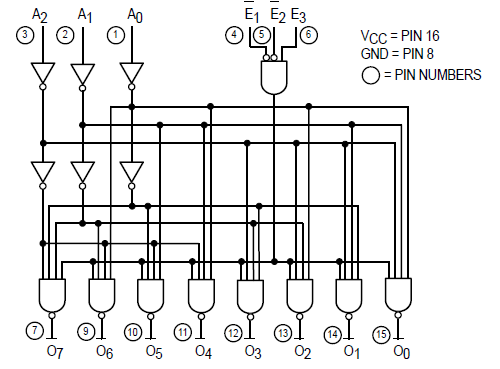

Motorola SN54 Demultiplexer Logic Diagram and Datasheet

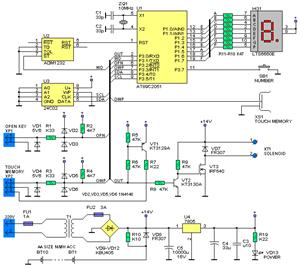

The Motorola SN54/74LS138 is recognized as a 1-of-8 decoder or demultiplexer, specifically engineered for high-speed bar memory chip select address decoding. The accompanying diagram illustrates the logic configuration of the SN54/74LS138 demultiplexer. According to the SN54 datasheet, the multiple enable function facilitates straightforward parallel expansion of the device to create a 1-of-32 decoder (using 5 input lines to decode to 32 output lines) with the integration of four LS138 devices and one inverter.

The Motorola SN54/74LS138 is a high-speed CMOS logic device that operates as a 1-of-8 line decoder/demultiplexer. This component features three binary select inputs (A0, A1, A2) that can decode a 3-bit binary number into one of eight active low outputs (Y0 to Y7). The device also includes three enable inputs (G1, G2A, G2B) which must be appropriately activated to allow the decoder to function. When the enable inputs are not activated, all outputs remain inactive regardless of the select input states.

The operational speed of the SN54/74LS138 makes it suitable for applications requiring rapid address decoding, such as in memory chip selection for microprocessors. The architecture of the device allows for cascading multiple SN54/74LS138 chips to expand the decoding capability. By connecting four of these devices along with a single inverter, one can achieve a 1-of-32 decoding scheme. This is accomplished by using five input lines to select one of the thirty-two outputs, effectively increasing the number of selectable outputs while maintaining the high-speed performance characteristic of the SN54/74LS138.

In practical applications, the multiple enable function enhances versatility in circuit design, allowing for complex configurations without significant additional components. The logic diagram of the SN54/74LS138 can be utilized to understand the internal workings of the device, including the AND gates and inverters used to produce the desired output based on the binary input. This makes the SN54/74LS138 a crucial component in digital systems requiring efficient address decoding and demultiplexing capabilities.Motorola SN54/74LS138 known to be 1-of-8 decoder or demultiplexer which is designed for high speed bar memory chip select address decoding. Below diagram illustrates logic diagram of this SN54/74LS138 demultiplexer. According to the SN54 datasheet, multiple enable function allows easy parallel expansion of the device to a 1-of-32 (5 lines to 32 li

nes) decoder with just four LS138s and one inverter. Diagram 🔗 External reference

The Motorola SN54/74LS138 is a high-speed CMOS logic device that operates as a 1-of-8 line decoder/demultiplexer. This component features three binary select inputs (A0, A1, A2) that can decode a 3-bit binary number into one of eight active low outputs (Y0 to Y7). The device also includes three enable inputs (G1, G2A, G2B) which must be appropriately activated to allow the decoder to function. When the enable inputs are not activated, all outputs remain inactive regardless of the select input states.

The operational speed of the SN54/74LS138 makes it suitable for applications requiring rapid address decoding, such as in memory chip selection for microprocessors. The architecture of the device allows for cascading multiple SN54/74LS138 chips to expand the decoding capability. By connecting four of these devices along with a single inverter, one can achieve a 1-of-32 decoding scheme. This is accomplished by using five input lines to select one of the thirty-two outputs, effectively increasing the number of selectable outputs while maintaining the high-speed performance characteristic of the SN54/74LS138.

In practical applications, the multiple enable function enhances versatility in circuit design, allowing for complex configurations without significant additional components. The logic diagram of the SN54/74LS138 can be utilized to understand the internal workings of the device, including the AND gates and inverters used to produce the desired output based on the binary input. This makes the SN54/74LS138 a crucial component in digital systems requiring efficient address decoding and demultiplexing capabilities.Motorola SN54/74LS138 known to be 1-of-8 decoder or demultiplexer which is designed for high speed bar memory chip select address decoding. Below diagram illustrates logic diagram of this SN54/74LS138 demultiplexer. According to the SN54 datasheet, multiple enable function allows easy parallel expansion of the device to a 1-of-32 (5 lines to 32 li

nes) decoder with just four LS138s and one inverter. Diagram 🔗 External reference