NAND gate S-R flip-flop

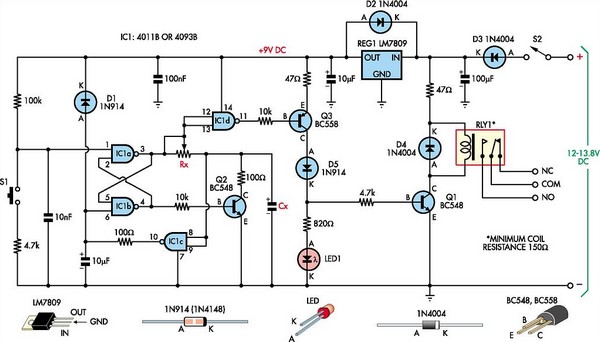

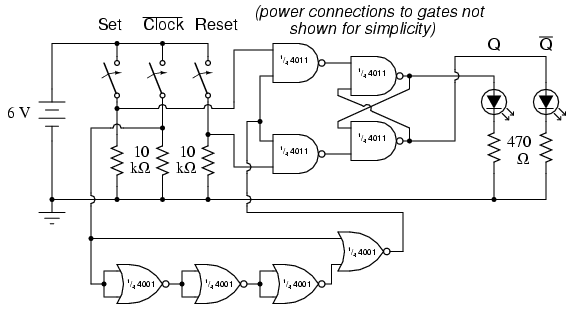

The parts list specifies a ten-segment LED unit, but the illustration depicts two individual LEDs instead. This change is due to limited space on the breadboard for the switch assembly, two integrated circuits, and the bar graph. If space permits, the bar graph can be utilized as indicated in the parts list, as shown in previous latch circuits. The distinction between a gated latch (or enabled latch) and a flip-flop is that a flip-flop is activated solely on the rising or falling edge of a clock signal, rather than for the entire duration of a high enable signal. To convert an enabled latch into a flip-flop, a pulse detector circuit must be added to the Enable input, allowing the edge of a clock pulse to generate a brief high Enable pulse. This effect is achieved using a single NOR gate and three inverter gates, which take advantage of the propagation delay time of multiple cascaded gates. In this setup, three NOR gates with paralleled inputs are employed to create three inverters, thus utilizing all four NOR gates of a 4001 integrated circuit. Typically, when configuring a NOR gate as an inverter, one input is grounded while the other serves as the inverter input to reduce input capacitance and enhance speed. However, in this case, a slower response is desired, so the NOR inputs are paralleled to form inverters instead of following the conventional approach. It is important to note that this pulse detector circuit generates a high output pulse at every falling edge of the clock input signal. Consequently, the flip-flop circuit should be responsive to the Set and Reset input states only when the middle switch transitions from "on" to "off," rather than from "off" to "on." During the construction of this circuit, it may be observed that the outputs respond to Set and Reset input signals during both transitions of the Clock input, not exclusively when it shifts from a high state to a low state. This behavior is attributed to contact bounce, which is the phenomenon of a mechanical switch rapidly making and breaking contact when its contacts are initially closed due to the elastic collision of the metal contact pads. Instead of producing a single, clean low-to-high signal transition upon closure, the Clock switch will likely exhibit several low-high-low cycles as the contact pads bounce during off-to-on actuation. The first high-to-low transition resulting from this bouncing will activate the pulse detector circuit, temporarily enabling the S-R latch and making it responsive to the Set and Reset inputs. Ideally, switches would operate perfectly and without bounce; however, in practical applications, contact bounce is a prevalent issue in digital gate circuits driven by switch inputs and must be thoroughly understood to be effectively addressed.

The circuit described involves a ten-segment LED display or two individual LEDs, which function as visual indicators for the output states of the flip-flop. The flip-flop is designed using a combination of NOR gates configured to create a pulse detector that converts a gated latch into a flip-flop. The pulse detector's role is crucial, as it ensures that the flip-flop responds correctly to clock signals by generating a brief high pulse at the falling edge of the clock, which allows for accurate transitions between Set and Reset states.

The use of a 4001 integrated circuit is significant, as it contains four NOR gates, which are versatile components in digital logic design. The intentional design choice to parallel the inputs of the NOR gates to create inverters is a deviation from standard practice, which typically emphasizes speed. In this scenario, the slower response time is leveraged to mitigate the effects of contact bounce, allowing for a more stable operation of the flip-flop circuit.

The circuit's response to the mechanical switch's bounce is a critical consideration in its design. The mechanical switch's inherent imperfections can lead to unintended triggering of the flip-flop, which necessitates careful attention in practical implementations. This understanding of contact bounce and its implications on circuit behavior is essential for engineers and designers working with digital systems. Proper debouncing techniques or circuitry may be employed to ensure that the flip-flop operates reliably, responding only to intended state changes rather than erratic signals caused by mechanical imperfections.Although the parts list calls for a ten-segment LED unit, the illustration shows two individual LEDs being used instead. This is due to lack of room on my breadboard to mount the switch assembly, two integrated circuits, and the bargraph.

If you have room on your breadboard, feel free to use the bargraph as called for in the parts list, and as sho wn in prior latch circuits. The only difference between a gated (or enabled) latch and a flip-flop is that a flip-flop is enabled only on the rising or falling edge of a "clock" signal, rather than for the entire duration of a "high" enable signal. Converting an enabled latch into a flip-flop simply requires that a "pulse detector" circuit be added to the Enable input, so that the edge of a clock pulse generates a brief "high" Enable pulse: The single NOR gate and three inverter gates create this effect by exploiting the propagation delay time of multiple, cascaded gates.

In this experiment, I use three NOR gates with paralleled inputs to create three inverters, thus using all four NOR gates of a 4001 integrated circuit: Normally, when using a NOR gate as an inverter, one input would be grounded while the other acts as the inverter input, to minimize input capacitance and increase speed. Here, however, slow response is desired, and so I parallel the NOR inputs to make inverters rather than use the more conventional method.

Please note that this particular pulse detector circuit produces a "high" output pulse at every falling edge of the clock (input) signal. This means that the flip-flop circuit should be responsive to the Set and Reset input states only when the middle switch is moved from "on" to "off, " not from "off" to "on.

" When you build this circuit, though, you may discover that the outputs respond to Set and Reset input signals during both transitions of the Clock input, not just when it is switched from a "high" state to a "low" state. The reason for this is contact bounce: the effect of a mechanical switch rapidly making-and-breaking when its contacts are first closed, due to the elastic collision of the metal contact pads.

Instead of the Clock switch producing a single, clean low-to-high signal transition when closed, there will most likely be several low-high-low "cycles" as the contact pads "bounce" upon off-to-on actuation. The first high-to-low transition caused by bouncing will trigger the pulse detector circuit, enabling the S-R latch for that moment in time, making it responsive to the Set and Reset inputs.

Ideally, of course, switches are perfect and bounce-free. In the real world, though, contact bounce is a very common problem for digital gate circuits operated by switch inputs, and must be understood well if it is to be overcome. 🔗 External reference

The circuit described involves a ten-segment LED display or two individual LEDs, which function as visual indicators for the output states of the flip-flop. The flip-flop is designed using a combination of NOR gates configured to create a pulse detector that converts a gated latch into a flip-flop. The pulse detector's role is crucial, as it ensures that the flip-flop responds correctly to clock signals by generating a brief high pulse at the falling edge of the clock, which allows for accurate transitions between Set and Reset states.

The use of a 4001 integrated circuit is significant, as it contains four NOR gates, which are versatile components in digital logic design. The intentional design choice to parallel the inputs of the NOR gates to create inverters is a deviation from standard practice, which typically emphasizes speed. In this scenario, the slower response time is leveraged to mitigate the effects of contact bounce, allowing for a more stable operation of the flip-flop circuit.

The circuit's response to the mechanical switch's bounce is a critical consideration in its design. The mechanical switch's inherent imperfections can lead to unintended triggering of the flip-flop, which necessitates careful attention in practical implementations. This understanding of contact bounce and its implications on circuit behavior is essential for engineers and designers working with digital systems. Proper debouncing techniques or circuitry may be employed to ensure that the flip-flop operates reliably, responding only to intended state changes rather than erratic signals caused by mechanical imperfections.Although the parts list calls for a ten-segment LED unit, the illustration shows two individual LEDs being used instead. This is due to lack of room on my breadboard to mount the switch assembly, two integrated circuits, and the bargraph.

If you have room on your breadboard, feel free to use the bargraph as called for in the parts list, and as sho wn in prior latch circuits. The only difference between a gated (or enabled) latch and a flip-flop is that a flip-flop is enabled only on the rising or falling edge of a "clock" signal, rather than for the entire duration of a "high" enable signal. Converting an enabled latch into a flip-flop simply requires that a "pulse detector" circuit be added to the Enable input, so that the edge of a clock pulse generates a brief "high" Enable pulse: The single NOR gate and three inverter gates create this effect by exploiting the propagation delay time of multiple, cascaded gates.

In this experiment, I use three NOR gates with paralleled inputs to create three inverters, thus using all four NOR gates of a 4001 integrated circuit: Normally, when using a NOR gate as an inverter, one input would be grounded while the other acts as the inverter input, to minimize input capacitance and increase speed. Here, however, slow response is desired, and so I parallel the NOR inputs to make inverters rather than use the more conventional method.

Please note that this particular pulse detector circuit produces a "high" output pulse at every falling edge of the clock (input) signal. This means that the flip-flop circuit should be responsive to the Set and Reset input states only when the middle switch is moved from "on" to "off, " not from "off" to "on.

" When you build this circuit, though, you may discover that the outputs respond to Set and Reset input signals during both transitions of the Clock input, not just when it is switched from a "high" state to a "low" state. The reason for this is contact bounce: the effect of a mechanical switch rapidly making-and-breaking when its contacts are first closed, due to the elastic collision of the metal contact pads.

Instead of the Clock switch producing a single, clean low-to-high signal transition when closed, there will most likely be several low-high-low "cycles" as the contact pads "bounce" upon off-to-on actuation. The first high-to-low transition caused by bouncing will trigger the pulse detector circuit, enabling the S-R latch for that moment in time, making it responsive to the Set and Reset inputs.

Ideally, of course, switches are perfect and bounce-free. In the real world, though, contact bounce is a very common problem for digital gate circuits operated by switch inputs, and must be understood well if it is to be overcome. 🔗 External reference