One KHz Synchronous Detector Circuit

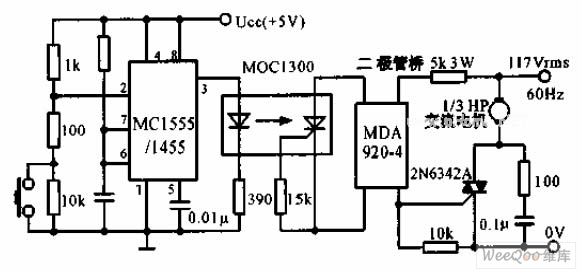

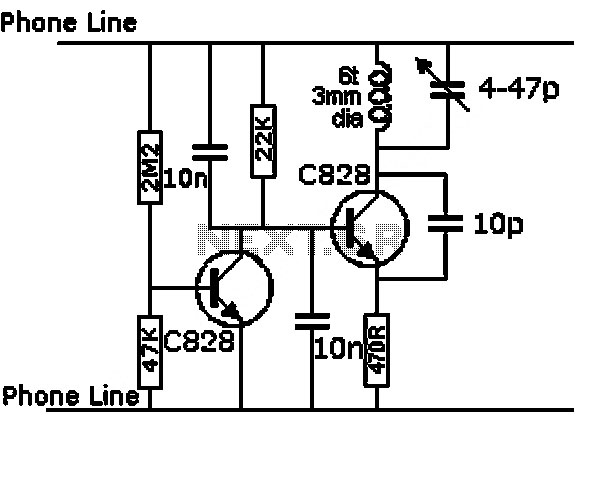

This circuit utilizes a synchronous demodulator to extract a 1 kHz signal from noise and measures its amplitude, with the 1 kHz signal providing a resolution of approximately 60 microvolts per count. The measurements are transmitted via an RS-232 interface for further processing or display. An LED on the board activates when the measured signal surpasses a predefined threshold. This project originated from an interest in capturing extremely low-frequency (ELF) wireless signals and has applications in optics, high-frequency RF, and any scenario where small signals, with recognized frequency and phase, need to be measured in the presence of noise. By incorporating a preamplifier based on the LM324, the circuit sensitivity was enhanced to 160 nanovolts per count. The LM324 is noted for its low noise output, which is beneficial for this type of detection. The incoming signal is buffered by U2A (part of U1, which is separated into a preamp assembly), providing a non-inverted signal to the integrator when U3A is activated. U2B inverts the buffered signal from U2A and sends an inverted version to the integrator when U3B is activated. To increase the charging rate, the 100k resistor at the input of U2C can be reduced, or the 0.047 µF integrating capacitor can be decreased. The signals input to the integrator charge the 0.047 µF capacitor. After 999 cycles of the 1 kHz sampling signal, U3C activates, discharging the capacitor with a constant current (1.8V/7.5K = 240 microamps), generating a linear positive-going ramp at 5.106 volts/second on the output of U2C. While the output of U2 is ramping towards the 1.8-volt reference, the AT90S2313 microcontroller increments a counter every 1.25 microseconds until the comparator on the AT90S2313 changes state, indicating that the ramp on U2C has reached the 1.8-volt reference voltage. The maximum count for this measurement is 127, ensuring that the measurement time remains under the 250 microsecond interrupt interval. Consequently, a 7-bit measurement is completed in 160 microseconds or less, fitting within one 250 microsecond interrupt interval. The discharge rate of the integrating capacitor during the measurement phase is determined by the current into the node (1.8 volts/7.5 kΩ = 240 microamps) divided by the 0.047 µF capacitance, resulting in a voltage ramp of 5100 volts/second. The A/D conversion sensitivity is thus calculated as 1.25 µs/count multiplied by 5100 volts/second, yielding 6.375 millivolts per count. After the counting process concludes, which occurs when the pseudo 7-bit counter overflows or the ramp reaches the 1.8-volt reference, U3C is deactivated, and U3D is activated to clamp the integrator to the 1.8-volt reference, ensuring the capacitor is discharged to a stable state for one millisecond before commencing the next signal measurement. The entire measurement cycle lasts for 999 milliseconds for integration plus one millisecond for clamping the capacitor to zero, totaling one second per measurement. The gain in the integrator is calculated as (Peak input Voltage / 100 kΩ) × 0.999 seconds / 0.047 microfarads = 212.5 volts out per volt in. Therefore, the sensitivity of the detector is 6.375 mV / 212.5 = 30 microvolts peak per count, which translates to 60 microvolts peak-to-peak per count. Once the measurement is finalized, the measured value is formatted into Binary-Coded Decimal (BCD) and transmitted via the UART at 9600 baud, with two stop bits and no parity. Data transmission does not occur during interrupt time. An LED is activated by the microcontroller during the integration and measurement cycle if the measured value exceeds 64 in decimal.

This circuit design is particularly effective in environments with significant noise, allowing for precise measurement of small signals. The use of a synchronous demodulator enhances the ability to distinguish the desired signal from background noise, making it suitable for applications in various fields, including telecommunications, scientific research, and industrial monitoring. The integration of the AT90S2313 microcontroller allows for efficient processing and data handling, ensuring that the system operates seamlessly while maintaining high sensitivity and accuracy.This circuit employs a synchronous demodulator to separate a 1 KHz signal from noise and measures the amplitude with the 1 kHz signals when a 2nd at about 60 microvolts per count then sends the measurements via an RS-232 interface for further processing or exhibit. An LED about the board also lights when the measured signal exceeds a preset thresh old. This experiment was began when I took an interest in getting ELF wireless signals. It also has applictions in optics and superior frequency RF, or for that matter, any place one wants to measure a small signal, of which the frequency and phase are recognized, in the presence of noise. Using the addition of the preamplifier according to the LM324, the sensitivity of this circuit was very easily extended to a sensitivity to 160 nanovolts per count.

That an LM324 is utilized with little within the way of noise about the output testifies to the worth of employing this type of detector. The incoming signal is buffered by U2A (there is on U1 with this schematic as U1 was moved to a separate preamp assembly), which delivers a noniverted signal towards the integrator when U3A is switched on.

U2B inverts the buffered signal from U2A and offers an inverted edition of the signal towards the integrator when U3B is switched on. To increase the charging fee, possibly reduce the 100k resistor around the input of U2C or decrease the.

047 uf integrating capacitor. The signals fed into the integrator charge the. 047 uf capacitor within the integrator. Right after 999 cycles with the 1 kHz sampling signal, U3C is turned on plus the capacitor is discharged with a continual current (one. 8V/7. 5K = 240 microamps), creating a linear positive-going ramp at five, 106 volts/second on the output of U2C.

Though the output of U2 is ramping up toward the one. eight volt reference, the AT90S2313 sits inside a loop, incrementing a counter each and every 1. 25 microseconds, until the comparitor around the AT90S2313 modifications state, indicating that the ramp on U2C has reached the one. 8 volt reference voltage. The optimum count for this measurement is 127 to restrict the time invested in the measurement to less than the 250 microsecond interrupt interval.

Therefore, a 7 bit measurement is created in 160 microseconds or much less, and it is finished within a single 250 microsecond interrupt interval. The charge of discharge in the integrating capacitor throughout the measurement phase is set through the present in to the node, 1.

eight volts/7. five k =240 microamps, divided by the. 047 uf capacitance, which offers a 5100 volt/second voltage ramp. The A/D conversion sensitivity is therefore 1. 25 us/count X 5100 volts/second = 6. 375 millivolts per count. Immediately after the count is completed, which happens when the pseudo 7 bit counter overflows or even the ramp reaches the 1. 8 volt reference, U3C is switched off and U3D is switched on to clamp the of your integrator to the one.

eight volt reference and to make sure the capacitor is discharged to a consistent state for one millisecond before beginning signal measurement once more, The entire measurement cycle requires 999 milliseconds for integration + one millisecond to clamp the capacitor to zero, for a total of one second per measurement. The gian in the integrator is ( ( Peak input Voltage/ a hundred k Ohm) X 0. 999 seconds ) )/. 047 microfarads = 212. 5 volts out/volt in. The sensitivity of your detector is for that reason six. 375 mv/212. 5 = thirty microvolts peak per count, or because peak-to-peak = 2 x peak, 60 microvolts peak-to-peak per count.

Immediately after the measurement is completed, the measured worth is formatted into BCD and sent through the UART at 9600 baud, two stop bits, no parity. The transmission with the data does not happen during interrupt time. An LED is turned on by the microcontroller in the course of the integration and measurement cycle following a measurement during which the measured worth exceeded 64 decimal.

🔗 External reference

This circuit design is particularly effective in environments with significant noise, allowing for precise measurement of small signals. The use of a synchronous demodulator enhances the ability to distinguish the desired signal from background noise, making it suitable for applications in various fields, including telecommunications, scientific research, and industrial monitoring. The integration of the AT90S2313 microcontroller allows for efficient processing and data handling, ensuring that the system operates seamlessly while maintaining high sensitivity and accuracy.This circuit employs a synchronous demodulator to separate a 1 KHz signal from noise and measures the amplitude with the 1 kHz signals when a 2nd at about 60 microvolts per count then sends the measurements via an RS-232 interface for further processing or exhibit. An LED about the board also lights when the measured signal exceeds a preset thresh old. This experiment was began when I took an interest in getting ELF wireless signals. It also has applictions in optics and superior frequency RF, or for that matter, any place one wants to measure a small signal, of which the frequency and phase are recognized, in the presence of noise. Using the addition of the preamplifier according to the LM324, the sensitivity of this circuit was very easily extended to a sensitivity to 160 nanovolts per count.

That an LM324 is utilized with little within the way of noise about the output testifies to the worth of employing this type of detector. The incoming signal is buffered by U2A (there is on U1 with this schematic as U1 was moved to a separate preamp assembly), which delivers a noniverted signal towards the integrator when U3A is switched on.

U2B inverts the buffered signal from U2A and offers an inverted edition of the signal towards the integrator when U3B is switched on. To increase the charging fee, possibly reduce the 100k resistor around the input of U2C or decrease the.

047 uf integrating capacitor. The signals fed into the integrator charge the. 047 uf capacitor within the integrator. Right after 999 cycles with the 1 kHz sampling signal, U3C is turned on plus the capacitor is discharged with a continual current (one. 8V/7. 5K = 240 microamps), creating a linear positive-going ramp at five, 106 volts/second on the output of U2C.

Though the output of U2 is ramping up toward the one. eight volt reference, the AT90S2313 sits inside a loop, incrementing a counter each and every 1. 25 microseconds, until the comparitor around the AT90S2313 modifications state, indicating that the ramp on U2C has reached the one. 8 volt reference voltage. The optimum count for this measurement is 127 to restrict the time invested in the measurement to less than the 250 microsecond interrupt interval.

Therefore, a 7 bit measurement is created in 160 microseconds or much less, and it is finished within a single 250 microsecond interrupt interval. The charge of discharge in the integrating capacitor throughout the measurement phase is set through the present in to the node, 1.

eight volts/7. five k =240 microamps, divided by the. 047 uf capacitance, which offers a 5100 volt/second voltage ramp. The A/D conversion sensitivity is therefore 1. 25 us/count X 5100 volts/second = 6. 375 millivolts per count. Immediately after the count is completed, which happens when the pseudo 7 bit counter overflows or even the ramp reaches the 1. 8 volt reference, U3C is switched off and U3D is switched on to clamp the of your integrator to the one.

eight volt reference and to make sure the capacitor is discharged to a consistent state for one millisecond before beginning signal measurement once more, The entire measurement cycle requires 999 milliseconds for integration + one millisecond to clamp the capacitor to zero, for a total of one second per measurement. The gian in the integrator is ( ( Peak input Voltage/ a hundred k Ohm) X 0. 999 seconds ) )/. 047 microfarads = 212. 5 volts out/volt in. The sensitivity of your detector is for that reason six. 375 mv/212. 5 = thirty microvolts peak per count, or because peak-to-peak = 2 x peak, 60 microvolts peak-to-peak per count.

Immediately after the measurement is completed, the measured worth is formatted into BCD and sent through the UART at 9600 baud, two stop bits, no parity. The transmission with the data does not happen during interrupt time. An LED is turned on by the microcontroller in the course of the integration and measurement cycle following a measurement during which the measured worth exceeded 64 decimal.

🔗 External reference