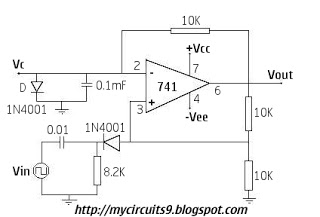

OP AMP BASED MONOSTABLE MULTIVIBRATOR 741

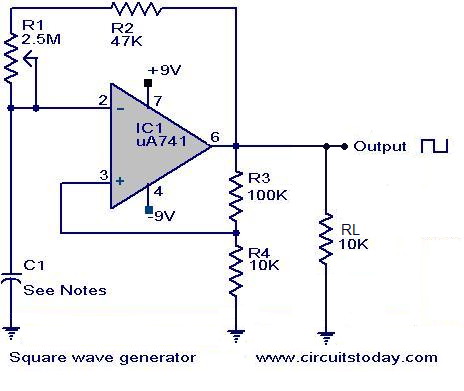

The circuit remains in a stable state until a triggering signal is applied to its input. Upon receiving the triggering signal, the output transitions from a stable state to a quasi-stable state and returns after a specified time period, generating a single pulse for each trigger. At the moment when the output voltage (Vo) reaches +Vsat, diode D1 dampens the capacitor voltage (Vc) to 0.7V. Additionally, the feedback voltage at the non-inverting terminal is +2Vsat. When a negative trigger is applied, the potential at the non-inverting terminal drops below 0.7V, causing the output to switch to -Vsat, which makes the diode more negative than -2Vsat. The comparator then switches back to +Vsat. Capacitor C begins to charge to +Vsat through resistor R until Vc reaches 0.7V, at which point the capacitor is damped to 0.7V.

This circuit operates as a monostable multivibrator, which is designed to produce a single output pulse in response to an input trigger. The initial stable state is maintained until a triggering event occurs, which can be a voltage pulse applied to the input. The transition to the quasi-stable state is characterized by the output voltage changing from its stable high state (+Vsat) to a low state (-Vsat) upon receiving a negative trigger.

The function of diode D1 is critical in this configuration, as it clamps the voltage across the capacitor (Vc) to a predetermined level of 0.7V, ensuring that the capacitor does not charge beyond this voltage during the pulse generation process. The feedback voltage of +2Vsat at the non-inverting terminal ensures that the comparator remains in a high state until the triggering condition is met.

When the negative trigger is applied, the potential at the non-inverting terminal drops below the threshold of 0.7V, leading to a rapid switch in the output to -Vsat. This change in output state causes the diode to become more negatively biased than -2Vsat, which effectively turns off the feedback to the non-inverting terminal. As a result, the comparator resets and switches back to +Vsat, initiating the charging cycle of capacitor C.

The charging of capacitor C through resistor R is a crucial part of the timing mechanism of this circuit. The time it takes for the capacitor to charge to 0.7V is determined by the RC time constant, which is a product of the resistance (R) and capacitance (C) values. Once Vc reaches 0.7V, the circuit returns to its stable state, completing the pulse cycle. This design allows for precise control of pulse width and timing, making it suitable for various applications in digital electronics and signal processing.The circuit remains in stable state until a triggering signal is applied to its input. After getting the triggering signal the output transit from stable to Quasi-stable state and return back after a time period. So a Single Pulse isgenerated for single Trigger. Consider the instant at which the output Vo=+Vsat. At that time diode D1 damps the Capacitor voltage, Vc at 0. 7V. Feedback voltage is + ²Vsat at Non-Inverting terminal. When the negative trigger is applied, the potential at Non-Inverting terminal becomes less than 0. 7v the output switches to -Vsat, which makes the diode more negative than - ²Vsat. Comparator switches back to +Vsat. The Capacitor C starts charging to +Vsat through R until Vc reaches 0. 7v and C becomes damped to 0. 7v. 🔗 External reference

This circuit operates as a monostable multivibrator, which is designed to produce a single output pulse in response to an input trigger. The initial stable state is maintained until a triggering event occurs, which can be a voltage pulse applied to the input. The transition to the quasi-stable state is characterized by the output voltage changing from its stable high state (+Vsat) to a low state (-Vsat) upon receiving a negative trigger.

The function of diode D1 is critical in this configuration, as it clamps the voltage across the capacitor (Vc) to a predetermined level of 0.7V, ensuring that the capacitor does not charge beyond this voltage during the pulse generation process. The feedback voltage of +2Vsat at the non-inverting terminal ensures that the comparator remains in a high state until the triggering condition is met.

When the negative trigger is applied, the potential at the non-inverting terminal drops below the threshold of 0.7V, leading to a rapid switch in the output to -Vsat. This change in output state causes the diode to become more negatively biased than -2Vsat, which effectively turns off the feedback to the non-inverting terminal. As a result, the comparator resets and switches back to +Vsat, initiating the charging cycle of capacitor C.

The charging of capacitor C through resistor R is a crucial part of the timing mechanism of this circuit. The time it takes for the capacitor to charge to 0.7V is determined by the RC time constant, which is a product of the resistance (R) and capacitance (C) values. Once Vc reaches 0.7V, the circuit returns to its stable state, completing the pulse cycle. This design allows for precise control of pulse width and timing, making it suitable for various applications in digital electronics and signal processing.The circuit remains in stable state until a triggering signal is applied to its input. After getting the triggering signal the output transit from stable to Quasi-stable state and return back after a time period. So a Single Pulse isgenerated for single Trigger. Consider the instant at which the output Vo=+Vsat. At that time diode D1 damps the Capacitor voltage, Vc at 0. 7V. Feedback voltage is + ²Vsat at Non-Inverting terminal. When the negative trigger is applied, the potential at Non-Inverting terminal becomes less than 0. 7v the output switches to -Vsat, which makes the diode more negative than - ²Vsat. Comparator switches back to +Vsat. The Capacitor C starts charging to +Vsat through R until Vc reaches 0. 7v and C becomes damped to 0. 7v. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713