Power Factor Correction (PFC) Circuit Reduces MOSFET Miller Effect

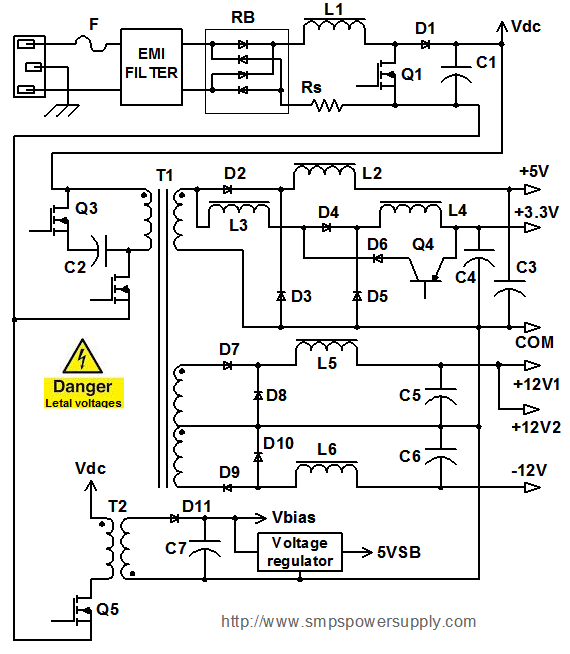

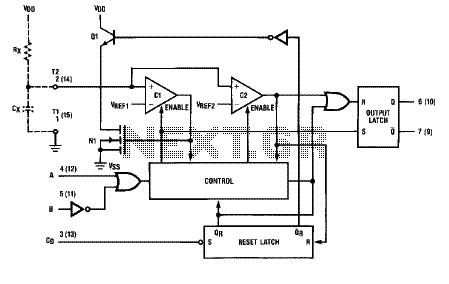

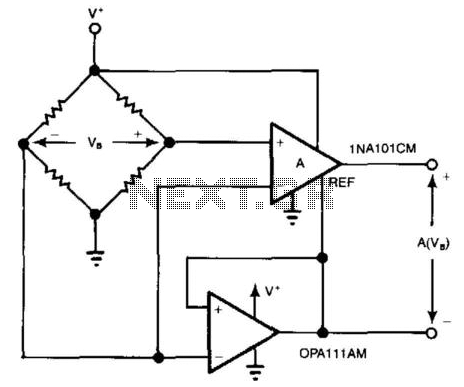

Adding a discharge path to the upper MOSFET of a cascode circuit significantly reduces the unavoidable Miller effect, thereby enhancing the Power Factor Correction (PFC) performance of a power supply's front end.

In a cascode configuration, the upper MOSFET is typically subject to the Miller effect, which can lead to increased switching losses and reduced efficiency. By incorporating a discharge path for the upper MOSFET, the gate capacitance can be effectively managed. This modification allows for faster turn-off times and mitigates the impact of voltage transients, which are particularly pronounced due to the Miller capacitance.

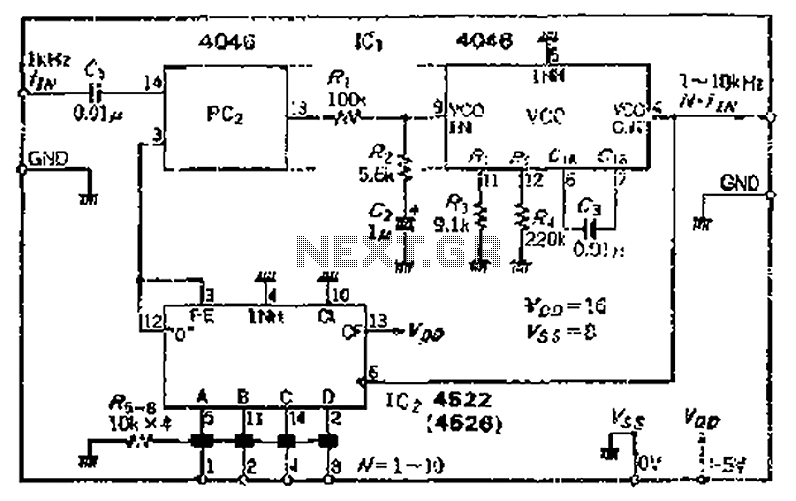

The discharge path can be implemented using a resistor or an additional transistor that provides a controlled discharge route for the gate capacitance when the MOSFET is turned off. This approach ensures that the gate voltage is lowered more quickly, thereby reducing the time the MOSFET remains in the linear region during switching transitions. As a result, the overall switching losses are minimized, which is crucial for applications requiring high efficiency, such as in power supply designs focused on PFC.

Furthermore, improving the PFC performance not only enhances the efficiency of the power supply but also helps in meeting regulatory standards for harmonic distortion and energy consumption. This modification can lead to a more robust design that is capable of handling varying load conditions while maintaining optimal performance. The integration of a discharge path into the upper MOSFET of a cascode circuit exemplifies an effective strategy for advancing the operational characteristics of modern power electronics.By adding a discharge path to the upper MOSFET of a cascode circuit, the unavoidable Miller effect is greatly reduced and the PFC performance of a power supply`s front end can be improved 🔗 External reference

In a cascode configuration, the upper MOSFET is typically subject to the Miller effect, which can lead to increased switching losses and reduced efficiency. By incorporating a discharge path for the upper MOSFET, the gate capacitance can be effectively managed. This modification allows for faster turn-off times and mitigates the impact of voltage transients, which are particularly pronounced due to the Miller capacitance.

The discharge path can be implemented using a resistor or an additional transistor that provides a controlled discharge route for the gate capacitance when the MOSFET is turned off. This approach ensures that the gate voltage is lowered more quickly, thereby reducing the time the MOSFET remains in the linear region during switching transitions. As a result, the overall switching losses are minimized, which is crucial for applications requiring high efficiency, such as in power supply designs focused on PFC.

Furthermore, improving the PFC performance not only enhances the efficiency of the power supply but also helps in meeting regulatory standards for harmonic distortion and energy consumption. This modification can lead to a more robust design that is capable of handling varying load conditions while maintaining optimal performance. The integration of a discharge path into the upper MOSFET of a cascode circuit exemplifies an effective strategy for advancing the operational characteristics of modern power electronics.By adding a discharge path to the upper MOSFET of a cascode circuit, the unavoidable Miller effect is greatly reduced and the PFC performance of a power supply`s front end can be improved 🔗 External reference