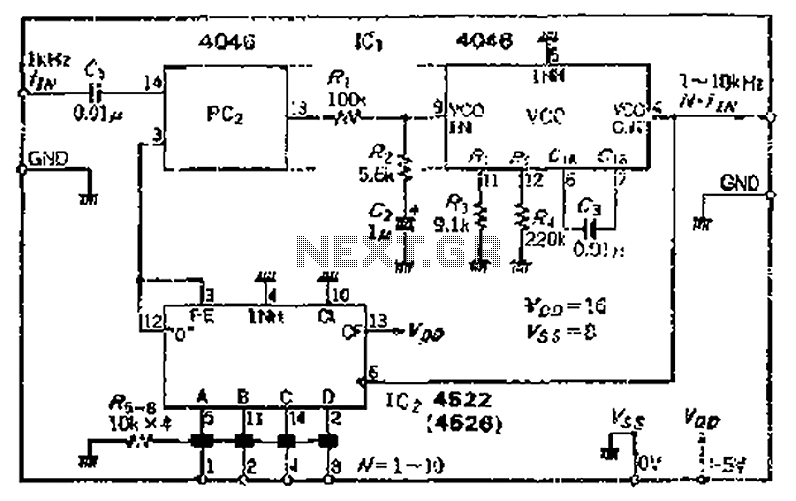

Using PLL Phase Locked Loop IC frequency N 1 to 10 of the multiplier circuit

The CMOS IC 4046 Phase-Locked Loop (PLL) operates with a maximum frequency of 1 MHz. It is connected to a programmable divider, allowing it to process input frequencies. As the frequency increases by a factor of t, the circuit's functionality is adjusted. The phase comparator PC2 checks if phase t is equal to the output frequency of the frequency divider circuit. It then outputs a voltage signal (vP-P) through the loop filter, which consists of resistors R1 and R2, and capacitor C, after filtering the voltage-controlled oscillator (VCO) frequency. The variable range of the VCO spans from the input frequency (fiv) to N times the output frequency (ffw). Consideration of circuit errors and long-term stability is essential to enhance the safety margin.

The CMOS 4046 PLL is a versatile integrated circuit designed for frequency synthesis and demodulation applications. The primary components of the 4046 include a phase comparator, a voltage-controlled oscillator (VCO), and a programmable frequency divider. The phase comparator can operate in two modes, PC1 and PC2, which allow for different applications depending on the desired output characteristics.

In operation, the VCO generates an output frequency that is adjustable based on the input control voltage. The programmable divider allows for the division of the VCO output frequency, enabling the PLL to lock onto a specific frequency ratio. The phase comparator continuously monitors the phase difference between the divided output frequency and the reference input frequency. When a phase discrepancy is detected, the phase comparator generates an error signal that is filtered by the loop filter (consisting of resistors and capacitors) to smooth out the control voltage applied to the VCO.

The loop filter's design is crucial for the stability and performance of the PLL. It determines the response time and bandwidth of the system, affecting how quickly the PLL can lock onto a new frequency. The choice of resistor and capacitor values in the loop filter must be carefully calculated to achieve the desired transient response and steady-state performance.

The VCO's frequency range is defined by the input voltage, which can be adjusted to cover a wide range of frequencies, making the 4046 suitable for various applications, including frequency modulation, demodulation, and clock recovery in communication systems.

Additionally, attention must be given to potential circuit errors that can arise from component tolerances, noise, and temperature variations. Implementing design strategies to mitigate these issues, such as using precision components and providing adequate thermal management, can significantly improve the long-term stability and reliability of the PLL circuit. C- MOSIC4046 PLL having the main function of a maximum operating frequency of iMHz integrated circuit, which is connected to the programmable divider, can constitute the input frequency increases t times the circuit. Phase comparator PC2 check, t phase 1 is equal to the frequency of the output of the frequency divider circuit and t which outputs ) ~ vP-P signal via the loop filter (roar -R2, G soap) after filtering vco oscillation frequency control. vco variable range of jf a field -f, In is from the input frequency fiv to N- ffw. Consider Journal circuit errors and long-term stability, actually increase the number of safety margin.

The CMOS 4046 PLL is a versatile integrated circuit designed for frequency synthesis and demodulation applications. The primary components of the 4046 include a phase comparator, a voltage-controlled oscillator (VCO), and a programmable frequency divider. The phase comparator can operate in two modes, PC1 and PC2, which allow for different applications depending on the desired output characteristics.

In operation, the VCO generates an output frequency that is adjustable based on the input control voltage. The programmable divider allows for the division of the VCO output frequency, enabling the PLL to lock onto a specific frequency ratio. The phase comparator continuously monitors the phase difference between the divided output frequency and the reference input frequency. When a phase discrepancy is detected, the phase comparator generates an error signal that is filtered by the loop filter (consisting of resistors and capacitors) to smooth out the control voltage applied to the VCO.

The loop filter's design is crucial for the stability and performance of the PLL. It determines the response time and bandwidth of the system, affecting how quickly the PLL can lock onto a new frequency. The choice of resistor and capacitor values in the loop filter must be carefully calculated to achieve the desired transient response and steady-state performance.

The VCO's frequency range is defined by the input voltage, which can be adjusted to cover a wide range of frequencies, making the 4046 suitable for various applications, including frequency modulation, demodulation, and clock recovery in communication systems.

Additionally, attention must be given to potential circuit errors that can arise from component tolerances, noise, and temperature variations. Implementing design strategies to mitigate these issues, such as using precision components and providing adequate thermal management, can significantly improve the long-term stability and reliability of the PLL circuit. C- MOSIC4046 PLL having the main function of a maximum operating frequency of iMHz integrated circuit, which is connected to the programmable divider, can constitute the input frequency increases t times the circuit. Phase comparator PC2 check, t phase 1 is equal to the frequency of the output of the frequency divider circuit and t which outputs ) ~ vP-P signal via the loop filter (roar -R2, G soap) after filtering vco oscillation frequency control. vco variable range of jf a field -f, In is from the input frequency fiv to N- ffw. Consider Journal circuit errors and long-term stability, actually increase the number of safety margin.

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713