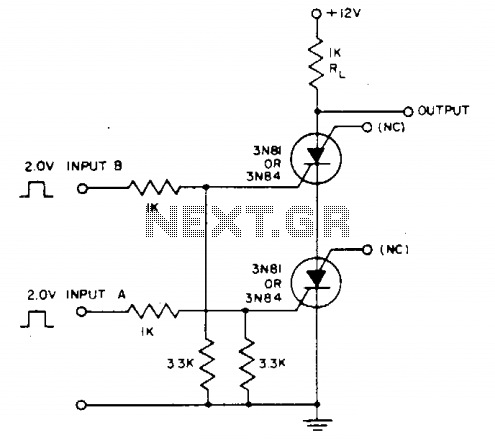

Pulse coincidence detector

Voltage across resistor Rl is only present when inputs A and (2- to 3-V amplitude) occur simultaneously. A brief overlap of less than 1 microsecond is enough to trigger the silicon-controlled switch (SCS). Coincidence of negative inputs is detected using gates G^ instead of Gc by utilizing the SCS in a complementary silicon-controlled rectifier (SCR) configuration.

The described circuit operates on the principle of detecting simultaneous input signals to control the output across a resistor. The primary component, a silicon-controlled switch (SCS), is a four-layer semiconductor device that can be turned on and off by applying appropriate gate signals. In this configuration, the SCS is used to manage the flow of current through resistor Rl based on the coincidence of two distinct input signals.

When input A and a secondary input with an amplitude of 2 to 3 volts are applied simultaneously, a voltage is developed across Rl. The critical aspect of this design is the timing; the overlap of the two inputs must be less than 1 microsecond to ensure reliable triggering of the SCS. This rapid response time is essential for applications requiring fast switching.

Additionally, the circuit employs gates G^ to detect the coincidence of negative inputs, which is a modification from the use of gates Gc. This adaptation allows for enhanced performance in specific applications where negative signal detection is crucial. The complementary SCR configuration of the SCS provides flexibility and improved control over the output, allowing for greater efficiency in managing the current flow through the circuit.

Overall, this circuit design effectively leverages the properties of the SCS and logic gates to achieve precise control of voltage across Rl, making it suitable for various electronic applications that require rapid response to input conditions.Unless inputs A and (2- to 3-V amplitude) occur simultaneously no voltage exists across Rl. Less than 1 microsecond overlap is sufficient to trigger the scs. Coincidence of negative inputs is detected with gates G^ instead of Gc by using the scs in a complementary SCR configuration. 🔗 External reference

The described circuit operates on the principle of detecting simultaneous input signals to control the output across a resistor. The primary component, a silicon-controlled switch (SCS), is a four-layer semiconductor device that can be turned on and off by applying appropriate gate signals. In this configuration, the SCS is used to manage the flow of current through resistor Rl based on the coincidence of two distinct input signals.

When input A and a secondary input with an amplitude of 2 to 3 volts are applied simultaneously, a voltage is developed across Rl. The critical aspect of this design is the timing; the overlap of the two inputs must be less than 1 microsecond to ensure reliable triggering of the SCS. This rapid response time is essential for applications requiring fast switching.

Additionally, the circuit employs gates G^ to detect the coincidence of negative inputs, which is a modification from the use of gates Gc. This adaptation allows for enhanced performance in specific applications where negative signal detection is crucial. The complementary SCR configuration of the SCS provides flexibility and improved control over the output, allowing for greater efficiency in managing the current flow through the circuit.

Overall, this circuit design effectively leverages the properties of the SCS and logic gates to achieve precise control of voltage across Rl, making it suitable for various electronic applications that require rapid response to input conditions.Unless inputs A and (2- to 3-V amplitude) occur simultaneously no voltage exists across Rl. Less than 1 microsecond overlap is sufficient to trigger the scs. Coincidence of negative inputs is detected with gates G^ instead of Gc by using the scs in a complementary SCR configuration. 🔗 External reference