Sample-and-hold

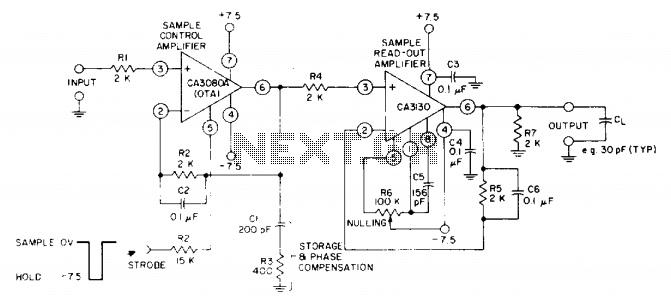

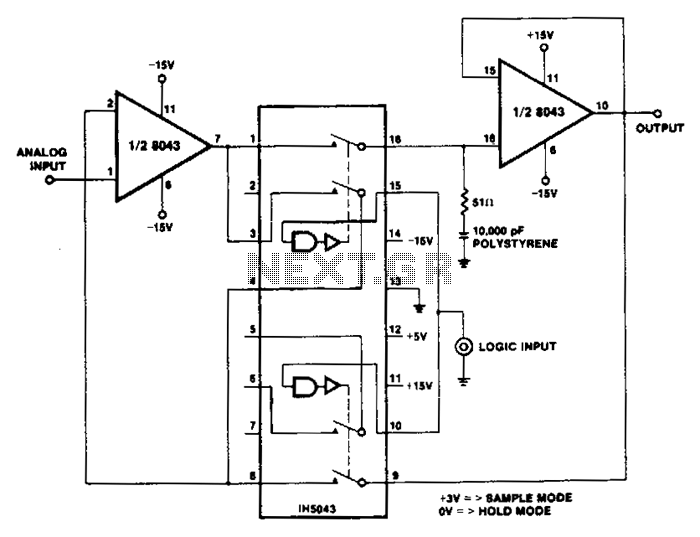

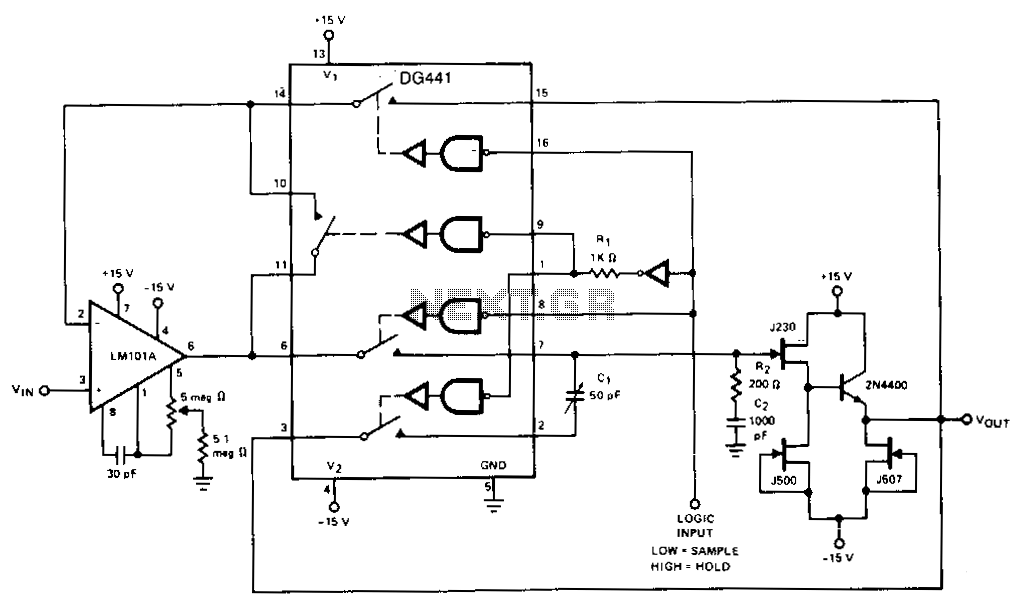

The LM101A provides gain and buffers the input from storage capacitor C2. R2 adds a zero in the open loop response to compensate for the pole caused by the switch resistance and C2, improving the closed-loop stability. R1 provides a slight delay in the digital drive to pins 1 and 9. C1 provides cancellation of coupled charge, keeping the sample-and-hold offset below 5 mV over the analog signal range of -10 through +10 V. Aperture time is typically 1 ps, the switching time of the DG441. Acquisition time is 25 ps, but this can be improved by using a faster slewing operational amplifier. Droop rate is typically less than 5 mV/s at 25°C.

The LM101A operational amplifier is utilized in a sample-and-hold circuit to ensure precise signal processing. The configuration begins with the input signal being buffered by the LM101A, which amplifies the signal while maintaining its integrity. The storage capacitor C2 plays a crucial role in holding the voltage level for processing. The resistor R2 introduces a zero in the open-loop frequency response, which effectively compensates for the pole formed due to the interaction between the switch resistance and C2. This compensation enhances the closed-loop stability of the circuit and ensures reliable performance during operation.

R1 is strategically placed to provide a slight delay in the digital drive signals sent to pins 1 and 9 of the LM101A. This delay can help mitigate issues related to timing mismatches in the circuit, ensuring that signals are properly synchronized during the sample-and-hold process. The capacitor C1 is critical for canceling any coupled charge that might interfere with the accuracy of the sample-and-hold function. By maintaining the sample-and-hold offset below 5 mV across the specified analog signal range of -10 V to +10 V, the circuit ensures high fidelity in signal reproduction.

The aperture time of the circuit is typically 1 picosecond, which indicates the precision timing capability of the system. The switching time of the DG441, which is used in conjunction with this circuit, also plays a significant role in determining the overall performance. The acquisition time, noted to be 25 picoseconds, can be further optimized by integrating a faster slewing operational amplifier, thereby enhancing the responsiveness of the circuit.

The droop rate, which is observed to be less than 5 mV/s at a temperature of 25°C, reflects the stability of the stored voltage over time. This characteristic is essential for applications requiring long-duration signal retention without significant degradation, ensuring that the output remains stable and reliable throughout the operation. Overall, the described circuit configuration is designed to provide high-performance signal processing with minimal offsets and optimal stability.The LM101A provides gain and buffers the input from storage capacitor C2. R2 adds a zero in the open loop response to compensate for the pole caused by the switch resistance and C2, improving the closed-loop stability. R1 provides a slight delay in the digital drive to pins 1 and 9. C1 provides cancellation of coupled charge, keeping the sample-and-hold offset below 5 mV over the analog signal range of -10 through +10 V.

Aperture time is typically 1 p.s, the switcl>.ing time of the DG441. Acquisition time is 25 p.s, but this can be improved by using a faster slewing op amp. Droop rate is typically less than 5 mV/s at 25°C.

The LM101A operational amplifier is utilized in a sample-and-hold circuit to ensure precise signal processing. The configuration begins with the input signal being buffered by the LM101A, which amplifies the signal while maintaining its integrity. The storage capacitor C2 plays a crucial role in holding the voltage level for processing. The resistor R2 introduces a zero in the open-loop frequency response, which effectively compensates for the pole formed due to the interaction between the switch resistance and C2. This compensation enhances the closed-loop stability of the circuit and ensures reliable performance during operation.

R1 is strategically placed to provide a slight delay in the digital drive signals sent to pins 1 and 9 of the LM101A. This delay can help mitigate issues related to timing mismatches in the circuit, ensuring that signals are properly synchronized during the sample-and-hold process. The capacitor C1 is critical for canceling any coupled charge that might interfere with the accuracy of the sample-and-hold function. By maintaining the sample-and-hold offset below 5 mV across the specified analog signal range of -10 V to +10 V, the circuit ensures high fidelity in signal reproduction.

The aperture time of the circuit is typically 1 picosecond, which indicates the precision timing capability of the system. The switching time of the DG441, which is used in conjunction with this circuit, also plays a significant role in determining the overall performance. The acquisition time, noted to be 25 picoseconds, can be further optimized by integrating a faster slewing operational amplifier, thereby enhancing the responsiveness of the circuit.

The droop rate, which is observed to be less than 5 mV/s at a temperature of 25°C, reflects the stability of the stored voltage over time. This characteristic is essential for applications requiring long-duration signal retention without significant degradation, ensuring that the output remains stable and reliable throughout the operation. Overall, the described circuit configuration is designed to provide high-performance signal processing with minimal offsets and optimal stability.The LM101A provides gain and buffers the input from storage capacitor C2. R2 adds a zero in the open loop response to compensate for the pole caused by the switch resistance and C2, improving the closed-loop stability. R1 provides a slight delay in the digital drive to pins 1 and 9. C1 provides cancellation of coupled charge, keeping the sample-and-hold offset below 5 mV over the analog signal range of -10 through +10 V.

Aperture time is typically 1 p.s, the switcl>.ing time of the DG441. Acquisition time is 25 p.s, but this can be improved by using a faster slewing op amp. Droop rate is typically less than 5 mV/s at 25°C.