The CDMS II Veto Readout Electronics

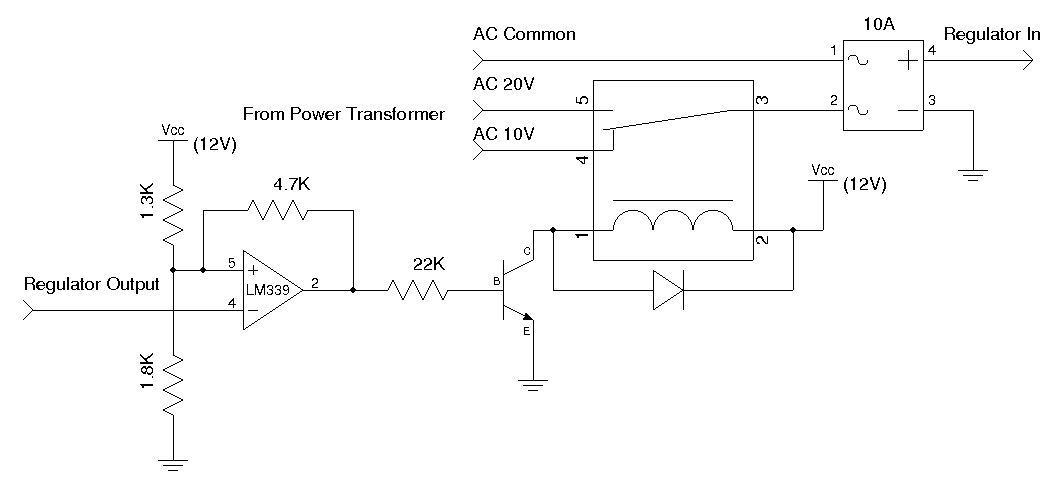

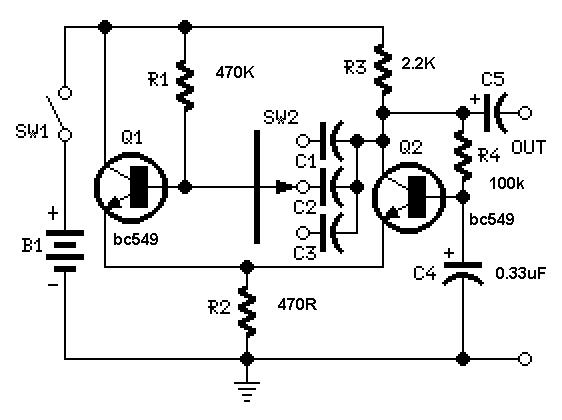

A Prototype Sample and Hold Circuit - The original concept for the veto front-end amplifiers was to continuously sample the input pulse height and maintain the pulse height for any pulses exceeding a low voltage threshold (approximately 10 mV). This mixed analog and digital circuit was successfully implemented. However, the highly variable rise times of the input pulses result in significant pulse height errors for all but a very limited range of input pulse heights.

The prototype sample and hold circuit is designed to capture and retain the amplitude of input pulses that exceed a specified voltage threshold. The primary function of this circuit is to ensure that only valid pulses, which surpass the threshold of approximately 10 mV, are processed further. The circuit operates by continuously sampling the input signal using a comparator to determine when the signal exceeds the defined threshold. Upon detecting a valid pulse, the circuit engages a sample and hold mechanism that captures the peak voltage of the pulse.

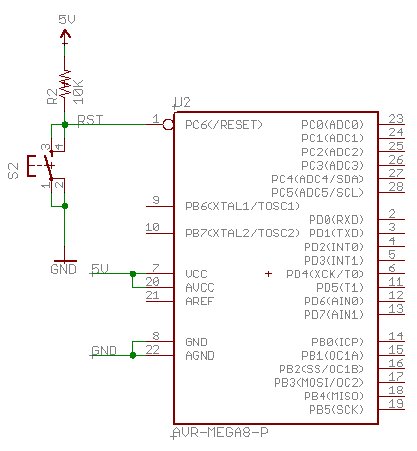

The implementation of the mixed analog and digital components allows for effective integration of the sampling process with digital logic for subsequent signal processing. The analog section typically includes operational amplifiers configured as comparators and sample-and-hold circuits, while the digital section may consist of a microcontroller or digital signal processor to handle the logic and control functions.

Challenges arise due to the variable rise times of the input pulses, which can lead to inaccuracies in the captured pulse heights. This variability can introduce significant errors, particularly for input pulses that fall outside the optimal range. To mitigate these issues, careful design considerations must be made, including the selection of appropriate components that can handle the dynamic characteristics of the input signals. Additionally, implementing filtering techniques and optimizing the timing of the sample and hold circuit can enhance performance and accuracy.

Overall, this prototype serves as a foundational circuit for applications requiring precise pulse height measurements while highlighting the importance of addressing rise time variability to improve reliability across a broader range of input conditions.A Prototype Sample and Hold Circuit -The original idea for the veto front end amps was to continually sample the input pulse height and hold the pulse height for any pulses passing a low voltage threshold (~10mV). This mixed analog and digital circuit was actually made to work. Unfortunately, the highly variable risetimes of the input pulses cause d large pulse height errors for all but a very limitied range of input pulse heights. 🔗 External reference

The prototype sample and hold circuit is designed to capture and retain the amplitude of input pulses that exceed a specified voltage threshold. The primary function of this circuit is to ensure that only valid pulses, which surpass the threshold of approximately 10 mV, are processed further. The circuit operates by continuously sampling the input signal using a comparator to determine when the signal exceeds the defined threshold. Upon detecting a valid pulse, the circuit engages a sample and hold mechanism that captures the peak voltage of the pulse.

The implementation of the mixed analog and digital components allows for effective integration of the sampling process with digital logic for subsequent signal processing. The analog section typically includes operational amplifiers configured as comparators and sample-and-hold circuits, while the digital section may consist of a microcontroller or digital signal processor to handle the logic and control functions.

Challenges arise due to the variable rise times of the input pulses, which can lead to inaccuracies in the captured pulse heights. This variability can introduce significant errors, particularly for input pulses that fall outside the optimal range. To mitigate these issues, careful design considerations must be made, including the selection of appropriate components that can handle the dynamic characteristics of the input signals. Additionally, implementing filtering techniques and optimizing the timing of the sample and hold circuit can enhance performance and accuracy.

Overall, this prototype serves as a foundational circuit for applications requiring precise pulse height measurements while highlighting the importance of addressing rise time variability to improve reliability across a broader range of input conditions.A Prototype Sample and Hold Circuit -The original idea for the veto front end amps was to continually sample the input pulse height and hold the pulse height for any pulses passing a low voltage threshold (~10mV). This mixed analog and digital circuit was actually made to work. Unfortunately, the highly variable risetimes of the input pulses cause d large pulse height errors for all but a very limitied range of input pulse heights. 🔗 External reference