THE ZX97LITE SCHEMATIC

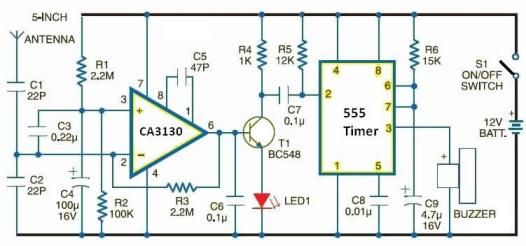

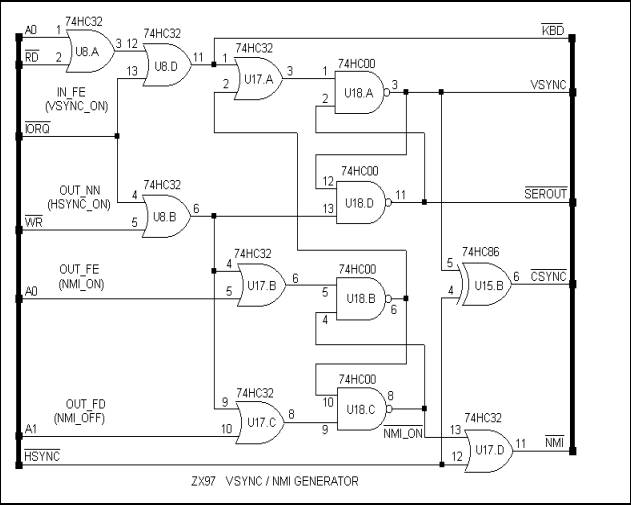

The ZX97 was developed as a discrete replica of the ZX81, which served as the first personal computer for millions. However, the ZX97 evolved into more than just a simple copy. While maintaining backward compatibility with the ZX81, it offers significant improvements in various aspects. In 1998, Rodney Knaap reached out to create a printed circuit board (PCB) for the ZX97, a task that proved to be quite challenging. The final design required three interconnected PCBs linked by flat cables. To facilitate easier construction for others, the ZX97Lite was created as a streamlined version of the ZX97, omitting the large RAMdisk and the 8255 parallel port. For a comprehensive background and details regarding Rodney's ZX projects, refer to Rodney Knaap's website, which also hosts the original ZX97 article and schematic. Rodney has designed a single-sided PCB for the ZX97Lite and has built and tested a prototype using this circuit. Attempts to contact Rodney have been unsuccessful for some time; however, inquiries for the latest CAD version of the ZX97Lite PCB are encouraged. If contact cannot be established, beta versions of the ZX97Lite single-sided PCB (ZX97LPCB for 600dpi printer), ZX97Lite parts and jumper layout (ZX97Lite Layout), and the ZX97 EPROM file (ZX97L 27C256 EPROM binary image) are available. While Rodney's ZX97Lite schematic significantly improved upon the original ZX97 ASCII drawing, it poses readability challenges due to color contrasts, dense layouts, bused signal lines, IEC logic symbols, crowded pin numbers, and minor errors and omissions. To enhance clarity, the schematic has been redrawn using ANSI symbols, reformatted to black on white, pin numbers renumbered, and missing components completed. The overall drawing was divided into smaller functional subsystems. The ZX97Lite is a simplified version of the ZX97 designed for a single-sided PCB. It functions as a complete ZX81 using discrete logic chips, featuring 32K of battery-backed RAM and 32K of EPROM. The user-selectable memory mapping allows the ZX97Lite to boot directly from user machine code in RAM. The circuit consumes only 50mA, making it suitable for battery or solar cell operation. The ZX97Lite operating system supports a bank-switched RAM/EPROM disk with a hotkey, demonstrating this feature with bundled utility machine code programs stored in a 16K bank of EPROM DISK. The expanded RAM/EPROM DISK circuit and the 8255 parallel port from the ZX97 were omitted to simplify the PCB layout. The ZX97Lite closely resembles the original ZX97, and thus, this description also applies to the original circuit. The CPU, utilizing a Z80, is the central subsystem. While a detailed discussion of all Z80 pin functions and CPU operations is not included, as they follow conventional usage and are readily accessible online, some CPU control lines are employed in unconventional manners related to the ZX81 video system. These specifics include: 1) The 3.25MHz CPU clock line is derived from the 6.5MHz video clock, divided by 2, to facilitate the loading of each video pattern byte into the 8-bit Video Shift Register during a NOP cycle, which consumes 4 CPU clock cycles while the 8 pixels are clocked out of the VSR with 8 video clock pulses. 2) As with the ZX81, the INT input connects to A6, where the Z80 decrements the refresh address counter, and the INT input is sampled during RFSH time for an active low on A6 to interrupt the HALT condition, which occurs at the end of each normal SINCLAIR video line. 3) The NMI line and its service routine at ROM address 0066 are utilized in SLOW mode to interrupt user program execution during blank video lines, switching to video display or VSYNC execution as needed. The NMI generator is controlled using OUT FE.

The ZX97Lite is designed as a compact and efficient alternative to the original ZX97, making it more accessible for hobbyists and engineers alike. Its single-sided PCB layout significantly reduces manufacturing complexity and costs, allowing for easier replication and modification. The omission of certain components, such as the RAMdisk and the 8255 parallel port, streamlines the design while still retaining the essential functionalities of the ZX81.

The architecture of the ZX97Lite emphasizes modularity, with the circuit divided into smaller functional subsystems. This modularity not only simplifies troubleshooting and upgrades but also enhances educational opportunities for those interested in understanding the workings of retro computing systems. The choice of the Z80 CPU, a well-documented and widely supported microprocessor, ensures that developers have access to a wealth of resources for programming and interfacing.

The power consumption of 50mA is particularly advantageous for portable applications, enabling the use of batteries or solar cells, which aligns with modern trends toward sustainable technology. The bank-switched RAM/EPROM disk feature allows for flexible software management, catering to the needs of users who may wish to run multiple programs or applications without requiring extensive hardware modifications.

In summary, the ZX97Lite represents a significant advancement over its predecessor while maintaining compatibility with the ZX81, making it a valuable addition to the lineage of personal computing. Its thoughtful design and user-friendly features ensure that it remains relevant in the current landscape of electronics and computing.I designed the ZX97 as a discrete copy of the ZX81, which was the first PC for millions of people. In the process ZX97 turned into much more than a mere copy. While it is backward compatible with the ZX81, it is in all other respects a significant improvement over the ZX81. In 1998, Rodney Knaap contacted me to offer to make a PCB of the ZX97 but this proved no small feat. The end result required 3 PCBs connected together with flat cables. In order to simplify the PCB for others to build I designed the ZX97Lite, a trimmed version of the ZX97 omitting the big RAMdIsk and the 8255 parallel port. For a full background on this story and details of Rodney`s ZX projects, check out Rodney Knaap`s Website where you will also find my original ZX97 article and schematic.

Rodney has designed a single sided PCB for the ZX97L and also build and tested a prototype using this circuit. I have been unable to contact Rodney for a long time but I would urge you to try and contact Rodney for the latest CAD version of the ZX97Lite PCB.

If you cannot get in touch with him, here are the beta version of the ZX97Lite single sided PCB ( ZX97LPCB - for 600pdi printer ), the ZX97Lite parts and jumper layout ( ZX97Lite Layout ) and my ZX97 EPROM file (ZX97L 27C256 EPROM binary image) While Rodney`s ZX97Lite schematic was a great improvement over my original ZX97 ASCII drawing, it is somewhat difficult to read because of the foreground and background colors, the dense layout, the bused signal lines, the IEC logic symbols, crowded pin numbers and in addition, it contains some minor errors and omissions In order to make the ZX97L easier to understand, I have redrawn the schematic by replacing the IEC logic with ANSI symbols, reformatted the drawing to black on white, renumbered pins and completed some missing bits. The overall drawing was then disassembled into byte sized smaller functional subsystems. The ZX97LITE is a simplified ZX97 designed to fit on one single sided PCB. The ZX97L is a complete ZX81 using discrete logic chips with 32K of battery backup RAM and 32K of EPROM.

User selectable memory mapping allows the ZX97L to boot directly from user M/C code in RAM. The circuit draws just 50mA so can easily be run from a battery or even solar cells. The ZX97L OS supports a bank switched RAM / EPROM disk with a hot key. The ZX97LITE demonstrates this feature with bundled utility machine code programs stored in one 16K bank of EPROM DISK. The expanded RAM / EPROM DISK circuit and the 8255 parallel port of the ZX97 were omitted in order to keep the PCB layout simple.

The ZX97L is virtually identical to the rest of the ZX97 and so this description therefore also applies that original circuit. The CPU is the subsystem that rules them all and uses a Z80 inside. I won`t go further into the details of the all Z80 pin functions and CPU operations as most are used in a conventional manner and information on this is readily available on the web.

But some of the CPU control lines are used in unconventional ways related to the ZX81 video system and these will be described in detail: 1) The 3. 25MHz CPU clock line is derived from the 6. 5MHz video clock after dividing by 2. This is required since the CPU must load each video pattern byte into the 8-bit Video Shift Register during a NOP cycle, which takes 4 CPU clock cycles while the 8 pixels are clocked out of the VSR with 8 video clock pulses.

2) Like the ZX81, the INT input is connected to A6. The Z80 decrements the refresh address counter and the INT input is sampled during RFSH time for an active low on A6 to interrupt the HALT condition. That HALT state occurs at the end of each normal SINCLAIR video line. 3) The NMI line and NMI service routine at ROM address 0066 is used in SLOW mode to interrupt user program execution during blank video lines to switch to video display or VSYNC execution when required.

The NMI generator is controlled with OUT FE 🔗 External reference

The ZX97Lite is designed as a compact and efficient alternative to the original ZX97, making it more accessible for hobbyists and engineers alike. Its single-sided PCB layout significantly reduces manufacturing complexity and costs, allowing for easier replication and modification. The omission of certain components, such as the RAMdisk and the 8255 parallel port, streamlines the design while still retaining the essential functionalities of the ZX81.

The architecture of the ZX97Lite emphasizes modularity, with the circuit divided into smaller functional subsystems. This modularity not only simplifies troubleshooting and upgrades but also enhances educational opportunities for those interested in understanding the workings of retro computing systems. The choice of the Z80 CPU, a well-documented and widely supported microprocessor, ensures that developers have access to a wealth of resources for programming and interfacing.

The power consumption of 50mA is particularly advantageous for portable applications, enabling the use of batteries or solar cells, which aligns with modern trends toward sustainable technology. The bank-switched RAM/EPROM disk feature allows for flexible software management, catering to the needs of users who may wish to run multiple programs or applications without requiring extensive hardware modifications.

In summary, the ZX97Lite represents a significant advancement over its predecessor while maintaining compatibility with the ZX81, making it a valuable addition to the lineage of personal computing. Its thoughtful design and user-friendly features ensure that it remains relevant in the current landscape of electronics and computing.I designed the ZX97 as a discrete copy of the ZX81, which was the first PC for millions of people. In the process ZX97 turned into much more than a mere copy. While it is backward compatible with the ZX81, it is in all other respects a significant improvement over the ZX81. In 1998, Rodney Knaap contacted me to offer to make a PCB of the ZX97 but this proved no small feat. The end result required 3 PCBs connected together with flat cables. In order to simplify the PCB for others to build I designed the ZX97Lite, a trimmed version of the ZX97 omitting the big RAMdIsk and the 8255 parallel port. For a full background on this story and details of Rodney`s ZX projects, check out Rodney Knaap`s Website where you will also find my original ZX97 article and schematic.

Rodney has designed a single sided PCB for the ZX97L and also build and tested a prototype using this circuit. I have been unable to contact Rodney for a long time but I would urge you to try and contact Rodney for the latest CAD version of the ZX97Lite PCB.

If you cannot get in touch with him, here are the beta version of the ZX97Lite single sided PCB ( ZX97LPCB - for 600pdi printer ), the ZX97Lite parts and jumper layout ( ZX97Lite Layout ) and my ZX97 EPROM file (ZX97L 27C256 EPROM binary image) While Rodney`s ZX97Lite schematic was a great improvement over my original ZX97 ASCII drawing, it is somewhat difficult to read because of the foreground and background colors, the dense layout, the bused signal lines, the IEC logic symbols, crowded pin numbers and in addition, it contains some minor errors and omissions In order to make the ZX97L easier to understand, I have redrawn the schematic by replacing the IEC logic with ANSI symbols, reformatted the drawing to black on white, renumbered pins and completed some missing bits. The overall drawing was then disassembled into byte sized smaller functional subsystems. The ZX97LITE is a simplified ZX97 designed to fit on one single sided PCB. The ZX97L is a complete ZX81 using discrete logic chips with 32K of battery backup RAM and 32K of EPROM.

User selectable memory mapping allows the ZX97L to boot directly from user M/C code in RAM. The circuit draws just 50mA so can easily be run from a battery or even solar cells. The ZX97L OS supports a bank switched RAM / EPROM disk with a hot key. The ZX97LITE demonstrates this feature with bundled utility machine code programs stored in one 16K bank of EPROM DISK. The expanded RAM / EPROM DISK circuit and the 8255 parallel port of the ZX97 were omitted in order to keep the PCB layout simple.

The ZX97L is virtually identical to the rest of the ZX97 and so this description therefore also applies that original circuit. The CPU is the subsystem that rules them all and uses a Z80 inside. I won`t go further into the details of the all Z80 pin functions and CPU operations as most are used in a conventional manner and information on this is readily available on the web.

But some of the CPU control lines are used in unconventional ways related to the ZX81 video system and these will be described in detail: 1) The 3. 25MHz CPU clock line is derived from the 6. 5MHz video clock after dividing by 2. This is required since the CPU must load each video pattern byte into the 8-bit Video Shift Register during a NOP cycle, which takes 4 CPU clock cycles while the 8 pixels are clocked out of the VSR with 8 video clock pulses.

2) Like the ZX81, the INT input is connected to A6. The Z80 decrements the refresh address counter and the INT input is sampled during RFSH time for an active low on A6 to interrupt the HALT condition. That HALT state occurs at the end of each normal SINCLAIR video line. 3) The NMI line and NMI service routine at ROM address 0066 is used in SLOW mode to interrupt user program execution during blank video lines to switch to video display or VSYNC execution when required.

The NMI generator is controlled with OUT FE 🔗 External reference