TV Decoder

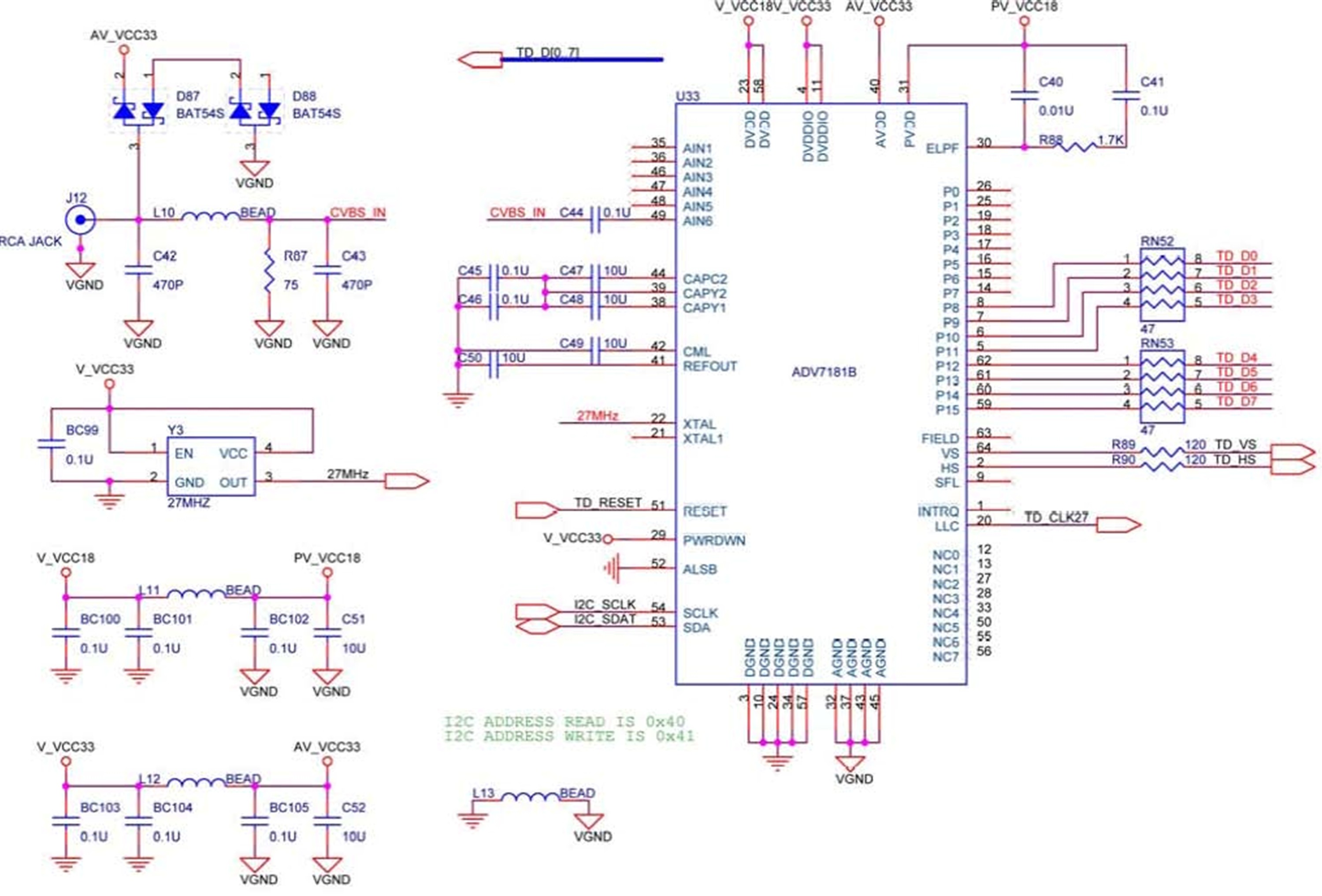

The DE2 board features an Analog Devices ADV7181 TV decoder chip. The ADV7181 is an integrated video decoder that automatically detects and converts standard analog baseband television signals (NTSC, PAL, and SECAM) into 4:2:2 component video data, which is compatible with 16-bit/8-bit CCIR601/CCIR656. It is compatible with a wide range of video devices, including DVD players, tape-based sources, broadcast sources, and security/surveillance cameras. The registers of the TV decoder can be programmed via a serial I2C bus connected to the Cyclone II FPGA, as shown in Figure 1. The pin assignments are detailed in Table 1. Additional information on the ADV7181 can be found on the manufacturer's website and in the Datasheet folder on the DE2 System CD-ROM. The DE2_pin_assignments.csv file provides a mapping of standard descriptive names to actual FPGA pin locations and can be opened directly in Microsoft Excel. While the DE2 board does not include a TV encoder chip, the ADV7123 (10-bit high-speed triple ADCs) can be utilized to create a professional-quality TV encoder, with the digital processing implemented in the Cyclone II FPGA. Figure 2 illustrates a block diagram of a TV encoder constructed in this manner.

The DE2 board, utilizing the ADV7181 TV decoder chip, serves as a versatile platform for video processing applications. The ADV7181's ability to automatically detect various analog television signals ensures its adaptability to different input sources, enhancing its utility in multimedia projects. The conversion of these signals into a 4:2:2 component format facilitates compatibility with high-quality video processing standards, making it suitable for integration with both consumer and professional video equipment.

Programming the ADV7181's registers through the I2C bus simplifies the configuration process, allowing for efficient control and customization of the video decoding parameters. The connection to the Cyclone II FPGA enables further processing and manipulation of the video data, leveraging the FPGA's capabilities for real-time applications. The detailed pin assignments provided in the DE2_pin_assignments.csv file are essential for developers to ensure correct interfacing between the ADV7181 and the FPGA, promoting effective signal routing and minimizing potential errors in the design.

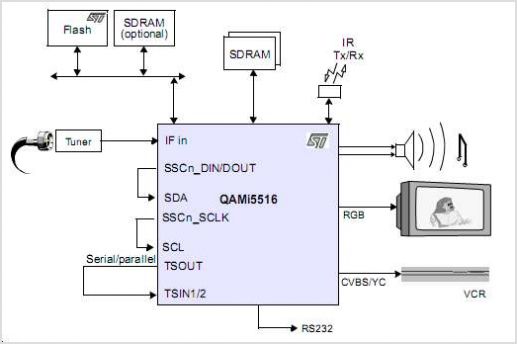

Although the DE2 board lacks a dedicated TV encoder chip, the option to implement the ADV7123 allows for the creation of a comprehensive video encoding solution. By utilizing the high-speed triple ADCs in conjunction with the Cyclone II FPGA, developers can achieve high-quality video output suitable for broadcasting or other applications. The block diagram referenced in Figure 2 outlines the architecture of such a system, illustrating the integration of the ADV7123 with the FPGA for seamless video encoding. Overall, the DE2 board presents a robust solution for projects requiring advanced video decoding and encoding capabilities.The DE2 board is equipped with an Analog Devices ADV7181 TV decoder chip. The ADV7181 is an integrated video decoder that automatically detects and converts a standard analog baseband television signal (NTSC, PAL, and SECAM) into 4:2:2 component video data compatible with 16-bit/8-bit CCIR601/CCIR656. The ADV7181 is compatible with a broad range o f video devices, including DVD players, tape-based sources, broadcast sources, and security/surveillance cameras. The registers in the TV decoder can be programmed by a serial I2C bus, which is connected to the Cyclone II FPGA as indicated in Figure 1.

The pin assignments are listed in Table 1. Detailed information on the ADV7181 is available on the manufacturer`s web site, and from the Datasheet folder on the DE2 System CD-ROM. See DE2_pin_assignments. csv, a comma-delimited file that matches "standard" descriptive names to actual FPGA pin locations. This file can be directly opened in Microsoft Excel. Although the DE2 board does not include a TV encoder chip, the ADV7123 (10-bit high-speed triple ADCs) can be used to implement a professional-quality TV encoder with the digital processing part implemented in the Cyclone II FPGA.

Figure 2 shows a block diagram of a TV encoder implemented in this manner. 🔗 External reference

The DE2 board, utilizing the ADV7181 TV decoder chip, serves as a versatile platform for video processing applications. The ADV7181's ability to automatically detect various analog television signals ensures its adaptability to different input sources, enhancing its utility in multimedia projects. The conversion of these signals into a 4:2:2 component format facilitates compatibility with high-quality video processing standards, making it suitable for integration with both consumer and professional video equipment.

Programming the ADV7181's registers through the I2C bus simplifies the configuration process, allowing for efficient control and customization of the video decoding parameters. The connection to the Cyclone II FPGA enables further processing and manipulation of the video data, leveraging the FPGA's capabilities for real-time applications. The detailed pin assignments provided in the DE2_pin_assignments.csv file are essential for developers to ensure correct interfacing between the ADV7181 and the FPGA, promoting effective signal routing and minimizing potential errors in the design.

Although the DE2 board lacks a dedicated TV encoder chip, the option to implement the ADV7123 allows for the creation of a comprehensive video encoding solution. By utilizing the high-speed triple ADCs in conjunction with the Cyclone II FPGA, developers can achieve high-quality video output suitable for broadcasting or other applications. The block diagram referenced in Figure 2 outlines the architecture of such a system, illustrating the integration of the ADV7123 with the FPGA for seamless video encoding. Overall, the DE2 board presents a robust solution for projects requiring advanced video decoding and encoding capabilities.The DE2 board is equipped with an Analog Devices ADV7181 TV decoder chip. The ADV7181 is an integrated video decoder that automatically detects and converts a standard analog baseband television signal (NTSC, PAL, and SECAM) into 4:2:2 component video data compatible with 16-bit/8-bit CCIR601/CCIR656. The ADV7181 is compatible with a broad range o f video devices, including DVD players, tape-based sources, broadcast sources, and security/surveillance cameras. The registers in the TV decoder can be programmed by a serial I2C bus, which is connected to the Cyclone II FPGA as indicated in Figure 1.

The pin assignments are listed in Table 1. Detailed information on the ADV7181 is available on the manufacturer`s web site, and from the Datasheet folder on the DE2 System CD-ROM. See DE2_pin_assignments. csv, a comma-delimited file that matches "standard" descriptive names to actual FPGA pin locations. This file can be directly opened in Microsoft Excel. Although the DE2 board does not include a TV encoder chip, the ADV7123 (10-bit high-speed triple ADCs) can be used to implement a professional-quality TV encoder with the digital processing part implemented in the Cyclone II FPGA.

Figure 2 shows a block diagram of a TV encoder implemented in this manner. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713