TV video output for the EB675001DIP

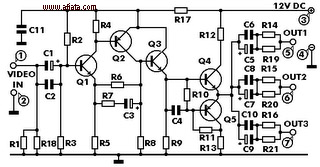

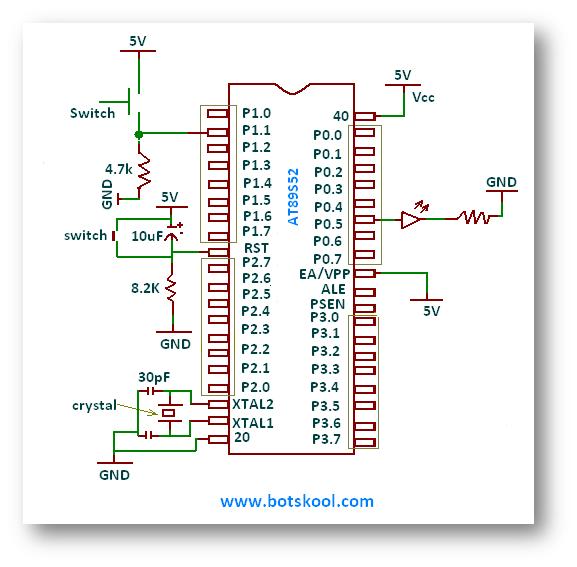

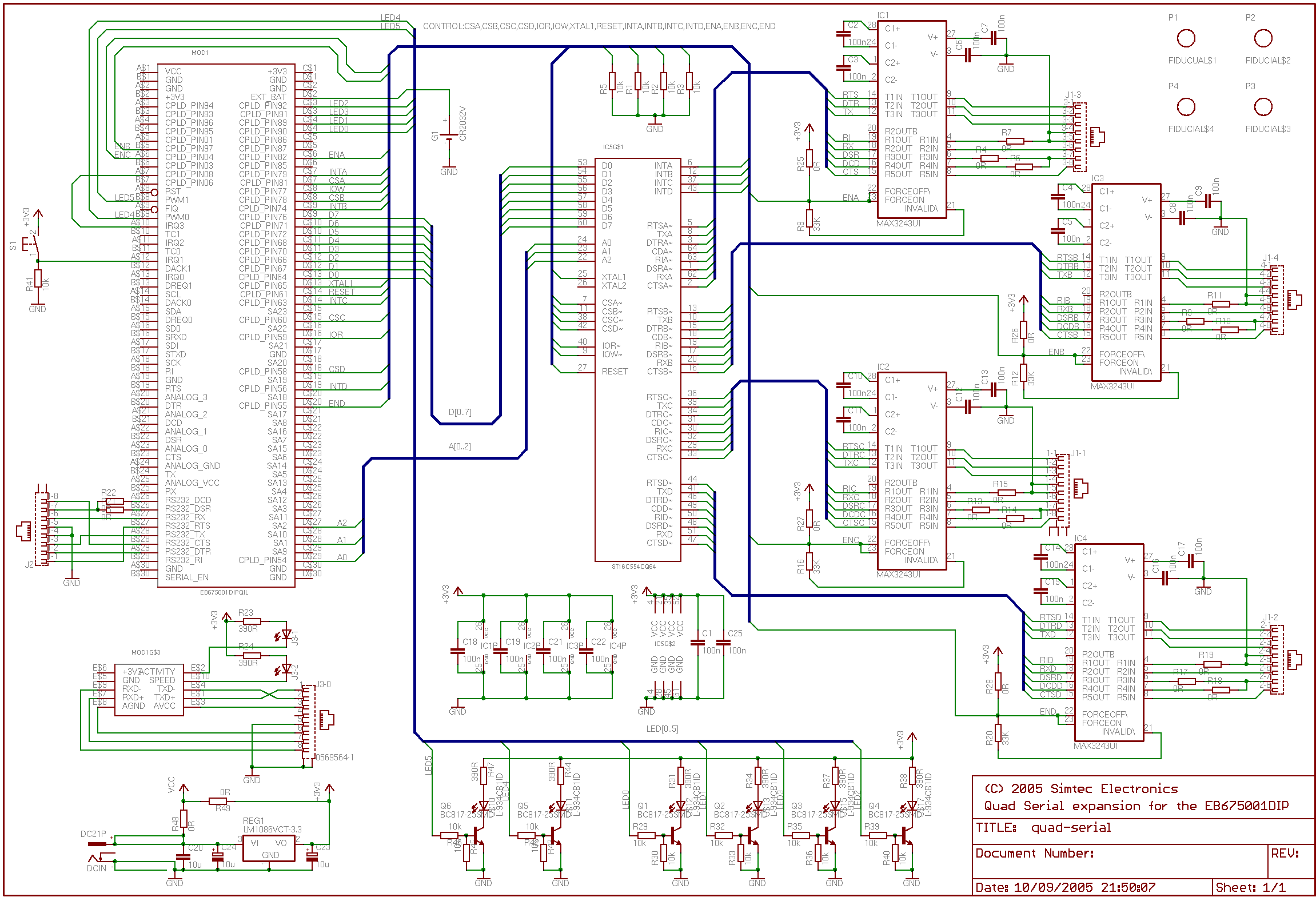

This application note outlines the creation of a basic framebuffer with PAL composite TV output for the EB675001DIP. The design employs a minimal number of additional components to facilitate this display. A user-configurable CPLD is utilized to provide all control and timing logic, thereby simplifying circuit complexity. Further information on composite video, related circuits, and techniques can be found online, with resources such as the Epanorama list of links and Rickard GunGé's video tutorial being particularly helpful. Monochrome composite video can be produced using a straightforward method that involves two logic outputs and carefully chosen resistor values to generate the necessary voltage levels. In its simplest form, composite video comprises a voltage level ranging from 0 to 1V, where 0V represents synchronization, 0.3V indicates the black level, and 1V corresponds to the white level. Various shades can be created by varying the voltage between the 0.3V and 1V levels; however, for this basic display, black and white suffices. A video frame consists of two fields of 312 scan lines displayed 25 times per second. For simplicity, the odd and even fields are treated as identical, effectively halving vertical resolution but simplifying the design by eliminating interlacing. Consequently, 312 scan lines are produced at a rate of 50 times per second, resulting in a line rate of 15,600 lines per second (the accurate line rate is 15,625, but the omission of 25 lines is not problematic in practice). Each scan line lasts for 64 microseconds and consists of a "front porch" of 2 microseconds, a horizontal sync pulse of 4 microseconds, a rear porch of 6 microseconds, and 52 microseconds of displayed data. The diagram illustrates this along with a typical scan line waveform for video bars. The final aspect of the signal requiring explanation is the vertical synchronization that initiates each field; the required waveform is depicted in the diagram. Although the second field of each frame should theoretically have a slightly different waveform, this is often unnecessary in practice. The proposed solution employs an external SRAM to store framebuffer data. The CPLD is responsible for generating appropriate timing to clock eight bits from the SRAM into the shift register every 500 nanoseconds. A 256Kbit SRAM clocked in this manner provides 256 scan lines of 64 microseconds each. The shift register is clocked every 62.5 nanoseconds (16 MHz rate), resulting in 1024 bits per line, although some bits will not be visible as they are output during the border and sync times. A continuous clock simplifies the design significantly. In addition to SRAM clocking, the CPLD generates SYNC and BLANK signals to ensure that the output waveform maintains proper sync and black levels at the correct times. The CPLD also produces the vertical synchronization waveform and guarantees that the top and bottom borders are at the black level. Data is written directly to the SRAM by the OKI CPU, with the CPLD managing correct timing and operation by utilizing the CPU I/O wait function to delay access until the appropriate moment. As the CPLD generates the vertical sync and can produce an interrupt, it is feasible to use a photodiode to detect the scanning beam's passage (on a CRT) and calculate the elapsed time, thereby determining the photodiode's position on the screen. This functionality would enable a light pen feature. The schematic delineates a specific design based on the general ideas previously outlined. The design was created by establishing data, address, and control buses and connecting the SRAM accordingly. Initially, it was anticipated that the external shift register could be eliminated by integrating it into the CPLD code; however, due to resource limitations within the CPLD, this could not be accomplished. The design was left with the option to operate in this mode by incorporating resistor R3, allowing the CPLD CLK register to serve as the output instead. The output from the shift register is combined with the SYNC and BLANK signals to produce the final composite video output.

The design of the framebuffer system is a sophisticated integration of various electronic components and logic functions aimed at generating a composite video output suitable for PAL television systems. The use of a CPLD for control and timing logic is particularly advantageous as it minimizes the need for discrete components, thereby reducing overall circuit complexity and improving reliability. The implementation of an external SRAM for framebuffer storage allows for efficient data handling and retrieval, essential for maintaining the required frame rates and synchronization in video output.

The choice of a 256Kbit SRAM is optimal for this application, as it provides sufficient capacity for storing the framebuffer data for multiple scan lines while ensuring quick access times. The timing control generated by the CPLD is critical; it ensures that data is clocked into the shift register at the correct intervals, maintaining the integrity of the video signal. The design's approach to generating SYNC and BLANK signals is also noteworthy, as these signals are crucial for proper display synchronization and image stability.

Moreover, the potential for integrating a light pen functionality through the use of a photodiode introduces an interactive element to the design, enhancing its versatility. This feature allows for user interaction with the display, which can be particularly useful in applications requiring graphical input.

Overall, the described design represents a well-thought-out approach to generating a monochrome composite video output, balancing simplicity with functionality, and providing a foundation for further enhancements or modifications as needed.This application note describes creating a dumb framebuffer with PAL composite TV output for the EB675001DIP. The design uses a minimal number of additional components to achieve this display. The user CPLD is used to provide all control and timing logic reducing circuit complexity. More in depth information on composite video, associated circui ts and techniques can be found across the web a useful resource is the epanorama list of links and Rickard GunG©e video howto Monochrome composite video can be generated with a very simple method. By using two logic outputs and carefully selected resistor values the required voltage levels can be generated.

Composite video in its most basic form consists of a voltage level between 0 and 1V, where 0 V is used for synchronization, 0. 3V is used as black level and 1V is used as a white level. Obviously almost any shade can be created by varying the voltage between the 0. 3 and 1V levels, however for the simple display presented here black and white will suffice. A video frame is made up from two fields of 312 scan lines displayed 25 times a second. For our purposes we will treat the odd and even fields as identical, this halves our vertical resolution but makes the design much simpler as we don`t have to do interlacing, effectively therefore we are producing 312 scan lines 50 times a second giving a line rate of 15, 600 lines per second (strictly speaking each frame has an additional line and the correct line rate is 15, 625 however the missing 25 lines will not prove problematic in practice).

Each scan line lasts for 64 S and consists of a "front porch" of 2 S, a horizontal sync pulse of 4 S, a rear porch of 6 S and 52 S of displayed data. The diagram illustrates this along with a typical scan line waveform for some video bars. The last part of the signal that needs explaining is the vertical synchronization that starts each field, the required waveform is shown in the diagram.

Strictly speaking the second field of each frame should be a slightly different waveform, however in practice this doesn`t seem necessary. The proposed solution uses an external SRAM to hold the framebuffer data. The CPLD is used to generate appropriate timing to clock eight bits from the SRAM into the shift register every 500nS.

A 256Kbit SRAM when clocked in this manner provides 256 64uS scan lines. The shift register is clocked once every 62. 5nS (16MHz rate) giving 1024bits per line, some of these bits will not be viewable as they are output during the boarders and sync times but a continuous clock greatly simplifies the design. In addition to the SRAM clocking the CPLD generates the SYNC and BLANK signals to ensure the output waveform has sync and black levels at the appropriate times.

The CPLD also generates the vertical synchronization waveform and ensures the top and bottom borders are black level. Data is written to the SRAM directly by the OKI CPU, the CPLD ensures correct timing and operation by using the CPU I/O wait function to delay access until the appropriate time.

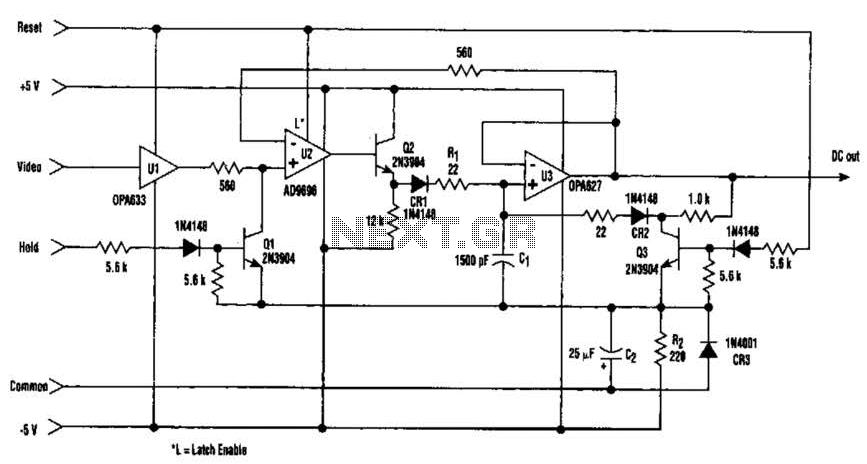

Because the CPLD generates the vertical sync and can generate an interrupt it is possible to use a photodiode to detect the passing of the scanning beam (on a CRT) and calculate the time elapsed and hence the location of the photodiode on the screen. This would give a light pen function. The schematic creates a specific design from the general ideas outlined previously. The design was generated directly by creating data, address and control buses and connecting the SRAM accordingly.

Initially it was hoped the external shift register could be avoided by integrating it into the CPLD code, however CPLD resources were exhausted and this could not be achieved. The option was left for this mode of operation by adding R3 to the design to allow the CPLD CLK register to be used as the output instead.

The output from the shift register is combined with the SYNC and BLANK signals to all 🔗 External reference

The design of the framebuffer system is a sophisticated integration of various electronic components and logic functions aimed at generating a composite video output suitable for PAL television systems. The use of a CPLD for control and timing logic is particularly advantageous as it minimizes the need for discrete components, thereby reducing overall circuit complexity and improving reliability. The implementation of an external SRAM for framebuffer storage allows for efficient data handling and retrieval, essential for maintaining the required frame rates and synchronization in video output.

The choice of a 256Kbit SRAM is optimal for this application, as it provides sufficient capacity for storing the framebuffer data for multiple scan lines while ensuring quick access times. The timing control generated by the CPLD is critical; it ensures that data is clocked into the shift register at the correct intervals, maintaining the integrity of the video signal. The design's approach to generating SYNC and BLANK signals is also noteworthy, as these signals are crucial for proper display synchronization and image stability.

Moreover, the potential for integrating a light pen functionality through the use of a photodiode introduces an interactive element to the design, enhancing its versatility. This feature allows for user interaction with the display, which can be particularly useful in applications requiring graphical input.

Overall, the described design represents a well-thought-out approach to generating a monochrome composite video output, balancing simplicity with functionality, and providing a foundation for further enhancements or modifications as needed.This application note describes creating a dumb framebuffer with PAL composite TV output for the EB675001DIP. The design uses a minimal number of additional components to achieve this display. The user CPLD is used to provide all control and timing logic reducing circuit complexity. More in depth information on composite video, associated circui ts and techniques can be found across the web a useful resource is the epanorama list of links and Rickard GunG©e video howto Monochrome composite video can be generated with a very simple method. By using two logic outputs and carefully selected resistor values the required voltage levels can be generated.

Composite video in its most basic form consists of a voltage level between 0 and 1V, where 0 V is used for synchronization, 0. 3V is used as black level and 1V is used as a white level. Obviously almost any shade can be created by varying the voltage between the 0. 3 and 1V levels, however for the simple display presented here black and white will suffice. A video frame is made up from two fields of 312 scan lines displayed 25 times a second. For our purposes we will treat the odd and even fields as identical, this halves our vertical resolution but makes the design much simpler as we don`t have to do interlacing, effectively therefore we are producing 312 scan lines 50 times a second giving a line rate of 15, 600 lines per second (strictly speaking each frame has an additional line and the correct line rate is 15, 625 however the missing 25 lines will not prove problematic in practice).

Each scan line lasts for 64 S and consists of a "front porch" of 2 S, a horizontal sync pulse of 4 S, a rear porch of 6 S and 52 S of displayed data. The diagram illustrates this along with a typical scan line waveform for some video bars. The last part of the signal that needs explaining is the vertical synchronization that starts each field, the required waveform is shown in the diagram.

Strictly speaking the second field of each frame should be a slightly different waveform, however in practice this doesn`t seem necessary. The proposed solution uses an external SRAM to hold the framebuffer data. The CPLD is used to generate appropriate timing to clock eight bits from the SRAM into the shift register every 500nS.

A 256Kbit SRAM when clocked in this manner provides 256 64uS scan lines. The shift register is clocked once every 62. 5nS (16MHz rate) giving 1024bits per line, some of these bits will not be viewable as they are output during the boarders and sync times but a continuous clock greatly simplifies the design. In addition to the SRAM clocking the CPLD generates the SYNC and BLANK signals to ensure the output waveform has sync and black levels at the appropriate times.

The CPLD also generates the vertical synchronization waveform and ensures the top and bottom borders are black level. Data is written to the SRAM directly by the OKI CPU, the CPLD ensures correct timing and operation by using the CPU I/O wait function to delay access until the appropriate time.

Because the CPLD generates the vertical sync and can generate an interrupt it is possible to use a photodiode to detect the passing of the scanning beam (on a CRT) and calculate the time elapsed and hence the location of the photodiode on the screen. This would give a light pen function. The schematic creates a specific design from the general ideas outlined previously. The design was generated directly by creating data, address and control buses and connecting the SRAM accordingly.

Initially it was hoped the external shift register could be avoided by integrating it into the CPLD code, however CPLD resources were exhausted and this could not be achieved. The option was left for this mode of operation by adding R3 to the design to allow the CPLD CLK register to be used as the output instead.

The output from the shift register is combined with the SYNC and BLANK signals to all 🔗 External reference