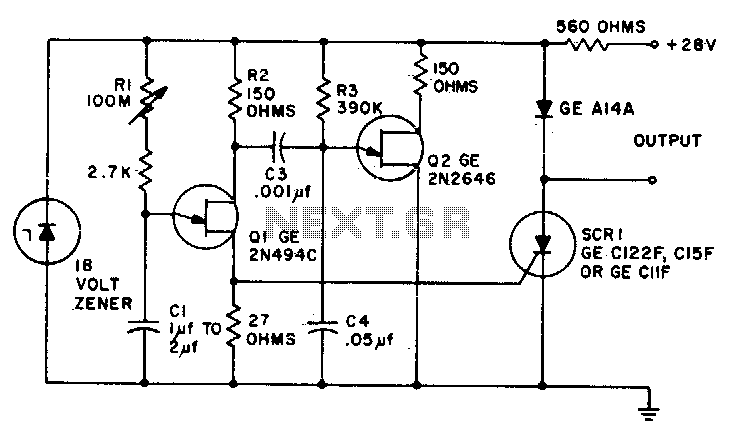

Ultra-precise long time delay relay

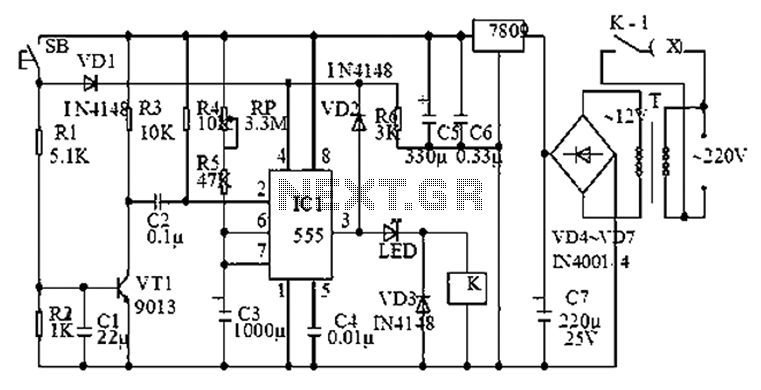

Predictable time delays ranging from 0 milliseconds to over 3 minutes can be achieved without the use of a large electrolytic timing capacitor. Instead, a stable low leakage paper or mylar capacitor is employed, effectively reducing the peak point current of the timing UJT (Q1), allowing for the substitution of a large value emitter resistor (R1).

In this circuit, the timing mechanism is primarily based on the use of a Unijunction Transistor (UJT) as the timing element. The UJT, designated as Q1, is crucial for generating the desired time delays. The choice of a low leakage capacitor, such as a paper or mylar capacitor, is essential for maintaining stability in the timing circuit. These capacitors exhibit minimal leakage current, which ensures that the charge-discharge cycle remains consistent and predictable over time.

The timing delay is determined by the RC time constant, where R1 serves as the emitter resistor and the chosen capacitor (C) acts as the timing capacitor. By utilizing a larger emitter resistor, the circuit can achieve longer time delays without necessitating a correspondingly large capacitance value, which is often required in traditional timing circuits using electrolytic capacitors. This design choice not only simplifies the circuit but also enhances reliability by reducing the size and potential failure points associated with larger electrolytic capacitors.

The operation of the circuit can be summarized as follows: when power is applied, the capacitor begins to charge through the resistor R1. Once the voltage across the capacitor reaches the peak point voltage of the UJT, the transistor will conduct, allowing current to flow through the emitter resistor. The discharge of the capacitor through the resistor determines the timing interval, which can be adjusted by varying the values of R1 and the capacitance.

Overall, this configuration allows for a versatile timing solution, capable of producing a wide range of delays while maintaining circuit integrity and performance.Predictable time delays from as low as 0 milliseconds to over 3 minutes are obtainable without resorting to a large value electrolytic-type timing capacitor Instead, a stable low leakage paper or mylar capacitor is used and the peak point current of the timing UJT (Ql) is effectively reduced, so that a large value emitter resistor (Rl) may be substituted. 🔗 External reference

In this circuit, the timing mechanism is primarily based on the use of a Unijunction Transistor (UJT) as the timing element. The UJT, designated as Q1, is crucial for generating the desired time delays. The choice of a low leakage capacitor, such as a paper or mylar capacitor, is essential for maintaining stability in the timing circuit. These capacitors exhibit minimal leakage current, which ensures that the charge-discharge cycle remains consistent and predictable over time.

The timing delay is determined by the RC time constant, where R1 serves as the emitter resistor and the chosen capacitor (C) acts as the timing capacitor. By utilizing a larger emitter resistor, the circuit can achieve longer time delays without necessitating a correspondingly large capacitance value, which is often required in traditional timing circuits using electrolytic capacitors. This design choice not only simplifies the circuit but also enhances reliability by reducing the size and potential failure points associated with larger electrolytic capacitors.

The operation of the circuit can be summarized as follows: when power is applied, the capacitor begins to charge through the resistor R1. Once the voltage across the capacitor reaches the peak point voltage of the UJT, the transistor will conduct, allowing current to flow through the emitter resistor. The discharge of the capacitor through the resistor determines the timing interval, which can be adjusted by varying the values of R1 and the capacitance.

Overall, this configuration allows for a versatile timing solution, capable of producing a wide range of delays while maintaining circuit integrity and performance.Predictable time delays from as low as 0 milliseconds to over 3 minutes are obtainable without resorting to a large value electrolytic-type timing capacitor Instead, a stable low leakage paper or mylar capacitor is used and the peak point current of the timing UJT (Ql) is effectively reduced, so that a large value emitter resistor (Rl) may be substituted. 🔗 External reference