Voltage controlled gain amplifier LM307

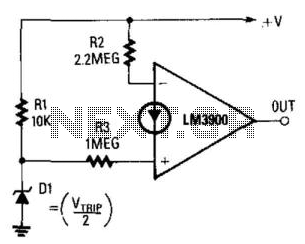

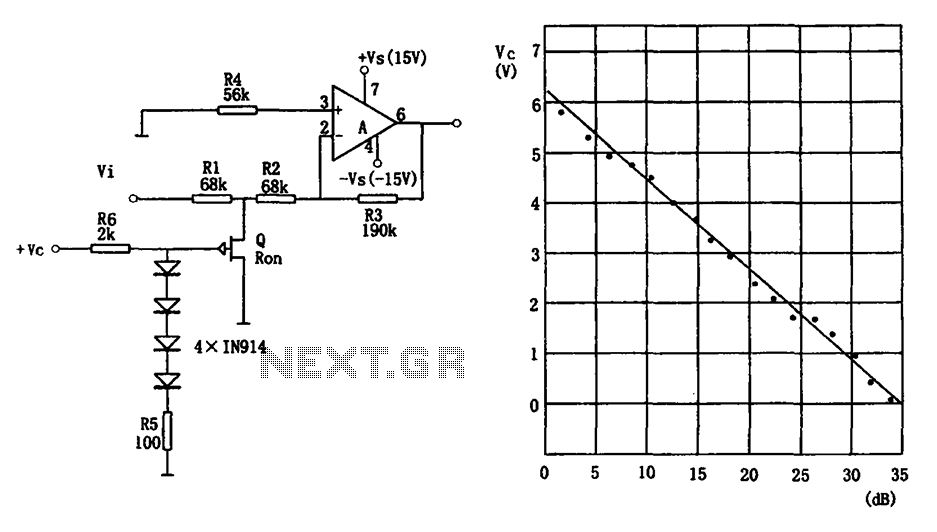

The voltage-controlled gain amplifier utilizes a FET gate voltage and the drain-source resistance (RSD) to approximate a logarithmic relationship. The integrated circuit chip LM307 is employed in the amplifier circuit with the inverting input configuration. In the circuit, RSD and R1 create a voltage divider for the input voltage (Vi). The voltage drop across the 1N914 diode, along with the voltage drop across resistor R5, results in a gate voltage (VG) for the FET. The control voltage (VC) is nonlinear, and there is a corresponding relationship between the attenuation controlled by VC and the amplifier gain. Specifically, as illustrated, a higher control voltage VC results in reduced attenuation of the amplifier gain. For instance, when VC is 7V, the amplifier achieves maximum gain (minimum attenuation), whereas at VC of 0V, the amplifier experiences maximum attenuation (minimum gain). The maximum gain of the circuit is defined as Avmax = R3 / (R1 + R2) when VC is 7V, while the minimum gain is Avmin = R3 / (R2 // RSD + R1) when VC is 0V. The upper cutoff frequency of the circuit is influenced by the low-pass filter formed between R1 and the capacitance of the FET. Under the specified conditions in Figure (A), the worst-case upper cutoff frequency can reach up to 1.8 MHz when VC is measured at 7V, indicating the maximum gain scenario. The primary parameters of the LM307 integrated chip are also considered in this configuration.

The voltage-controlled gain amplifier circuit employs a Field Effect Transistor (FET) to modulate gain based on an input control voltage. The configuration utilizes the LM307 integrated circuit, which is designed for operational amplifier applications, particularly in analog signal processing. The circuit's inverting input is critical for establishing the desired gain characteristics.

The resistors R1 and RSD form a voltage divider that determines the input voltage (Vi) to the amplifier. The diode (1N914) introduces a specific forward voltage drop that affects the gate voltage (VG) of the FET, which is essential for controlling the amplifier's gain. The relationship between the control voltage (VC) and the gain is nonlinear; as VC increases, the gain of the amplifier increases due to reduced attenuation. This behavior allows for precise control over the output signal, making it suitable for applications requiring variable gain.

The gain equations provided (Avmax and Avmin) outline the maximum and minimum gain states of the amplifier, depending on the control voltage. The maximum gain occurs when the control voltage is at its highest (7V), while the minimum gain is observed when the control voltage is at its lowest (0V). The circuit's performance is heavily influenced by the selected resistor values (R1, R2, R3, and RSD), which dictate the gain levels.

The upper cutoff frequency of the amplifier is determined by the low-pass filter characteristics, which consist of the resistor R1 and the capacitance associated with the FET. This cutoff frequency is a critical parameter for applications where bandwidth is a consideration. The stated maximum cutoff frequency of 1.8 MHz indicates the frequency range over which the amplifier can effectively operate without significant attenuation of the signal.

In summary, this voltage-controlled gain amplifier circuit exemplifies the integration of analog components to achieve variable gain control, suitable for a variety of signal processing applications. The LM307 integrated circuit serves as a robust platform for implementing these functionalities, with careful attention to the selection of passive components to optimize performance. As shown for the voltage-controlled gain amplifier. Use FET gate voltage and the drain - source resistance between RSD to approximate logarithmic relationship may constitute a voltage-controlled gain amplifier. The integrated circuit chip LM307 amplifier circuit, take the inverting input. Figure (a) shows that, RSD and R1 form a voltage divider (for Vi partial pressure). 4 1N914 diode voltage drop and the voltage drop across the resistor R5 and the gate voltage VG is equal to the FET. The VG control voltage VC is nonlinear, but the amount of attenuation control voltage VC and the amplifier gain corresponding relationship as shown in (b) below.

Figure (b) shows that the larger the control voltage VC, the smaller the amount of attenuation of the amplifier gain, that is, when VC 7V, amplifier gain maximum (minimum attenuation); when VC 0V, the maximum amount of attenuation of the amplifier gain ( the minimum gain). Figure (a) shows the maximum and minimum gain of the circuit is: When VC 7v, the maximum gain is: Avmax -R3/(R1 + R2).

When VC 0V, the minimum gain is: Avmin -R3/(R2 // RSD + R1). The circuits upper cutoff frequency depends on the low-pass filter between R1 and FET capacitance posed. For the FIG. (A) component parameters as shown in its worst upper cut-off frequency up to 1.8MHz, the value in the case of VC 7V measured (ie, the maximum gain of the circuit is measured).

The main parameters (typ) LM307 integrated chip

The voltage-controlled gain amplifier circuit employs a Field Effect Transistor (FET) to modulate gain based on an input control voltage. The configuration utilizes the LM307 integrated circuit, which is designed for operational amplifier applications, particularly in analog signal processing. The circuit's inverting input is critical for establishing the desired gain characteristics.

The resistors R1 and RSD form a voltage divider that determines the input voltage (Vi) to the amplifier. The diode (1N914) introduces a specific forward voltage drop that affects the gate voltage (VG) of the FET, which is essential for controlling the amplifier's gain. The relationship between the control voltage (VC) and the gain is nonlinear; as VC increases, the gain of the amplifier increases due to reduced attenuation. This behavior allows for precise control over the output signal, making it suitable for applications requiring variable gain.

The gain equations provided (Avmax and Avmin) outline the maximum and minimum gain states of the amplifier, depending on the control voltage. The maximum gain occurs when the control voltage is at its highest (7V), while the minimum gain is observed when the control voltage is at its lowest (0V). The circuit's performance is heavily influenced by the selected resistor values (R1, R2, R3, and RSD), which dictate the gain levels.

The upper cutoff frequency of the amplifier is determined by the low-pass filter characteristics, which consist of the resistor R1 and the capacitance associated with the FET. This cutoff frequency is a critical parameter for applications where bandwidth is a consideration. The stated maximum cutoff frequency of 1.8 MHz indicates the frequency range over which the amplifier can effectively operate without significant attenuation of the signal.

In summary, this voltage-controlled gain amplifier circuit exemplifies the integration of analog components to achieve variable gain control, suitable for a variety of signal processing applications. The LM307 integrated circuit serves as a robust platform for implementing these functionalities, with careful attention to the selection of passive components to optimize performance. As shown for the voltage-controlled gain amplifier. Use FET gate voltage and the drain - source resistance between RSD to approximate logarithmic relationship may constitute a voltage-controlled gain amplifier. The integrated circuit chip LM307 amplifier circuit, take the inverting input. Figure (a) shows that, RSD and R1 form a voltage divider (for Vi partial pressure). 4 1N914 diode voltage drop and the voltage drop across the resistor R5 and the gate voltage VG is equal to the FET. The VG control voltage VC is nonlinear, but the amount of attenuation control voltage VC and the amplifier gain corresponding relationship as shown in (b) below.

Figure (b) shows that the larger the control voltage VC, the smaller the amount of attenuation of the amplifier gain, that is, when VC 7V, amplifier gain maximum (minimum attenuation); when VC 0V, the maximum amount of attenuation of the amplifier gain ( the minimum gain). Figure (a) shows the maximum and minimum gain of the circuit is: When VC 7v, the maximum gain is: Avmax -R3/(R1 + R2).

When VC 0V, the minimum gain is: Avmin -R3/(R2 // RSD + R1). The circuits upper cutoff frequency depends on the low-pass filter between R1 and FET capacitance posed. For the FIG. (A) component parameters as shown in its worst upper cut-off frequency up to 1.8MHz, the value in the case of VC 7V measured (ie, the maximum gain of the circuit is measured).

The main parameters (typ) LM307 integrated chip