Voltage doubler circuit using NE555

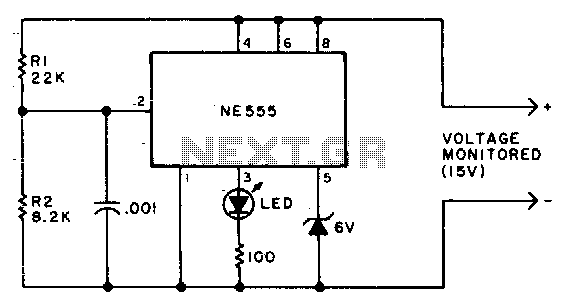

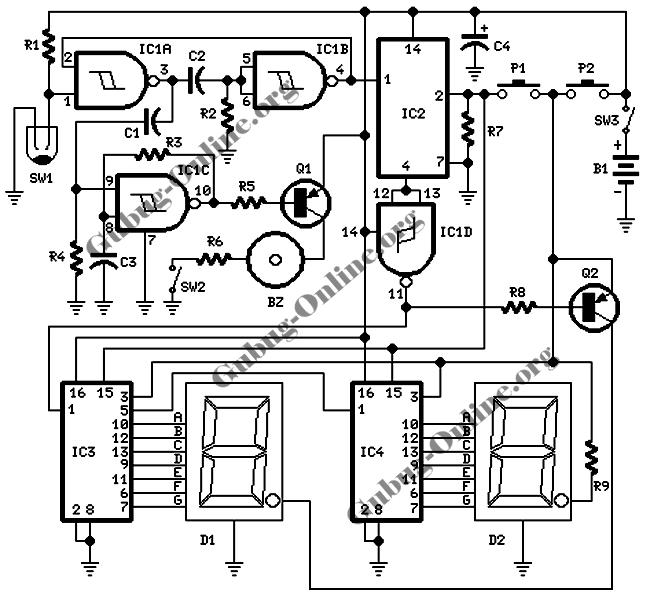

The circuit diagram of a simple voltage doubler using the NE555 timer is presented. In this configuration, the NE555 IC operates as an astable multivibrator at approximately 9 kHz. The bases of two transistors, Q1 and Q2, are connected together, with the output from the astable multivibrator (pin 3) linked to this point. When the astable multivibrator output is low, Q1 is turned off while Q2 is turned on. Consequently, the negative terminal of capacitor C3 is grounded through Q2, allowing it to charge to the input supply voltage. Conversely, when the astable multivibrator output is high, Q1 is activated and Q2 is deactivated. At this point, capacitor C4 charges to the sum of the voltage across capacitor C3 and the input supply voltage, effectively doubling the input voltage. This voltage doubler circuit can provide a maximum output current of 50 mA; exceeding this limit results in a significant drop in output voltage. For a 12V DC input, the actual output voltage can reach around 19V, although it may exhibit some instability. Despite these limitations, the circuit is suitable for low current applications.

The voltage doubler circuit utilizing the NE555 timer is a straightforward design that leverages the timer's capabilities as an astable multivibrator to generate a square wave signal. This signal controls two transistors, which function as switches to alternately charge capacitors, thereby achieving voltage doubling. The NE555 timer is configured to oscillate at a frequency of approximately 9 kHz, which is suitable for this application.

Transistor Q1 and Q2 serve as the primary switching elements in the circuit. When Q2 is turned on, capacitor C3 charges to the input voltage, establishing a baseline voltage level. Upon switching, when the output from the NE555 goes high, Q1 turns on, allowing capacitor C4 to charge to a higher voltage, which is effectively the sum of the input voltage and the voltage across C3. This results in a doubled output voltage, making the circuit beneficial for applications requiring a higher voltage from a lower voltage source.

The design includes capacitors C3 and C4, which are essential for storing and transferring charge. C3 acts as an initial charge storage element, while C4 serves as the output capacitor that provides the doubled voltage. The circuit's limitation of 50 mA output current is a critical consideration, as exceeding this threshold can lead to a drop in output voltage due to the transistors' inability to handle higher currents effectively.

In practical applications, this voltage doubler circuit is advantageous for powering low-current devices, where the simplicity and compactness of the design can be beneficial. However, users should be aware of the potential instability in the output voltage and the current limitations when designing systems that incorporate this circuit.The circuit diagram of a very simple voltage doubler using NE555 timer is shown here. Here IC NE555 is wired as an astable mutivibrator operating at around 9KHz. The base of the two transistors (Q1 and Q2) is shorted and output of the astable multivibrator (pin 3) is connected to it. When the output of astable multivibrator is low, Q1 will be OFF and Q2 will be ON. The negative terminal of the capacitor C3 will be shorted to ground through T2 and it will be charged to the input supply voltage. When the output of the astable multi vibrator is high, transistor Q1 will be ON and transistor Q2 will be OFF.

The capacitor C4 will be charged to the voltage across capacitor C3 plus the input supply voltage (that is double the input voltage). This is how the circuit works. This voltage doubler circuit can deliver only up to 50mA output current and above that current limit the output voltage will be dramatically reduced.

The actual output voltage will be around 19V for a 12V DC input and also the output voltage will be a bit unstable. Anyway, for low current applications this circuit is well enough. CircuitsToday has introduced an online store where you can buy books that give you a better understanding on the applications of 555 IC.

These books have been reviewed in detail and the links to buy them is also provided. Check it out:- 3 Great Books to Learn 555 Timer Circuits and Projects. 🔗 External reference

The voltage doubler circuit utilizing the NE555 timer is a straightforward design that leverages the timer's capabilities as an astable multivibrator to generate a square wave signal. This signal controls two transistors, which function as switches to alternately charge capacitors, thereby achieving voltage doubling. The NE555 timer is configured to oscillate at a frequency of approximately 9 kHz, which is suitable for this application.

Transistor Q1 and Q2 serve as the primary switching elements in the circuit. When Q2 is turned on, capacitor C3 charges to the input voltage, establishing a baseline voltage level. Upon switching, when the output from the NE555 goes high, Q1 turns on, allowing capacitor C4 to charge to a higher voltage, which is effectively the sum of the input voltage and the voltage across C3. This results in a doubled output voltage, making the circuit beneficial for applications requiring a higher voltage from a lower voltage source.

The design includes capacitors C3 and C4, which are essential for storing and transferring charge. C3 acts as an initial charge storage element, while C4 serves as the output capacitor that provides the doubled voltage. The circuit's limitation of 50 mA output current is a critical consideration, as exceeding this threshold can lead to a drop in output voltage due to the transistors' inability to handle higher currents effectively.

In practical applications, this voltage doubler circuit is advantageous for powering low-current devices, where the simplicity and compactness of the design can be beneficial. However, users should be aware of the potential instability in the output voltage and the current limitations when designing systems that incorporate this circuit.The circuit diagram of a very simple voltage doubler using NE555 timer is shown here. Here IC NE555 is wired as an astable mutivibrator operating at around 9KHz. The base of the two transistors (Q1 and Q2) is shorted and output of the astable multivibrator (pin 3) is connected to it. When the output of astable multivibrator is low, Q1 will be OFF and Q2 will be ON. The negative terminal of the capacitor C3 will be shorted to ground through T2 and it will be charged to the input supply voltage. When the output of the astable multi vibrator is high, transistor Q1 will be ON and transistor Q2 will be OFF.

The capacitor C4 will be charged to the voltage across capacitor C3 plus the input supply voltage (that is double the input voltage). This is how the circuit works. This voltage doubler circuit can deliver only up to 50mA output current and above that current limit the output voltage will be dramatically reduced.

The actual output voltage will be around 19V for a 12V DC input and also the output voltage will be a bit unstable. Anyway, for low current applications this circuit is well enough. CircuitsToday has introduced an online store where you can buy books that give you a better understanding on the applications of 555 IC.

These books have been reviewed in detail and the links to buy them is also provided. Check it out:- 3 Great Books to Learn 555 Timer Circuits and Projects. 🔗 External reference