Voltage Level Detector Circuit

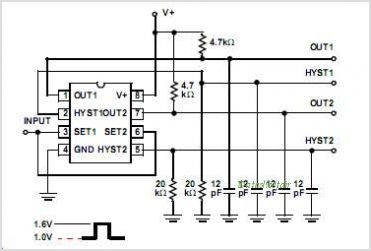

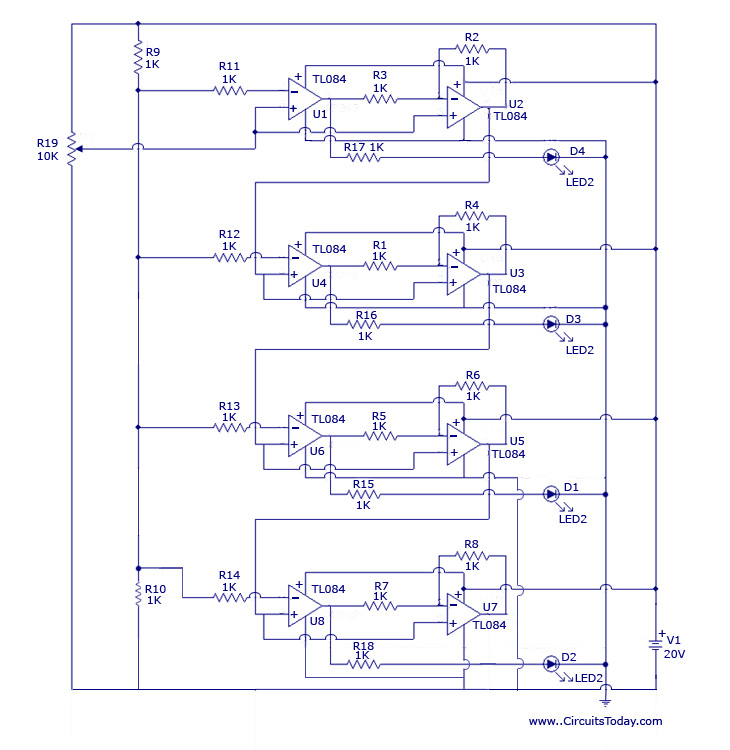

The design originated from the interest in discovering a new technique for analog to digital conversion. The two types of ADC (Analog to Digital Converter) that influenced the development of this circuit are the Flash Type ADC and the Successive Approximation Type ADC. The Flash Type ADC is the fastest available on the market, boasting a maximum sampling rate of 120 Msps; however, it requires a large number of operational amplifiers (OP-AMPs). Conversely, the Successive Approximation Type ADC utilizes fewer components, but its speed is contingent upon the clock frequency supplied to it. A technique that offers a balance between these two was sought, resulting in the development of this circuit. The operation of this circuit is analogous to converting a decimal fraction to a binary fraction. To achieve this, the circuit amplifies an input signal and compares it to a reference voltage. The circuit can be segmented into multiple stages, with the number of stages adjustable as needed. Each stage comprises two OP-AMPs (TL084). One OP-AMP (located on the left) functions as a comparator, while the other OP-AMP (on the right) serves as a non-inverting amplifier with a fixed gain of exactly 2. The input voltage is connected to the non-inverting pin of each OP-AMP. The digital output is derived from the output of the comparator OP-AMP, while the output of the amplifier OP-AMP is directed to the input of the subsequent stage. A reference voltage is established using two resistors. An input voltage is applied, and the comparator OP-AMP assesses the input voltage against the reference level. If the input voltage surpasses the reference level, the comparator output becomes high, and the amplifying OP-AMP performs both amplification and subtraction operations. Conversely, if the input voltage is below the reference voltage, only amplification occurs. The output from the amplifier OP-AMP is forwarded to lower stages. To verify the circuit's functionality, a potentiometer can be employed; its terminals are connected to the battery's poles, and the wiper is linked to the first stage of the circuit. As the potentiometer is adjusted, a binary count can be observed represented by four LEDs, indicating either an upward or downward count. The amplifier's gain must be precisely 2. Any minor error in the higher stages will adversely affect the performance of the lower stages, which is unavoidable since achieving an exact gain of 2 is impractical. Even a four-stage circuit will exhibit some level loss.

The circuit design integrates a multi-stage architecture to facilitate efficient analog-to-digital conversion. Each stage's operational amplifiers are configured to ensure that the signal is accurately amplified and compared against a predetermined reference voltage. The use of TL084 OP-AMPs is notable due to their low noise characteristics and high-speed performance, making them suitable for applications requiring rapid signal processing.

The configuration allows for dynamic adjustment of the number of stages, enabling scalability based on the desired resolution and speed of the ADC. The non-inverting amplifier stage ensures that the signal is amplified without phase inversion, which is critical for maintaining signal integrity throughout the conversion process.

The reference voltage is created using a voltage divider network formed by two resistors, which provides a stable reference point for the comparator. This setup is essential for ensuring accurate comparisons, as any fluctuation in the reference voltage can lead to erroneous digital output.

The binary output is represented by four LEDs, which provide a visual indication of the digital count derived from the analog input. This feature enhances the circuit's usability by allowing real-time monitoring of the conversion process.

Overall, the design represents a thoughtful synthesis of speed and component efficiency, addressing the inherent trade-offs between Flash and Successive Approximation ADCs, while also acknowledging the practical limitations of achieving exact gains in real-world applications.The design came from the interest of finding a new technique of analog to digital conversion. The two types of ADC (Analog to Digital Converter) that inspired me in the development of this circuit are Flash Type ADC and Successive Approximation Type ADC. The Flash Type ADC is the fastest ADC available in the market (highest sampling rate 120 Msps) but it uses a huge number of OP-AMPS. On the other hand Successive Approximation Type ADC uses fewer components but its speed is dependent upon the clock frequency provided to it. I was looking for a technique that can give a trade-off between this two, the result of which is this circuit.

The working of this circuit is similar to that of decimal fraction to binary fraction conversion. For this purpose, the circuit amplifies a signal and compares it to a reference voltage. The circuit can be divided into a number of stages. Number of stages can be increased or decreased according to need. Each stage contains two OP-AMPs(TL084). One of them (OP-AMP at the left side) is used for comparison purpose. The other (OP-AMP at the right side) is used as a non-inverting amplifier with a fixed gain (EXACTLY 2). The input voltage is connected to the non-inverting pin/terminal of each OP-AMP. The digital output is obtained from the output of the comparing OP-AMP and the output of the amplifier OP-AMP is fed to the input of the next stage.

To obtain a reference voltage, two resistors are used. An input voltage is applied. The OP-AMP used as a comparator compares the input voltage with the reference level. If it exceeds a certain reference level, the comparator output goes high and there is amplification along with subtraction operation is performed by the amplifying OP-AMP. If the input voltage is less than the reference voltage, only the amplification operation is performed.

The output of the amplifier OP-AMP is inherited to lower stages. To see if the circuit is working or not, use a potentiometer, connect its two ends to the two poles of the battery, connect the wiper to the first stage of the circuit. Now as the potentiometer is swiped across its range, a count can be observed represented by the four LED`s.

It will be a binary count, either upward or downward. The gain of the amplifier must be 2. Small error in higher stages will deteriorate the performance of lower stages and is un-avoidable since practically a gain, exactly 2 is un-obtainable. Even the 4 stage circuit will show up level loss. 🔗 External reference

The circuit design integrates a multi-stage architecture to facilitate efficient analog-to-digital conversion. Each stage's operational amplifiers are configured to ensure that the signal is accurately amplified and compared against a predetermined reference voltage. The use of TL084 OP-AMPs is notable due to their low noise characteristics and high-speed performance, making them suitable for applications requiring rapid signal processing.

The configuration allows for dynamic adjustment of the number of stages, enabling scalability based on the desired resolution and speed of the ADC. The non-inverting amplifier stage ensures that the signal is amplified without phase inversion, which is critical for maintaining signal integrity throughout the conversion process.

The reference voltage is created using a voltage divider network formed by two resistors, which provides a stable reference point for the comparator. This setup is essential for ensuring accurate comparisons, as any fluctuation in the reference voltage can lead to erroneous digital output.

The binary output is represented by four LEDs, which provide a visual indication of the digital count derived from the analog input. This feature enhances the circuit's usability by allowing real-time monitoring of the conversion process.

Overall, the design represents a thoughtful synthesis of speed and component efficiency, addressing the inherent trade-offs between Flash and Successive Approximation ADCs, while also acknowledging the practical limitations of achieving exact gains in real-world applications.The design came from the interest of finding a new technique of analog to digital conversion. The two types of ADC (Analog to Digital Converter) that inspired me in the development of this circuit are Flash Type ADC and Successive Approximation Type ADC. The Flash Type ADC is the fastest ADC available in the market (highest sampling rate 120 Msps) but it uses a huge number of OP-AMPS. On the other hand Successive Approximation Type ADC uses fewer components but its speed is dependent upon the clock frequency provided to it. I was looking for a technique that can give a trade-off between this two, the result of which is this circuit.

The working of this circuit is similar to that of decimal fraction to binary fraction conversion. For this purpose, the circuit amplifies a signal and compares it to a reference voltage. The circuit can be divided into a number of stages. Number of stages can be increased or decreased according to need. Each stage contains two OP-AMPs(TL084). One of them (OP-AMP at the left side) is used for comparison purpose. The other (OP-AMP at the right side) is used as a non-inverting amplifier with a fixed gain (EXACTLY 2). The input voltage is connected to the non-inverting pin/terminal of each OP-AMP. The digital output is obtained from the output of the comparing OP-AMP and the output of the amplifier OP-AMP is fed to the input of the next stage.

To obtain a reference voltage, two resistors are used. An input voltage is applied. The OP-AMP used as a comparator compares the input voltage with the reference level. If it exceeds a certain reference level, the comparator output goes high and there is amplification along with subtraction operation is performed by the amplifying OP-AMP. If the input voltage is less than the reference voltage, only the amplification operation is performed.

The output of the amplifier OP-AMP is inherited to lower stages. To see if the circuit is working or not, use a potentiometer, connect its two ends to the two poles of the battery, connect the wiper to the first stage of the circuit. Now as the potentiometer is swiped across its range, a count can be observed represented by the four LED`s.

It will be a binary count, either upward or downward. The gain of the amplifier must be 2. Small error in higher stages will deteriorate the performance of lower stages and is un-avoidable since practically a gain, exactly 2 is un-obtainable. Even the 4 stage circuit will show up level loss. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713