1Ghz Divide-By-N Counter

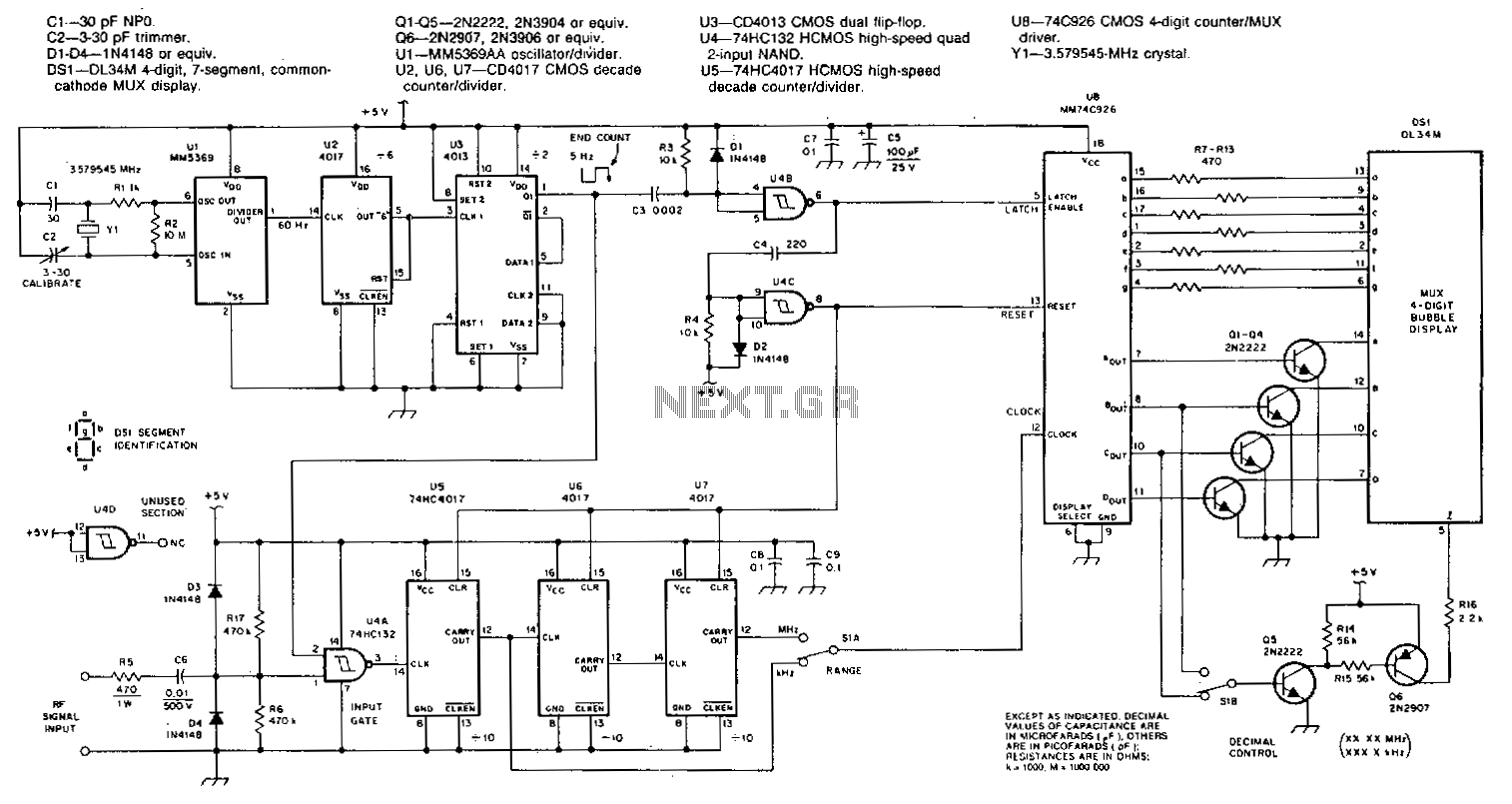

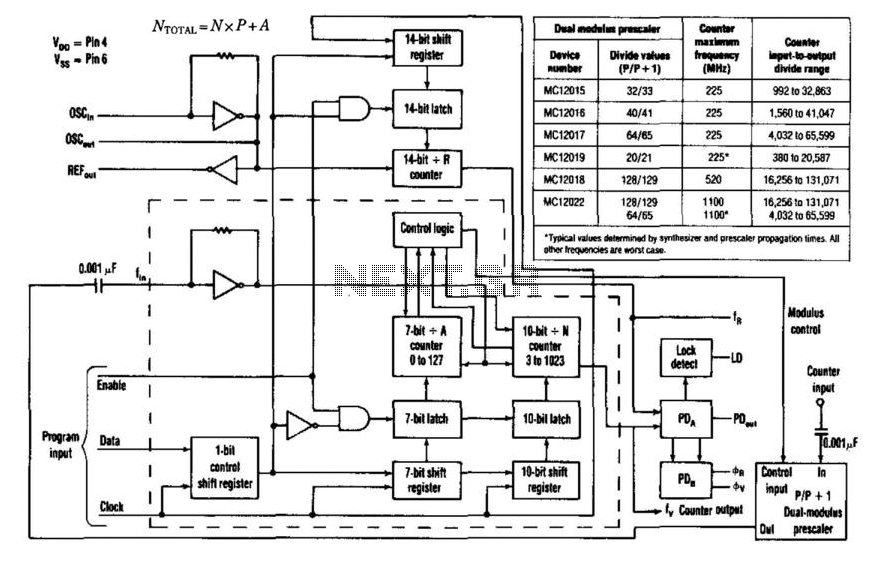

Counter speeds for CMOS and TTL programmable counters are limited to under 100 MHz. ECL-type devices can approach a few hundred MHz but require significant current. However, using the dual-modulus-prescaling technique in conjunction with phase-locked-loop synthesizer chips that control the prescaler can overcome these frequency and power drain limitations. This method allows designers to select various counter programming schemes (serial, parallel, or data bus) while achieving higher frequency capabilities. Low-power devices (under 75 mW) and low-cost options are also available. Furthermore, only two integrated circuits (ICs) are needed to achieve divide values exceeding 131,000. The maximum input frequency and dividing range for the counter are determined by selecting an appropriate 8-pin dual-modulus prescaler. The counter's output is available at the synthesizer pin Fy. The total input-to-output divide value is governed by the equation: Ntotal = NxP + A, where A represents the value programmed through the serial port into the divide-by-jV and divide-by-A counters. The lower dual-modulus value is established by the synthesizer's modulus control signal. Typically, A varies from zero to P-1 to achieve steps within the system's divide range. N must be equal to or greater than A. The condition N > A sets a lower limit on Ntotal, which is dictated by Amax = P - 1.

The described circuit involves a sophisticated approach to counter design that utilizes dual-modulus prescaling in combination with phase-locked-loop (PLL) synthesizers to achieve high-frequency operation while maintaining low power consumption. The dual-modulus prescaler allows for flexible division ratios, enabling the design to adapt to various applications requiring different frequency outputs.

In this configuration, the programmable counter can be set up to operate in multiple modes (serial, parallel, or data bus), providing versatility in how the counter is integrated into larger systems. The use of low-power devices ensures that the overall system remains energy-efficient, making it suitable for battery-operated or power-sensitive applications.

The equation Ntotal = NxP + A is crucial for determining the total division factor, where N represents the programmable division value, P is the modulus of the prescaler, and A is the additional programmable parameter. The choice of the prescaler, which is an 8-pin IC, is essential as it dictates the maximum input frequency and the overall dividing range of the counter.

The output from the counter is made available at the synthesizer pin Fy, which can be interfaced with other components in the system, such as frequency synthesizers or digital signal processors. The design ensures that the counter can handle high-frequency signals while providing a reliable output that meets the specifications of modern electronic systems.

In summary, this circuit design exemplifies the integration of advanced digital techniques to enhance the performance of counters, making it a valuable solution in high-speed and low-power applications. Counter speeds for CMOS- and TTL-programmable counters are limited to under 100 MHz. ECL-type devices can approach a few hundred MHz, but with significant current requirements. However, coupling the dual-modulus-prescaling technique with the available phase-locked-loop synthesizer chips that control the prescaler circumvents these frequency and power-drain constraints. With this approach, designers can also choose various counter-programming schemes (serial, parallel, or data bus), in addition to achieving higher frequency capabilities.

Low-power drain (less than 75 mW) and low-cost devices can also be selected. Moreover, only two ICs are necessary to achieve divide values above 131000. Maximum input frequency and dividing range for the counter are controlled by choosing an appropriate 8-pin dual-modulus prescaler. The counter"s output appears at synthesizer pin Fy (see the figure). The total input-to-output divide value is governed by the equation: Ntotal = NxP+A and A represent the value programmed through the serial port into the divide-by-jV and divide-by-A counters.

is the lower dual-modulus value that is established by the synthesizer"s modulus-control signal. Typically, A varies from zero to P-l to achieve steps within the system"s divide range. must be equal to or greater than A. N>A then sets a lower limit on NT0tal> which is dictated by Amax = P- 1. 🔗 External reference

The described circuit involves a sophisticated approach to counter design that utilizes dual-modulus prescaling in combination with phase-locked-loop (PLL) synthesizers to achieve high-frequency operation while maintaining low power consumption. The dual-modulus prescaler allows for flexible division ratios, enabling the design to adapt to various applications requiring different frequency outputs.

In this configuration, the programmable counter can be set up to operate in multiple modes (serial, parallel, or data bus), providing versatility in how the counter is integrated into larger systems. The use of low-power devices ensures that the overall system remains energy-efficient, making it suitable for battery-operated or power-sensitive applications.

The equation Ntotal = NxP + A is crucial for determining the total division factor, where N represents the programmable division value, P is the modulus of the prescaler, and A is the additional programmable parameter. The choice of the prescaler, which is an 8-pin IC, is essential as it dictates the maximum input frequency and the overall dividing range of the counter.

The output from the counter is made available at the synthesizer pin Fy, which can be interfaced with other components in the system, such as frequency synthesizers or digital signal processors. The design ensures that the counter can handle high-frequency signals while providing a reliable output that meets the specifications of modern electronic systems.

In summary, this circuit design exemplifies the integration of advanced digital techniques to enhance the performance of counters, making it a valuable solution in high-speed and low-power applications. Counter speeds for CMOS- and TTL-programmable counters are limited to under 100 MHz. ECL-type devices can approach a few hundred MHz, but with significant current requirements. However, coupling the dual-modulus-prescaling technique with the available phase-locked-loop synthesizer chips that control the prescaler circumvents these frequency and power-drain constraints. With this approach, designers can also choose various counter-programming schemes (serial, parallel, or data bus), in addition to achieving higher frequency capabilities.

Low-power drain (less than 75 mW) and low-cost devices can also be selected. Moreover, only two ICs are necessary to achieve divide values above 131000. Maximum input frequency and dividing range for the counter are controlled by choosing an appropriate 8-pin dual-modulus prescaler. The counter"s output appears at synthesizer pin Fy (see the figure). The total input-to-output divide value is governed by the equation: Ntotal = NxP+A and A represent the value programmed through the serial port into the divide-by-jV and divide-by-A counters.

is the lower dual-modulus value that is established by the synthesizer"s modulus-control signal. Typically, A varies from zero to P-l to achieve steps within the system"s divide range. must be equal to or greater than A. N>A then sets a lower limit on NT0tal> which is dictated by Amax = P- 1. 🔗 External reference