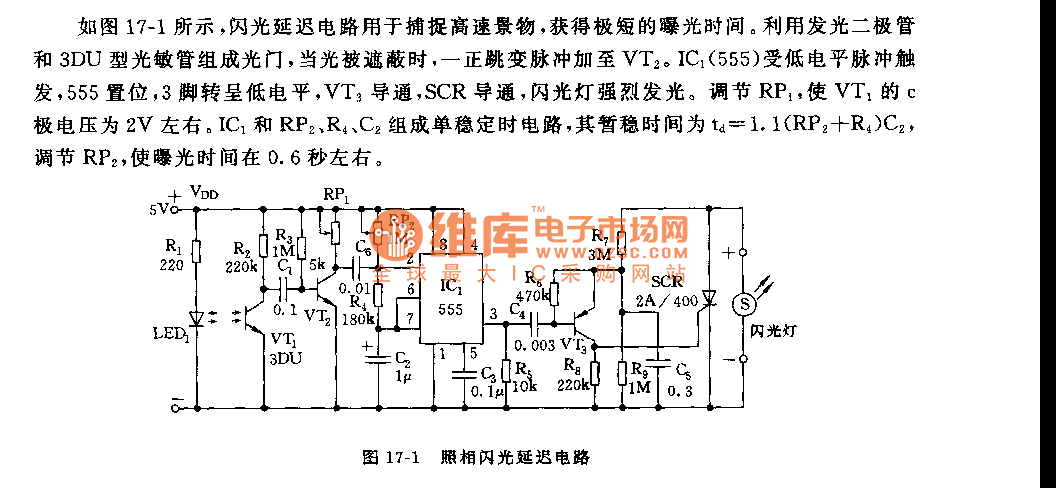

555 camera flash delay circuit

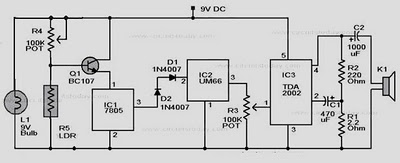

As shown in figure 17-1, the camera flash delay circuit is designed to capture high-speed scenes, allowing for very short exposure times. The light gate consists of a luminous diode and a 3DU type photosensitive tube. When the light is obstructed, a positive transition pulse is applied to VT2. The IC1 (555) is triggered by the low-level pulse.

The camera flash delay circuit utilizes a light gate mechanism to accurately time the activation of the camera flash during rapid events. The luminous diode emits light that is detected by the 3DU photosensitive tube. In normal conditions, the photosensitive tube remains conductive, allowing current to flow through the circuit. However, when an object passes through the light beam, it casts a shadow on the photosensitive tube, leading to a sudden change in its conductivity.

This change generates a positive transition pulse that is sent to a transistor (VT2), which acts as a switching element in the circuit. The pulse triggers the 555 timer IC (IC1), configured in a monostable mode. Upon receiving the low-level pulse, the 555 timer initiates a timing cycle, which determines the duration of the flash. The output pulse from the 555 timer controls the flash mechanism, ensuring that the flash is activated for a very short duration, suitable for freezing motion in high-speed photography.

The circuit may also include additional components such as resistors and capacitors to fine-tune the timing characteristics and ensure proper operation of the 555 timer. The design allows for adjustments to be made, enabling the user to optimize the exposure time based on specific lighting conditions and the speed of the subject being photographed. Overall, this camera flash delay circuit is an effective solution for capturing fleeting moments with precision and clarity.As the figure 17-1 showns, the camera flash delay circuit can be used to capture the high-speed scene, and you can get a very short exposure time. The light door is composed of the luminous diode and the 3DU type photosensitive tube. When the light is shadowed, the positive transition pulse adds to the VT2. The IC1(555) is triggered by the low-level pulse, 5.. 🔗 External reference

The camera flash delay circuit utilizes a light gate mechanism to accurately time the activation of the camera flash during rapid events. The luminous diode emits light that is detected by the 3DU photosensitive tube. In normal conditions, the photosensitive tube remains conductive, allowing current to flow through the circuit. However, when an object passes through the light beam, it casts a shadow on the photosensitive tube, leading to a sudden change in its conductivity.

This change generates a positive transition pulse that is sent to a transistor (VT2), which acts as a switching element in the circuit. The pulse triggers the 555 timer IC (IC1), configured in a monostable mode. Upon receiving the low-level pulse, the 555 timer initiates a timing cycle, which determines the duration of the flash. The output pulse from the 555 timer controls the flash mechanism, ensuring that the flash is activated for a very short duration, suitable for freezing motion in high-speed photography.

The circuit may also include additional components such as resistors and capacitors to fine-tune the timing characteristics and ensure proper operation of the 555 timer. The design allows for adjustments to be made, enabling the user to optimize the exposure time based on specific lighting conditions and the speed of the subject being photographed. Overall, this camera flash delay circuit is an effective solution for capturing fleeting moments with precision and clarity.As the figure 17-1 showns, the camera flash delay circuit can be used to capture the high-speed scene, and you can get a very short exposure time. The light door is composed of the luminous diode and the 3DU type photosensitive tube. When the light is shadowed, the positive transition pulse adds to the VT2. The IC1(555) is triggered by the low-level pulse, 5.. 🔗 External reference