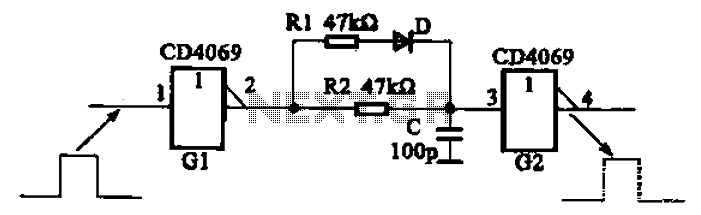

And broadening the delay circuit

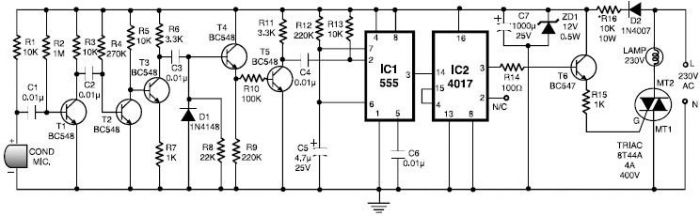

The inverter circuit using CD4069 is configured with a delay and width adjustment. When the output of the inverter (G1) is high, the capacitor (C) charges through resistor (R1) and diode (D). The voltage across capacitor C quickly reaches the threshold level at the input of G2. When the output of G1 goes low, capacitor C discharges through resistor R2 to the output terminal of G1, resulting in a low-level output. The discharge time of C is ten times that of the charging time due to the ratio of R2 to R1, thus creating a delayed output pulse and widening the pulse at G2.

The described circuit utilizes a CD4069 hex inverter to implement a delay and pulse width modulation functionality. The configuration consists of two main stages: the charging and discharging phases of the capacitor C, which are influenced by the resistors R1 and R2.

In the charging phase, when the output of inverter G1 is high, the capacitor C charges through the resistor R1 and the diode D. The diode ensures that current flows in one direction, allowing the capacitor to charge efficiently. The rate at which the capacitor charges is determined by the RC time constant, τ = R1 * C. The voltage across the capacitor rises exponentially until it reaches the threshold voltage of the next inverter stage, G2.

When the output of G1 transitions to a low state, the capacitor C begins to discharge through resistor R2. The discharge rate is governed by the time constant τ = R2 * C. Given that R2 is set to be ten times the value of R1, the discharge time becomes significantly longer than the charging time. This results in a delayed output pulse at G2, which effectively widens the output pulse compared to the input signal.

This configuration is particularly useful in applications where pulse width modulation or timing adjustments are necessary, such as in signal processing, timer circuits, or digital logic applications. The selection of resistor and capacitor values allows for customization of the delay and width of the output pulse, making the circuit versatile for various electronic designs. By inverter Gl, delay and width morning circuit 02 (CD4069) and RC integrating circuit configuration shown. When not gate output high when OI, C capacitor through Rl, D charge, C voltage quickly filled to G2 input threshold level. When Gl output low, C through R2 to the output terminal Gl of low level discharge, due R2-10Rl, therefore, C discharge time is 10 times the charging time. Therefore, the output pulse is delayed while G2 is widened.

The described circuit utilizes a CD4069 hex inverter to implement a delay and pulse width modulation functionality. The configuration consists of two main stages: the charging and discharging phases of the capacitor C, which are influenced by the resistors R1 and R2.

In the charging phase, when the output of inverter G1 is high, the capacitor C charges through the resistor R1 and the diode D. The diode ensures that current flows in one direction, allowing the capacitor to charge efficiently. The rate at which the capacitor charges is determined by the RC time constant, τ = R1 * C. The voltage across the capacitor rises exponentially until it reaches the threshold voltage of the next inverter stage, G2.

When the output of G1 transitions to a low state, the capacitor C begins to discharge through resistor R2. The discharge rate is governed by the time constant τ = R2 * C. Given that R2 is set to be ten times the value of R1, the discharge time becomes significantly longer than the charging time. This results in a delayed output pulse at G2, which effectively widens the output pulse compared to the input signal.

This configuration is particularly useful in applications where pulse width modulation or timing adjustments are necessary, such as in signal processing, timer circuits, or digital logic applications. The selection of resistor and capacitor values allows for customization of the delay and width of the output pulse, making the circuit versatile for various electronic designs. By inverter Gl, delay and width morning circuit 02 (CD4069) and RC integrating circuit configuration shown. When not gate output high when OI, C capacitor through Rl, D charge, C voltage quickly filled to G2 input threshold level. When Gl output low, C through R2 to the output terminal Gl of low level discharge, due R2-10Rl, therefore, C discharge time is 10 times the charging time. Therefore, the output pulse is delayed while G2 is widened.

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713