Butler emitter follower oscillator 100Mhz

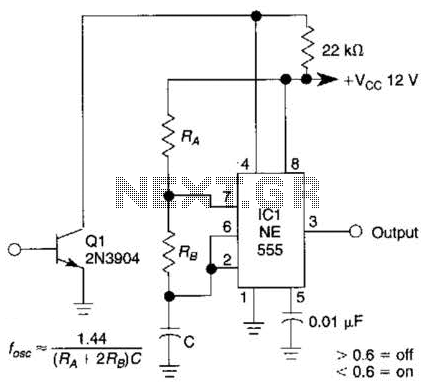

This circuit exhibits good performance without an amplifier, having a gain of only one, with built-in parasitics due to the emitter follower negative feedback. Additionally, it serves to stabilize its gain.

The circuit under discussion utilizes an emitter follower configuration, which is a type of transistor amplifier that provides voltage gain close to unity (1). The primary function of this configuration is to buffer the input signal, ensuring that the output can drive a load without significantly affecting the input signal's voltage.

In this design, the emitter follower employs negative feedback, which plays a crucial role in stabilizing the gain. Negative feedback occurs when a portion of the output signal is fed back to the input in a manner that opposes the input signal. This process helps to minimize the effects of any parasitic elements that may arise from the circuit components, thereby enhancing the overall performance and reliability of the circuit.

The emitter follower configuration typically consists of a bipolar junction transistor (BJT) or a field-effect transistor (FET) with its emitter (or source) connected to the output. The base (or gate) receives the input signal, while the collector (or drain) is connected to the power supply. The output is taken from the emitter (or source), which provides a low output impedance, making it suitable for driving capacitive loads or other stages in a circuit.

In summary, this circuit achieves effective signal buffering with a gain of one while utilizing negative feedback to stabilize performance and mitigate the impact of parasitic elements. This design is particularly useful in applications where signal integrity and stability are paramount, such as in audio processing, sensor interfacing, and other analog signal conditioning tasks.This circuit has good performance without amplifier has a gain of only one with built-in any parasitics because emitter follower negative feedback to stabilize its gain.

The circuit under discussion utilizes an emitter follower configuration, which is a type of transistor amplifier that provides voltage gain close to unity (1). The primary function of this configuration is to buffer the input signal, ensuring that the output can drive a load without significantly affecting the input signal's voltage.

In this design, the emitter follower employs negative feedback, which plays a crucial role in stabilizing the gain. Negative feedback occurs when a portion of the output signal is fed back to the input in a manner that opposes the input signal. This process helps to minimize the effects of any parasitic elements that may arise from the circuit components, thereby enhancing the overall performance and reliability of the circuit.

The emitter follower configuration typically consists of a bipolar junction transistor (BJT) or a field-effect transistor (FET) with its emitter (or source) connected to the output. The base (or gate) receives the input signal, while the collector (or drain) is connected to the power supply. The output is taken from the emitter (or source), which provides a low output impedance, making it suitable for driving capacitive loads or other stages in a circuit.

In summary, this circuit achieves effective signal buffering with a gain of one while utilizing negative feedback to stabilize performance and mitigate the impact of parasitic elements. This design is particularly useful in applications where signal integrity and stability are paramount, such as in audio processing, sensor interfacing, and other analog signal conditioning tasks.This circuit has good performance without amplifier has a gain of only one with built-in any parasitics because emitter follower negative feedback to stabilize its gain.