DDR memory power supply circuit

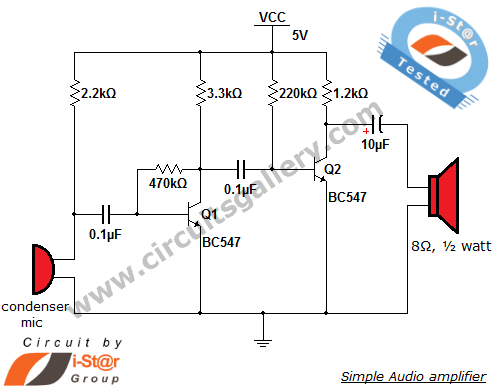

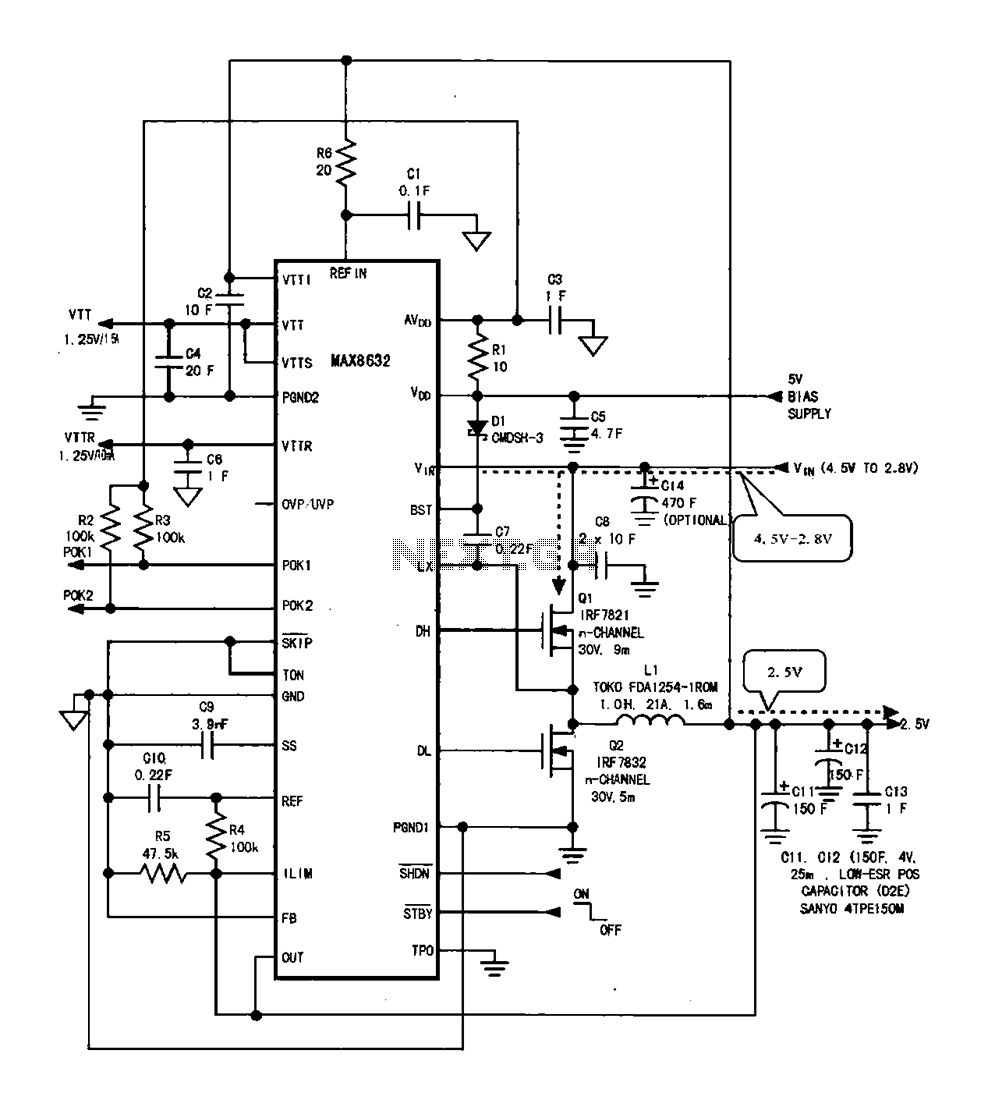

DDR memory power supply circuit. This circuit illustrates the power supply configuration for notebook DDR memory, utilizing the MAX8632 power control circuit chip. The power supply terminal VDD is connected to the voltage detection point 1. The battery DC supply voltage ranges from 4.5 V to 2.8 V. The switching voltage is applied to the drain of the field effect transistor Q1, while the DH and DL outputs of the control chip generate PWM pulse signals that are out of phase. These signals are directed to the gates of transistors Q1 and Q2. As a result of the PWM pulse action, Q1 and Q2 operate alternately, converting the DC battery voltage into a switching voltage. This voltage is then processed through an LC filter to yield an output voltage of 2.5 V for the memory circuitry.

The DDR memory power supply circuit is designed to efficiently convert a variable DC battery voltage into a stable output voltage suitable for DDR memory operation. The MAX8632 chip serves as the core component of the power control circuit, managing the power supply by generating pulse-width modulation (PWM) signals. These PWM signals are crucial for controlling the switching action of the field effect transistors Q1 and Q2, which are configured in a push-pull arrangement.

The operation begins with the detection of the battery voltage, which can range from 4.5 V to 2.8 V. This range is essential for ensuring compatibility with various battery types and states of charge. The MAX8632 monitors this voltage and adjusts the PWM signals accordingly to maintain the desired output voltage. The switching voltage applied to the drain of Q1 allows for the modulation of the input battery voltage.

Transistors Q1 and Q2 are key components in this circuit, as they alternately conduct based on the PWM signals they receive. When Q1 is turned on, it allows current to flow from the battery through the load, while Q2 is turned off, and vice versa. This complementary operation ensures that the output voltage remains stable despite variations in the input voltage or load conditions.

The LC filter, composed of an inductor (L) and a capacitor (C), smooths the PWM output to produce a consistent 2.5 V output. This filtered voltage is crucial for the reliable operation of DDR memory, which requires a stable power supply to function correctly. The design of the LC filter is critical, as it must effectively reduce ripple voltage while maintaining efficiency.

Overall, this DDR memory power supply circuit exemplifies a robust design that efficiently converts battery voltage to a suitable level for memory applications, ensuring reliable performance in notebook devices.DDR memory power supply circuit Shows the notebook DDR memory power supply circuit, the power control circuit chip MAX8632, the chip power supply terminal VDD is Sv (detection point 1), the battery DC supply voltage between 4.5 V-2.8 V, the the switching voltage is applied to the field effect transistor Ql drain power supply control chip DH, DL outputs a PWM pulse of opposite phase signals, which signals are applied to Ql, Q2 of the gate, under the action of the PWM pulse Q1, Q2 alternately working, the DC voltage of the battery becomes switching voltage, and then after the LC filter output voltage of 2.V for the memory circuitry.

The DDR memory power supply circuit is designed to efficiently convert a variable DC battery voltage into a stable output voltage suitable for DDR memory operation. The MAX8632 chip serves as the core component of the power control circuit, managing the power supply by generating pulse-width modulation (PWM) signals. These PWM signals are crucial for controlling the switching action of the field effect transistors Q1 and Q2, which are configured in a push-pull arrangement.

The operation begins with the detection of the battery voltage, which can range from 4.5 V to 2.8 V. This range is essential for ensuring compatibility with various battery types and states of charge. The MAX8632 monitors this voltage and adjusts the PWM signals accordingly to maintain the desired output voltage. The switching voltage applied to the drain of Q1 allows for the modulation of the input battery voltage.

Transistors Q1 and Q2 are key components in this circuit, as they alternately conduct based on the PWM signals they receive. When Q1 is turned on, it allows current to flow from the battery through the load, while Q2 is turned off, and vice versa. This complementary operation ensures that the output voltage remains stable despite variations in the input voltage or load conditions.

The LC filter, composed of an inductor (L) and a capacitor (C), smooths the PWM output to produce a consistent 2.5 V output. This filtered voltage is crucial for the reliable operation of DDR memory, which requires a stable power supply to function correctly. The design of the LC filter is critical, as it must effectively reduce ripple voltage while maintaining efficiency.

Overall, this DDR memory power supply circuit exemplifies a robust design that efficiently converts battery voltage to a suitable level for memory applications, ensuring reliable performance in notebook devices.DDR memory power supply circuit Shows the notebook DDR memory power supply circuit, the power control circuit chip MAX8632, the chip power supply terminal VDD is Sv (detection point 1), the battery DC supply voltage between 4.5 V-2.8 V, the the switching voltage is applied to the field effect transistor Ql drain power supply control chip DH, DL outputs a PWM pulse of opposite phase signals, which signals are applied to Ql, Q2 of the gate, under the action of the PWM pulse Q1, Q2 alternately working, the DC voltage of the battery becomes switching voltage, and then after the LC filter output voltage of 2.V for the memory circuitry.

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713