DECL Documentation

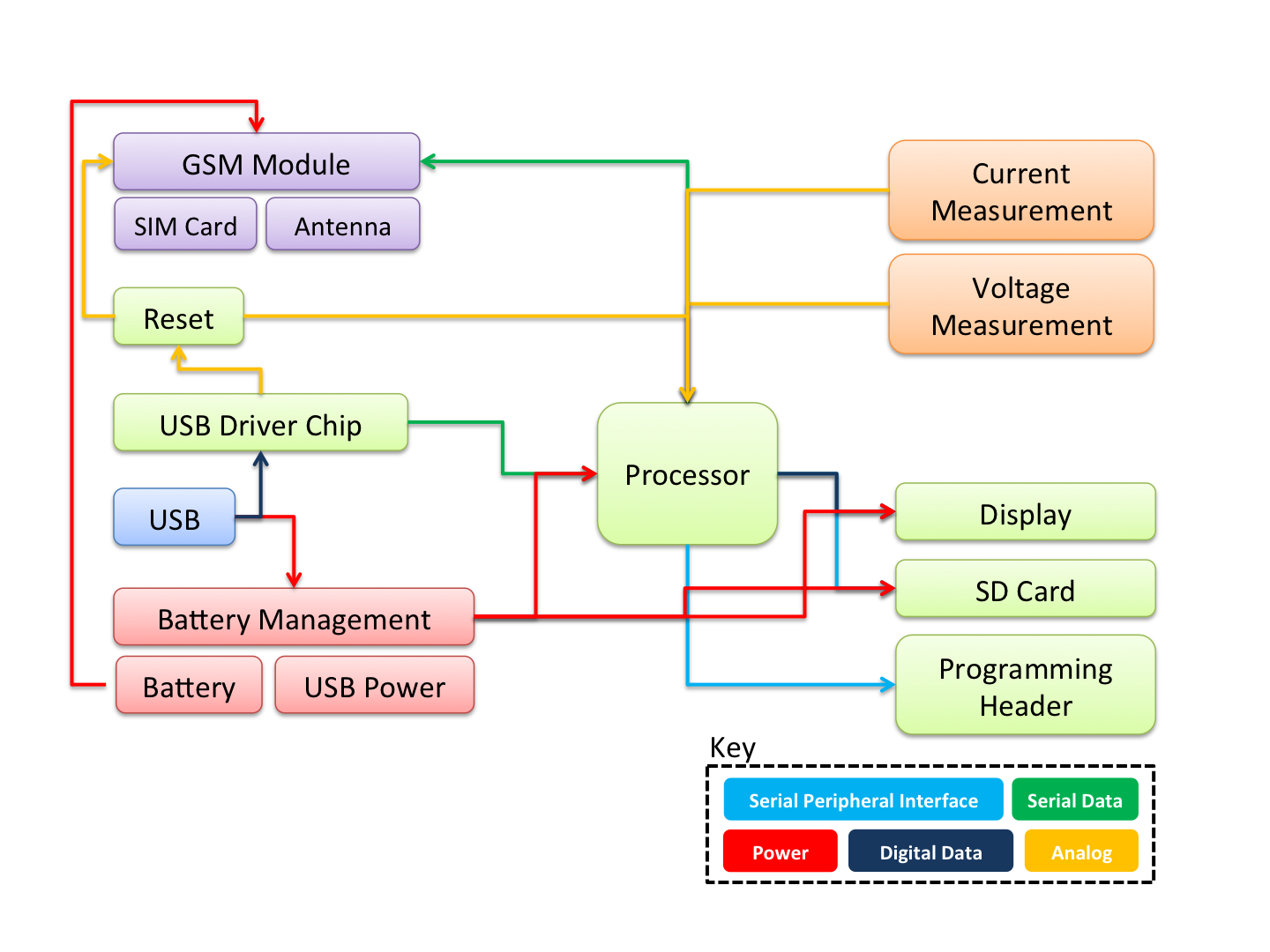

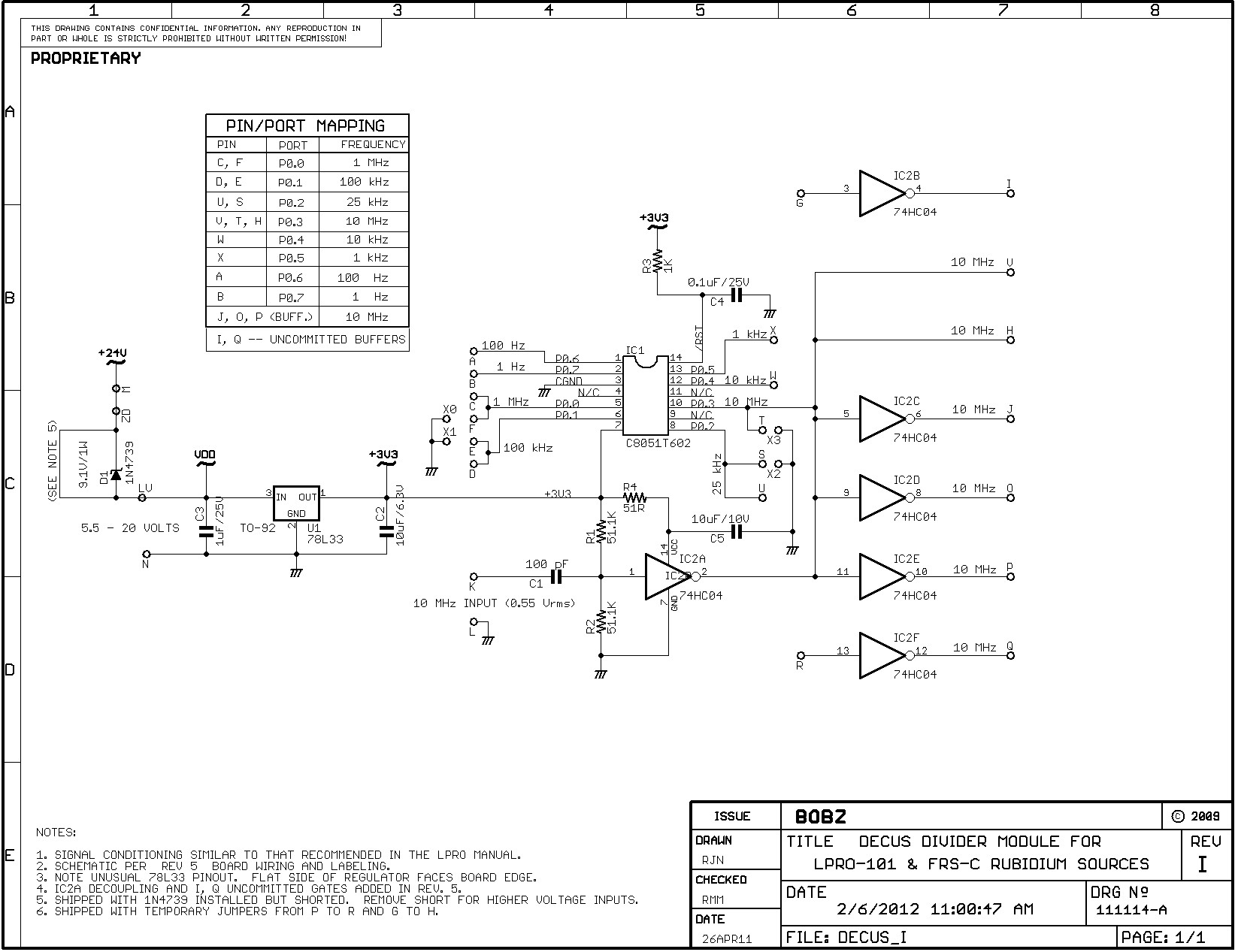

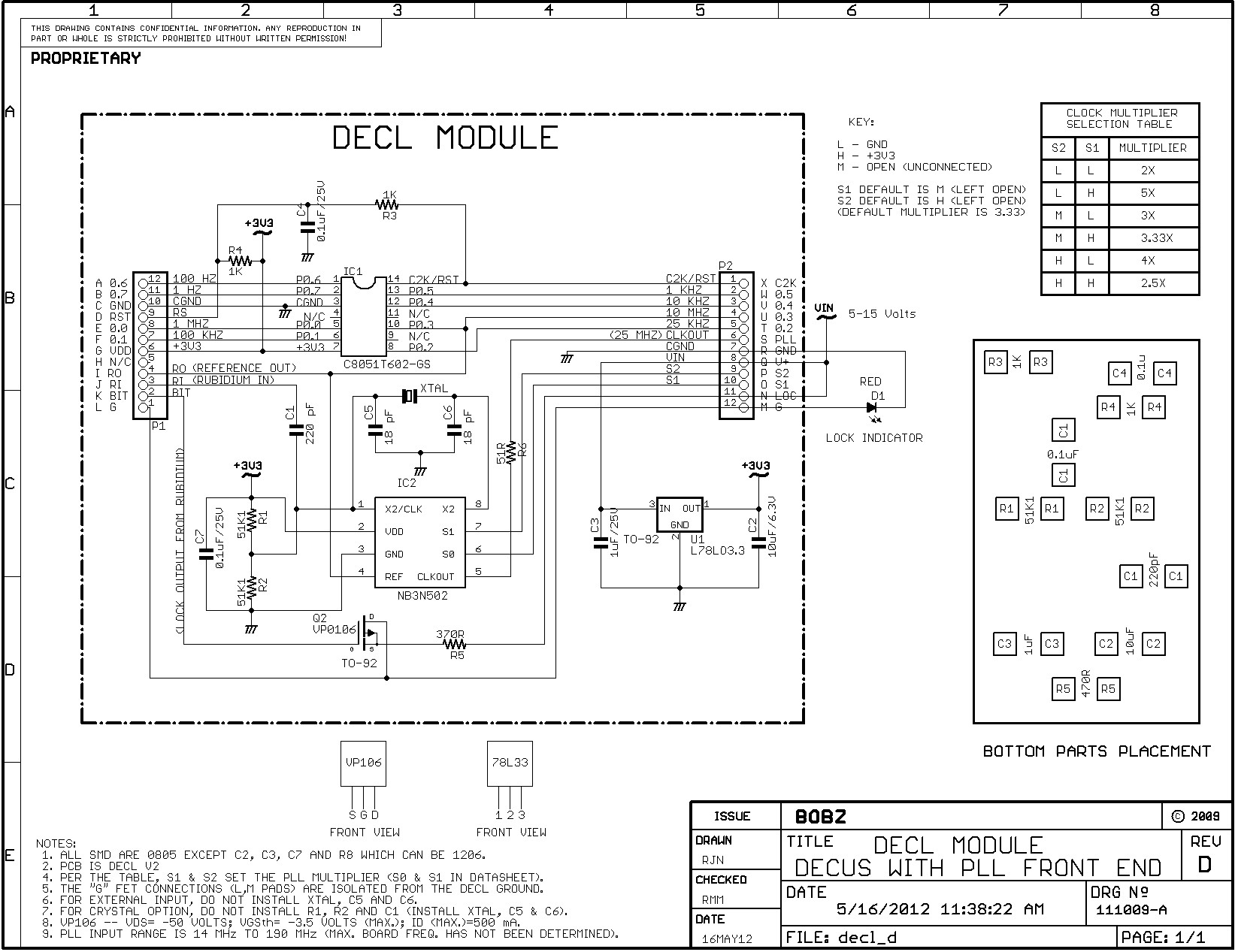

The following describes the design, construction, operation, and use of the DECL (Decade PLL) module. The module incorporates a Phase Locked Loop (PLL) frequency multiplier and a frequency divider to generate various output frequencies based on an input reference frequency. Its primary function is to condition a 10 MHz signal from a reference oscillator, producing divided and multiplied outputs that are synchronized to this reference. The DECL module utilizes two integrated circuits: a PLL chip and a microprocessor chip, which convert the rubidium input signal to a logic level and perform multiplication and division to yield multiple frequency outputs related to the reference. The PLL chip conditions the input signal to provide a buffered, logic-level output that also serves as the clock input for the microprocessor. The PLL generates a multiplied output, typically at 25 MHz, for stable phase-locked output derived from the input reference frequency. The microprocessor processes the buffered output of the reference signal, dividing it to create marker signals at various frequencies ranging from 1 MHz to 1 Hz. The microprocessor and its firmware are consistent with those used in the DECUS decade divider module. The schematic illustrates the components, circuitry, and operational details for the module, including a table for PLL jumper options and bottom-side component placement for the DECL PC Board. The parts list provides additional details about the components used in the module assembly. The module measures approximately 1.25 by 0.875 inches (32 by 23 mm), the same size as the DECUS module. Signal connections are available on two 12-pin single-row pin headers labeled "A" to "X" for easy reference and function identification (e.g., "06" for P0.6). Header pins are spaced 0.1 inches apart, with header rows spaced 0.6 inches apart, facilitating use with breadboard sockets or wired in-line sockets on a prototyping board. However, it should be noted that the inter-pin capacitance of breadboarding sockets may distort some higher frequency outputs, particularly those from the PLL with higher multipliers (e.g., 5). The module also provides a 10 MHz conditioned output and a frequency-multiplied output from the PLL chip, which is typically 33.33 MHz when the option pins are left open (factory default). Users may wire option pins "O" and "P" high to achieve a 25 MHz reference output. With a 10 MHz input from a frequency reference, the multiplied output can range from 20 MHz (2X) to 50 MHz (5X) by configuring the option pins "O" and "P" according to the PLL Multiplier table in the schematic. The DECL module includes a footprint for a P-channel MOSFET, which can be utilized to drive an LED, serving as an indicator that the rubidium reference source is locked. As depicted in Schematic 1, the LED drive connects to the MOSFET gate at module pin "K" (BIT), while the indicator LED connects between module pin "M" and ground (in "R"). Pin "N" (LOC) must be connected to the power supply input voltage. A footprint for an LED current limit resistor, R5, is provided on the module, typically set at 180 Ohms to allow approximately 10 milliamperes through a red LED (assuming a 5 Volt module input). The location of this resistor is indicated on the schematic's component placement diagram for easy identification and adjustment. The divider outputs are driven by microprocessor port pins capable of sourcing or sinking up to 100 milliamperes (100 mA) each, allowing the 1 Hz output to directly drive an LED as an "active" indicator. Drive capabilities are limited by the chosen input voltage and the current limitations of the regulator, as noted in the Power section.

The DECL module is designed for versatility in frequency generation, making it suitable for various applications in signal processing, testing, and communication systems. The integration of the PLL and microprocessor allows for precise control over output frequencies, with the ability to easily modify the configuration through jumper settings. The compact size of the module enhances its usability in space-constrained environments, while the clearly labeled pin headers facilitate straightforward integration into larger systems. The inclusion of an LED indicator enhances user feedback regarding the operational status of the module, providing a visual confirmation of the lock condition of the rubidium reference source. Overall, the DECL module exemplifies a robust solution for frequency manipulation, suitable for both experimental and practical implementations in electronic design.The following describes the design, construction, operation and use of the DECL (Decade PLL) module. The module has both a Phase Locked Loop (PLL) frequency multiplier and a frequency divider to produce various output frequencies that are based on an input reference frequency. The primary use of the module is to condition the ten megahertz (10 MHz ) signal from a reference oscillator and produce divided and multiplied outputs synchronized to the reference. The DECL module uses two chips, a PLL chip and a microprocessor chip, to convert the rubidium input signal to a logic level and multiply and divide that signal to provide multiple frequency outputs that are related to the reference.

The PLL chip conditions the input signal to provide a buffered, logic-level output. This output also drives the microprocessor clock input. The PLL provides a multiplied output, typically 25 MHz, for use as a stable phase-locked output that is derived from the input reference frequency. The microprocessor takes the buffered output of the reference signal and divides it to produce marker signals at various frequencies from 1 MHz to 1 Hertz.

The microprocessor and its code are the same as used for the DECUS decade divider module. The schematic shows the components, circuitry and some operational information for the module. For example, the schematic includes a table for PLL jumper options and bottom-side component placement for the DECL PC Board. The Parts List provides additional information about the components used to assemble the module. Photo 1, the module measures approximately 1 1/4 by 7/8 inches (32 by 23 mm). This is the same size as the the DECUS module. Signal connections are provided on two 12-pin single-row pin headers. The header connections are labeled "A" to "X" for easy reference. The connections are also labeled according to function (e. g. , "06" for P0. 6). Header pins are spaced one tenth of an inch apart and the header rows are spaced 0. 6 inch apart. This allows the module to be used with breadboard sockets or wired with in-line sockets on a prototyping board.

Note that the inter-pin capacitance of breadboarding sockets can distort some higher frequency outputs, especially PLL outputs with higher multipliers (e. g. , 5). outputs, ranging from one Hertz to one megahertz (MHz). The module also provides a 10 MHz conditioned output and a frequency-multiplied outptut from the PLL chip.

The multiplied output is 33. 33 MHz when the option pins are left open (factory default). Users will typically want to wire option pins "O" and "P" high to produce a 25 MHz reference output. With a 10 MHz input from a frequency reference, the multiplied output can range from 20 MHz (2X) to 50 MHz (5X) by wiring the option pins "O" and "P" according to the PLL Multiplier table in the schematic. The DECL module includes a footprint for a P-channel MOSFET that can be wired to drive an LED. For example this can be used to indicate that a rubidium reference source is locked. As shown in Schematic 1, the LED drive connects to the MOSFET gate at module pin "K" (BIT) and the indicator LED connects between module pin "M" and ground (in "R").

Pin "N" (LOC) must also be wired to the power supply input voltage. A footprint for a LED current limit resistor, R5, is provided on the module. This is typically 180 Ohms to provide approximately 10 milliamperes through a red LED (assuming a 5 Volt module input). The location of this resistor is marked on the schematic`s component placement diagram so that it can be easily identified and adjusted.

The divider outputs are driven by microprocessor port pins capable of sourcing or sinking up to 100 milliamperes (100 mA) each. Thus, the one Hertz output can directly drive an LED to act as an "active" indicator. These drive capabilities are limited by the choice of input voltage and the current limitations of the regulator, as noted in the Power section.

The outp 🔗 External reference

The DECL module is designed for versatility in frequency generation, making it suitable for various applications in signal processing, testing, and communication systems. The integration of the PLL and microprocessor allows for precise control over output frequencies, with the ability to easily modify the configuration through jumper settings. The compact size of the module enhances its usability in space-constrained environments, while the clearly labeled pin headers facilitate straightforward integration into larger systems. The inclusion of an LED indicator enhances user feedback regarding the operational status of the module, providing a visual confirmation of the lock condition of the rubidium reference source. Overall, the DECL module exemplifies a robust solution for frequency manipulation, suitable for both experimental and practical implementations in electronic design.The following describes the design, construction, operation and use of the DECL (Decade PLL) module. The module has both a Phase Locked Loop (PLL) frequency multiplier and a frequency divider to produce various output frequencies that are based on an input reference frequency. The primary use of the module is to condition the ten megahertz (10 MHz ) signal from a reference oscillator and produce divided and multiplied outputs synchronized to the reference. The DECL module uses two chips, a PLL chip and a microprocessor chip, to convert the rubidium input signal to a logic level and multiply and divide that signal to provide multiple frequency outputs that are related to the reference.

The PLL chip conditions the input signal to provide a buffered, logic-level output. This output also drives the microprocessor clock input. The PLL provides a multiplied output, typically 25 MHz, for use as a stable phase-locked output that is derived from the input reference frequency. The microprocessor takes the buffered output of the reference signal and divides it to produce marker signals at various frequencies from 1 MHz to 1 Hertz.

The microprocessor and its code are the same as used for the DECUS decade divider module. The schematic shows the components, circuitry and some operational information for the module. For example, the schematic includes a table for PLL jumper options and bottom-side component placement for the DECL PC Board. The Parts List provides additional information about the components used to assemble the module. Photo 1, the module measures approximately 1 1/4 by 7/8 inches (32 by 23 mm). This is the same size as the the DECUS module. Signal connections are provided on two 12-pin single-row pin headers. The header connections are labeled "A" to "X" for easy reference. The connections are also labeled according to function (e. g. , "06" for P0. 6). Header pins are spaced one tenth of an inch apart and the header rows are spaced 0. 6 inch apart. This allows the module to be used with breadboard sockets or wired with in-line sockets on a prototyping board.

Note that the inter-pin capacitance of breadboarding sockets can distort some higher frequency outputs, especially PLL outputs with higher multipliers (e. g. , 5). outputs, ranging from one Hertz to one megahertz (MHz). The module also provides a 10 MHz conditioned output and a frequency-multiplied outptut from the PLL chip.

The multiplied output is 33. 33 MHz when the option pins are left open (factory default). Users will typically want to wire option pins "O" and "P" high to produce a 25 MHz reference output. With a 10 MHz input from a frequency reference, the multiplied output can range from 20 MHz (2X) to 50 MHz (5X) by wiring the option pins "O" and "P" according to the PLL Multiplier table in the schematic. The DECL module includes a footprint for a P-channel MOSFET that can be wired to drive an LED. For example this can be used to indicate that a rubidium reference source is locked. As shown in Schematic 1, the LED drive connects to the MOSFET gate at module pin "K" (BIT) and the indicator LED connects between module pin "M" and ground (in "R").

Pin "N" (LOC) must also be wired to the power supply input voltage. A footprint for a LED current limit resistor, R5, is provided on the module. This is typically 180 Ohms to provide approximately 10 milliamperes through a red LED (assuming a 5 Volt module input). The location of this resistor is marked on the schematic`s component placement diagram so that it can be easily identified and adjusted.

The divider outputs are driven by microprocessor port pins capable of sourcing or sinking up to 100 milliamperes (100 mA) each. Thus, the one Hertz output can directly drive an LED to act as an "active" indicator. These drive capabilities are limited by the choice of input voltage and the current limitations of the regulator, as noted in the Power section.

The outp 🔗 External reference