DECUS Documentation

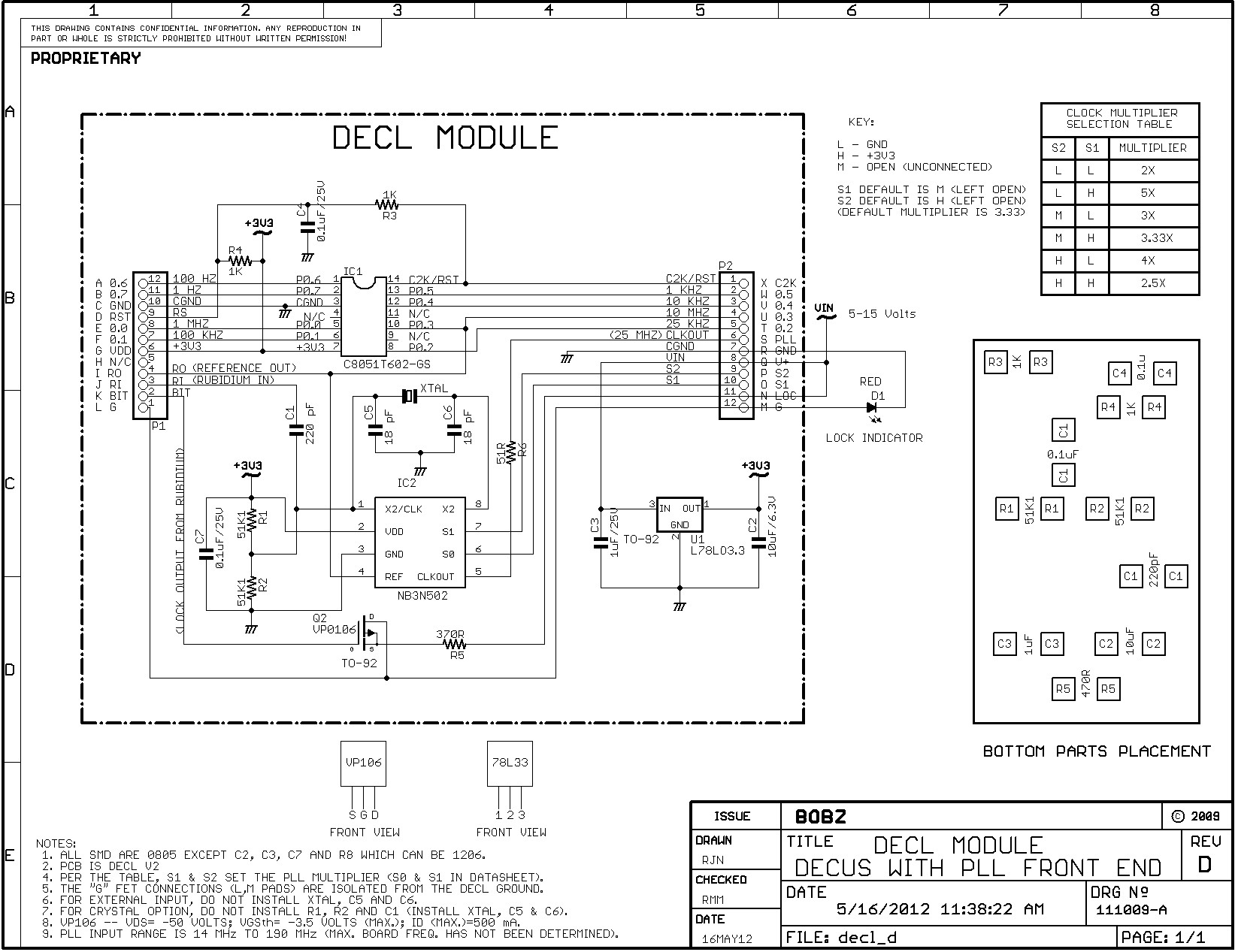

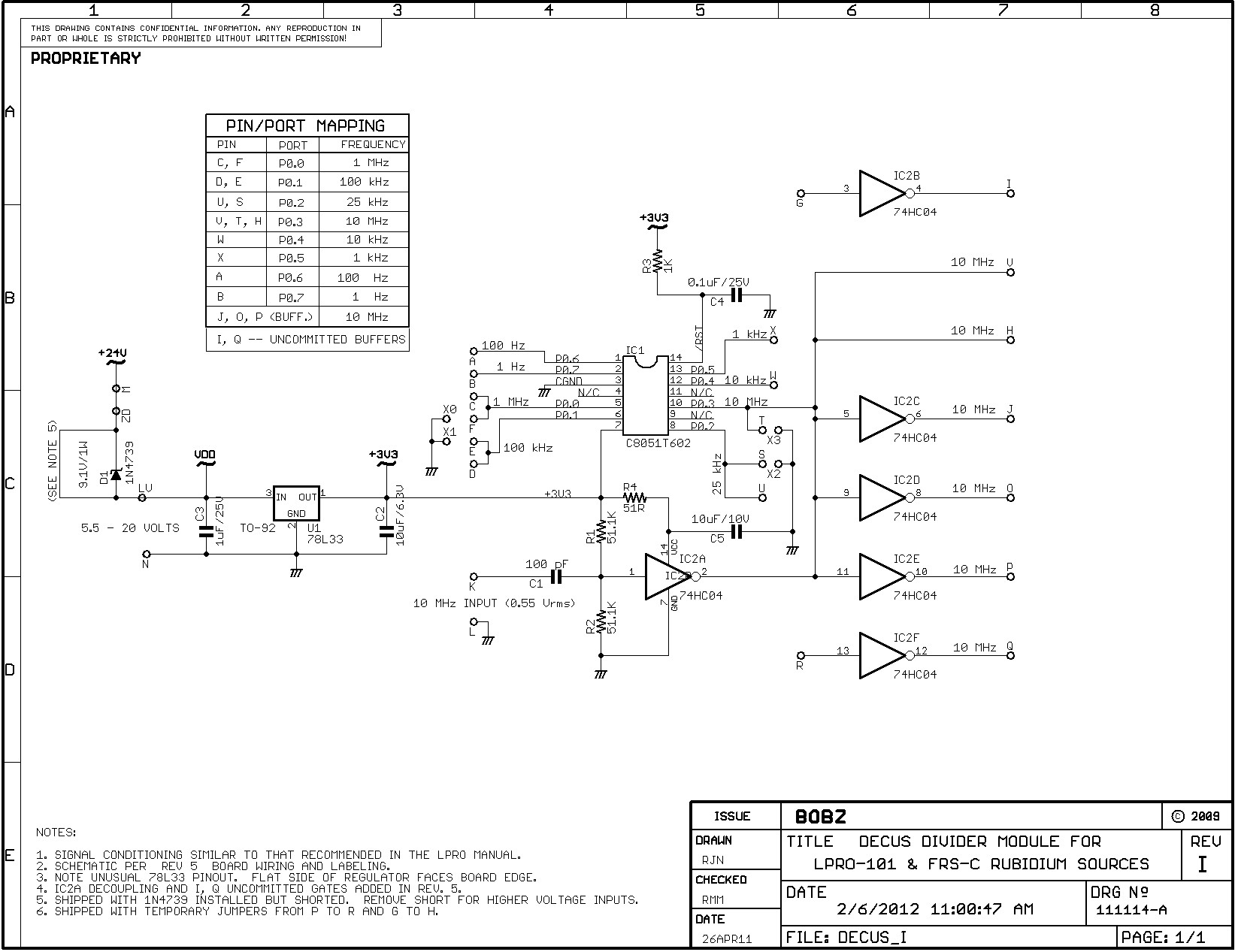

The following outlines the design, construction, operation, and use of the DECUS divider module. A top view of the module is depicted in Photo 2, while Photo 3 illustrates the bottom. The primary function of the module is to condition the 10 megahertz (MHz) signal from rubidium oscillators such as the LPRO-101 or FRS-C units manufactured by EFRATOM Ball, Inc. The DECUS module divides the 10 MHz output from these units to generate marker signals at various frequencies. For those requiring a multiplied frequency output alongside the decade divisor, the DECL module may be of interest. Additionally, users with a FE-5680 rubidium reference may find the FEBO module relevant. The module's conditioning circuit and divider chip can also serve other applications that necessitate signal conditioning and division, though these applications fall outside the scope of this document. The schematic provides details on the components, circuitry, and certain operational constraints of the module. The Parts List offers further information regarding the components utilized in the assembly of the module. The module measures approximately 1 1/4 by 7/8 inches (32 by 23 mm). Signal connections are made via two 12-pin single-row pin headers, which are labeled "A" to "X" for easy identification. The header pins are spaced one-tenth of an inch apart, with the header rows spaced 0.6 inches apart, allowing compatibility with in-line sockets or direct wiring to a protoboard. Outputs range from one Hertz to one megahertz. The module also provides three buffered outputs at ten megahertz, suitable for driving time base inputs of test equipment. Two buffer gates remain uncommitted, enabling the buffering of any two outputs or the buffering of an external signal (e.g., a lock indicator for an LPRO or FRS output). The divider outputs are driven by microprocessor port pins capable of sourcing or sinking up to 100 milliamperes each. The one Hertz output can directly drive an LED to function as an "active" indicator. These driving capabilities are constrained by the selected input voltage and the current limitations of the regulator, as specified in the Power section. The input signal is applied between the module pins labeled "K" and "L" (ground), as illustrated in the schematic. The conditioning circuit is designed to be compatible with the LPRO-101 specifications, typically accepting an input signal of 0.55 Volts RMS (approximately 1.5 Volts peak to peak). Photo 1 shows the typical input conditioning signals for an LPRO input. It should be noted that the input may not operate reliably for signal inputs below one Volt peak to peak. Inputs as high as 6 Volts peak to peak have been utilized but are not recommended for routine operation. To verify proper operation of the conditioning circuit, an oscilloscope should be used to observe the input signal between ground and pin 1 of the hex inverter. If the input voltage is within the specified range, a 10 MHz square wave can be observed at pins "H", "T", and "V". Buffered versions of the conditioned signal appear at pins "J", "O", and "P" as shown in the schematic. When using the zener diode, the input voltage applied to the module should be a minimum of 15 Volts. For direct operation at lower voltages, such as 5 Volts, the shorting jumper should remain in place (the factory-wired default). To utilize the zener diode, the shorting jumper across the diode on the bottom side of the board should be cut. The addition of the zener diode reduces the regulator input voltage to approximately 15 Volts. It is important to note that operating the module at higher input voltages (e.g., above 10 Volts) may significantly limit divider output currents, as indicated below. Once the appropriate input voltage has been selected, configured, and applied to pin "M", the operation of the regulator can be verified by measuring the voltage between ground and the power pins of the integrated circuits. For example, 3.3 Volts should be observed on pin 14 of the hex inverter and on pin 7 of the microprocessor.

The DECUS divider module is designed to provide reliable signal conditioning and frequency division for rubidium oscillator outputs. Its compact size and versatile pin header configuration facilitate easy integration into various electronic systems. The module's ability to generate multiple marker signals makes it suitable for applications in timekeeping, frequency generation, and synchronization tasks. The three buffered ten megahertz outputs are particularly useful for interfacing with test equipment, ensuring signal integrity and robustness.

The design incorporates a hex inverter to condition the input signal, ensuring that it meets the operational requirements of the associated rubidium oscillator. The specified input voltage range is critical for maintaining optimal performance, and the use of an oscilloscope for verification ensures that users can confirm the module's correct operation before deployment. The flexibility to use a zener diode for higher voltage operation or to maintain functionality at lower voltages enhances the module's adaptability to different applications.

In summary, the DECUS divider module is a sophisticated solution for conditioning and dividing high-frequency signals, providing essential features that cater to both standard and specialized applications. Its design considerations, including current limitations and voltage requirements, are essential for users to understand to ensure reliable and effective operation in their specific use cases.The following describes the design, construction, operation and use of the DECUS divider module. Photo 2 shows a top view of the module and Photo 3 shows the bottom. The primary use of the module is to condition the 10 megahertz (MHz) signal from a rubidium oscillator such as the LPRO-101 or FRS-C units manufactured by EFRATOM Ball, Inc. The DECUS module divides the 10 MHz output from these units to produce marker signals at various frequencies. If you require a multiplied frequency output in addition to the decade divisor, you may be interested in the DECL module. If you have a FE-5680 rubidium reference, you may be interested in the FEBO module. The module`s conditioning circuit and divider chip can also be used for other applications requiring signal conditioning and dividing, but this usage is outside the scope of this document.

The schematic shows the components, circuitry and some operational restrictions for the module. The Parts List provides additional information about the components used to assemble the module. photo 2, the module measures approximately 1 1/4 by 7/8 inches (32 by 23 mm). Signal connections are provided on two 12-pin single row pin headers. The header connections are labeled "A" to "X" for easy reference. Header pins are spaced one tenth of an inch apart and the header rows are spaced 0. 6 inch apart. This allows the module to be used with in-line sockets or wired directly to a protoboard. outputs, ranging from one Hertz to one megahertz. The module also provides three ten megahertz buffered outputs for driving time base inputs of test equipment. Two buffer gates are uncommitted to allow any two of the outputs to be buffered or to allow buffering of an external signal (e.

g. , a lock indicator for an LPRO or FRS output). Divider outputs are driven by microprocessor port pins capable of sourcing or sinking up to 100 milliamperes each. The one Hertz output can directly drive an LED to act as an "active" indicator. These drive capabilities are limited by the choice of input voltage and the current limitations of the regulator, as noted in the Power section.

The input signal is applied between the module pins labeled "K" and "L" (ground), as shown in the schematic. The conditioning circuit is designed to be compatible with the LPRO-101 specifications with a typical input signal of 0.

55 Volts RMS (approximately 1. 5 Volts peak to peak). DECUS Photo 1 shows the typical input conditioning signals for a LPRO input. Note: The input may not operate reliably for signal inputs under one Volt peak to peak. Inputs as high as 6 Volts peak to peak have been used but are not recommended for routine operation. To verify the correct operation of the conditioning circuit, use an oscilloscope to observe the input signal between ground and pin 1 of the hex inverter. If the input voltage is within the range specified above, a 10 MHz square wave can be observed at pins "H", "T" and "V.

" Buffered versions of the conditioned signal appear at pins "J", "O" and "P" as shown in the schematic. schematic ). When using the zener, the input voltage applied to the module should be a minimum of 15 Volts. For direct operation at lower voltages, such as 5 Volts, the shorting jumper should be left in place (the factory-wired default).

To use the zener diode, cut the shorting jumper across the diode on the bottom side of the board. The addition of the zener drops the regulator input voltage to approximately 15 Volts. Note that operating the module at higher input voltages (e. g. , above 10 Volts) may significantly limit divider output currents, as noted below. Once the proper input voltage has been selected, configured and applied to pin "M", the operation of the regulator can be verified by measuring the voltage betweeen ground and the power pins of the ICs. For example, 3. 3 Volts should appear on pin 14 of the hex inverter and on pin 7 of the microprocessor. The measured 🔗 External reference

The DECUS divider module is designed to provide reliable signal conditioning and frequency division for rubidium oscillator outputs. Its compact size and versatile pin header configuration facilitate easy integration into various electronic systems. The module's ability to generate multiple marker signals makes it suitable for applications in timekeeping, frequency generation, and synchronization tasks. The three buffered ten megahertz outputs are particularly useful for interfacing with test equipment, ensuring signal integrity and robustness.

The design incorporates a hex inverter to condition the input signal, ensuring that it meets the operational requirements of the associated rubidium oscillator. The specified input voltage range is critical for maintaining optimal performance, and the use of an oscilloscope for verification ensures that users can confirm the module's correct operation before deployment. The flexibility to use a zener diode for higher voltage operation or to maintain functionality at lower voltages enhances the module's adaptability to different applications.

In summary, the DECUS divider module is a sophisticated solution for conditioning and dividing high-frequency signals, providing essential features that cater to both standard and specialized applications. Its design considerations, including current limitations and voltage requirements, are essential for users to understand to ensure reliable and effective operation in their specific use cases.The following describes the design, construction, operation and use of the DECUS divider module. Photo 2 shows a top view of the module and Photo 3 shows the bottom. The primary use of the module is to condition the 10 megahertz (MHz) signal from a rubidium oscillator such as the LPRO-101 or FRS-C units manufactured by EFRATOM Ball, Inc. The DECUS module divides the 10 MHz output from these units to produce marker signals at various frequencies. If you require a multiplied frequency output in addition to the decade divisor, you may be interested in the DECL module. If you have a FE-5680 rubidium reference, you may be interested in the FEBO module. The module`s conditioning circuit and divider chip can also be used for other applications requiring signal conditioning and dividing, but this usage is outside the scope of this document.

The schematic shows the components, circuitry and some operational restrictions for the module. The Parts List provides additional information about the components used to assemble the module. photo 2, the module measures approximately 1 1/4 by 7/8 inches (32 by 23 mm). Signal connections are provided on two 12-pin single row pin headers. The header connections are labeled "A" to "X" for easy reference. Header pins are spaced one tenth of an inch apart and the header rows are spaced 0. 6 inch apart. This allows the module to be used with in-line sockets or wired directly to a protoboard. outputs, ranging from one Hertz to one megahertz. The module also provides three ten megahertz buffered outputs for driving time base inputs of test equipment. Two buffer gates are uncommitted to allow any two of the outputs to be buffered or to allow buffering of an external signal (e.

g. , a lock indicator for an LPRO or FRS output). Divider outputs are driven by microprocessor port pins capable of sourcing or sinking up to 100 milliamperes each. The one Hertz output can directly drive an LED to act as an "active" indicator. These drive capabilities are limited by the choice of input voltage and the current limitations of the regulator, as noted in the Power section.

The input signal is applied between the module pins labeled "K" and "L" (ground), as shown in the schematic. The conditioning circuit is designed to be compatible with the LPRO-101 specifications with a typical input signal of 0.

55 Volts RMS (approximately 1. 5 Volts peak to peak). DECUS Photo 1 shows the typical input conditioning signals for a LPRO input. Note: The input may not operate reliably for signal inputs under one Volt peak to peak. Inputs as high as 6 Volts peak to peak have been used but are not recommended for routine operation. To verify the correct operation of the conditioning circuit, use an oscilloscope to observe the input signal between ground and pin 1 of the hex inverter. If the input voltage is within the range specified above, a 10 MHz square wave can be observed at pins "H", "T" and "V.

" Buffered versions of the conditioned signal appear at pins "J", "O" and "P" as shown in the schematic. schematic ). When using the zener, the input voltage applied to the module should be a minimum of 15 Volts. For direct operation at lower voltages, such as 5 Volts, the shorting jumper should be left in place (the factory-wired default).

To use the zener diode, cut the shorting jumper across the diode on the bottom side of the board. The addition of the zener drops the regulator input voltage to approximately 15 Volts. Note that operating the module at higher input voltages (e. g. , above 10 Volts) may significantly limit divider output currents, as noted below. Once the proper input voltage has been selected, configured and applied to pin "M", the operation of the regulator can be verified by measuring the voltage betweeen ground and the power pins of the ICs. For example, 3. 3 Volts should appear on pin 14 of the hex inverter and on pin 7 of the microprocessor. The measured 🔗 External reference