fADC Amplifier Circuit Simulations

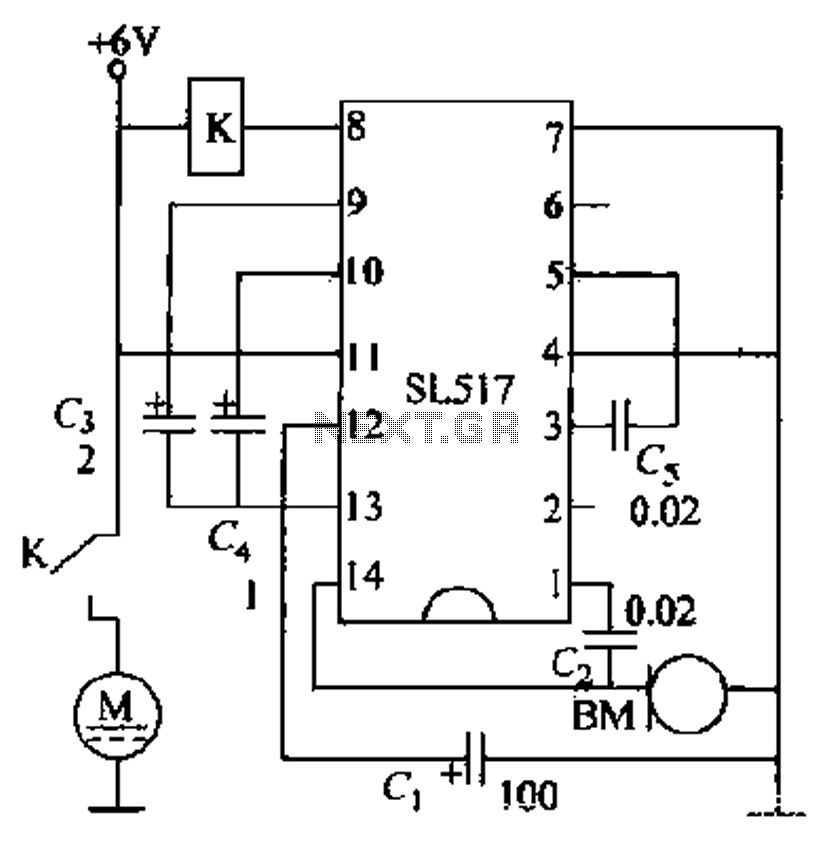

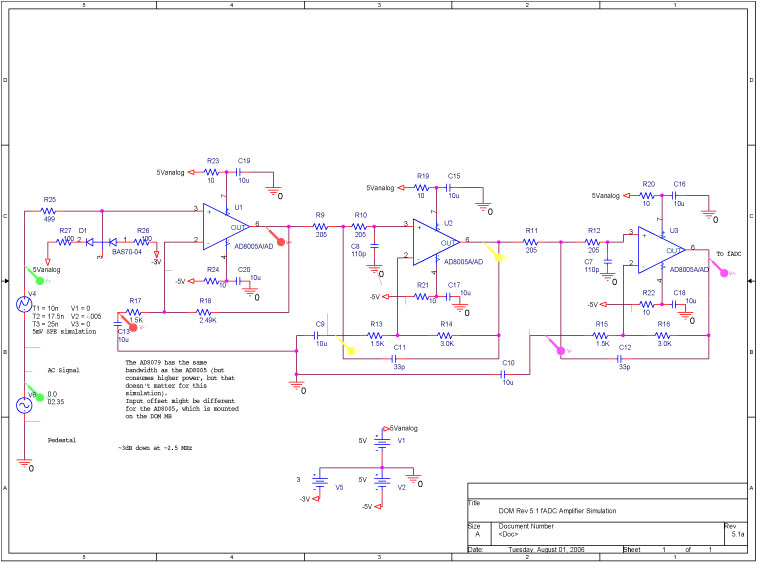

A bandwidth-limited amplifier shapes the waveform sampled by the 40 MHz high-speed pipeline Analog to Digital Converter (fast ADC, or fADC). It is well known that the shaping time is twice the time constant (peaking time) for each pole of the filter network. The time constant is calculated as (205 Ω x 110 pF) = 22.5 ns. The amplifier-filter topology consists of an amplifier preceding two cascaded two-pole active filters. The response of the filter to an impulse (similar to a pulse from a photomultiplier) yields a pulse that can be sampled at least twice on its rising or falling edge by the fADC. This waveform satisfies the Nyquist-Shannon sampling theorem, as there is negligible signal energy at half the sampling frequency. The gain is adjusted so that a 5 mV single photoelectron (SPE) pulse, approximated by a triangular pulse 15 ns wide at its base and 5 mV high, produces a 12 mV (six ADC count) pulse at the input of the fADC.

The described circuit employs a bandwidth-limited amplifier to enhance the signal integrity of a 40 MHz high-speed pipeline Analog to Digital Converter (ADC). The amplifier is crucial for shaping the waveform, ensuring that the signal is adequately processed for accurate digitization. The shaping time, which is critical for determining the response characteristics of the circuit, is derived from the time constant associated with the filter network. Specifically, the time constant, calculated as the product of resistance (205 Ω) and capacitance (110 pF), results in a value of 22.5 ns, which indicates the temporal response of the amplifier-filter arrangement.

The topology of the circuit features an amplifier followed by two cascaded two-pole active filters. This configuration is designed to optimize the frequency response and minimize noise, thereby enhancing the overall performance of the ADC. The filter's impulse response is particularly important; it is engineered to replicate the characteristics of a pulse generated by a photomultiplier tube, which is common in high-speed applications. The ability of the filter to produce a pulse that can be sampled at least twice on both the rising and falling edges is a key factor in ensuring compliance with the Nyquist-Shannon sampling theorem. This theorem asserts that to accurately reconstruct a signal, it must be sampled at a rate greater than twice its highest frequency component, which is achieved in this design.

Moreover, the gain of the amplifier is meticulously adjusted to ensure that a 5 mV single photoelectron (SPE) pulse—characterized as a triangular pulse with a width of 15 ns and a peak amplitude of 5 mV—results in a 12 mV output pulse at the ADC input. This translates to a six-count reading on the ADC, ensuring that the signal is sufficiently amplified for reliable digital representation. Overall, this circuit design exemplifies a well-structured approach to signal processing in high-speed applications, balancing amplification, filtering, and sampling to achieve optimal performance.A band-width limited amplifies shapes the waveform sampled by the 40 MHz high speed, pipeline Analog to Digital Converter (fast ADC, or fADC). It is well known that the shaping time is twice the time constant (peaking time), per pole of the filter network.

The time constant is (205 © x 110pF) = 22. 5ns. The amplifier-filter topology consists of an amplifier preceding two cascaded two-pole active filters. See the lower left corner of the front-end schematic. The response of the filter to an impulse (a pulse substantially like a photomultiplier pulse), yields a pulse that can be sampled at least twice on its rising, or falling edge by the fADC. This waveform easily satisfies the Nyquist Shannon sampling theorem. (Negligeable signal energy at half the sampling frequency) The gain is adjusted so that a 5 mV SPE (approximated by a triangular pulse 15ns wide at its base, 5mV high), produces a 12mV (six ADC count) pulse at the input of the fADC.

🔗 External reference

The described circuit employs a bandwidth-limited amplifier to enhance the signal integrity of a 40 MHz high-speed pipeline Analog to Digital Converter (ADC). The amplifier is crucial for shaping the waveform, ensuring that the signal is adequately processed for accurate digitization. The shaping time, which is critical for determining the response characteristics of the circuit, is derived from the time constant associated with the filter network. Specifically, the time constant, calculated as the product of resistance (205 Ω) and capacitance (110 pF), results in a value of 22.5 ns, which indicates the temporal response of the amplifier-filter arrangement.

The topology of the circuit features an amplifier followed by two cascaded two-pole active filters. This configuration is designed to optimize the frequency response and minimize noise, thereby enhancing the overall performance of the ADC. The filter's impulse response is particularly important; it is engineered to replicate the characteristics of a pulse generated by a photomultiplier tube, which is common in high-speed applications. The ability of the filter to produce a pulse that can be sampled at least twice on both the rising and falling edges is a key factor in ensuring compliance with the Nyquist-Shannon sampling theorem. This theorem asserts that to accurately reconstruct a signal, it must be sampled at a rate greater than twice its highest frequency component, which is achieved in this design.

Moreover, the gain of the amplifier is meticulously adjusted to ensure that a 5 mV single photoelectron (SPE) pulse—characterized as a triangular pulse with a width of 15 ns and a peak amplitude of 5 mV—results in a 12 mV output pulse at the ADC input. This translates to a six-count reading on the ADC, ensuring that the signal is sufficiently amplified for reliable digital representation. Overall, this circuit design exemplifies a well-structured approach to signal processing in high-speed applications, balancing amplification, filtering, and sampling to achieve optimal performance.A band-width limited amplifies shapes the waveform sampled by the 40 MHz high speed, pipeline Analog to Digital Converter (fast ADC, or fADC). It is well known that the shaping time is twice the time constant (peaking time), per pole of the filter network.

The time constant is (205 © x 110pF) = 22. 5ns. The amplifier-filter topology consists of an amplifier preceding two cascaded two-pole active filters. See the lower left corner of the front-end schematic. The response of the filter to an impulse (a pulse substantially like a photomultiplier pulse), yields a pulse that can be sampled at least twice on its rising, or falling edge by the fADC. This waveform easily satisfies the Nyquist Shannon sampling theorem. (Negligeable signal energy at half the sampling frequency) The gain is adjusted so that a 5 mV SPE (approximated by a triangular pulse 15ns wide at its base, 5mV high), produces a 12mV (six ADC count) pulse at the input of the fADC.

🔗 External reference