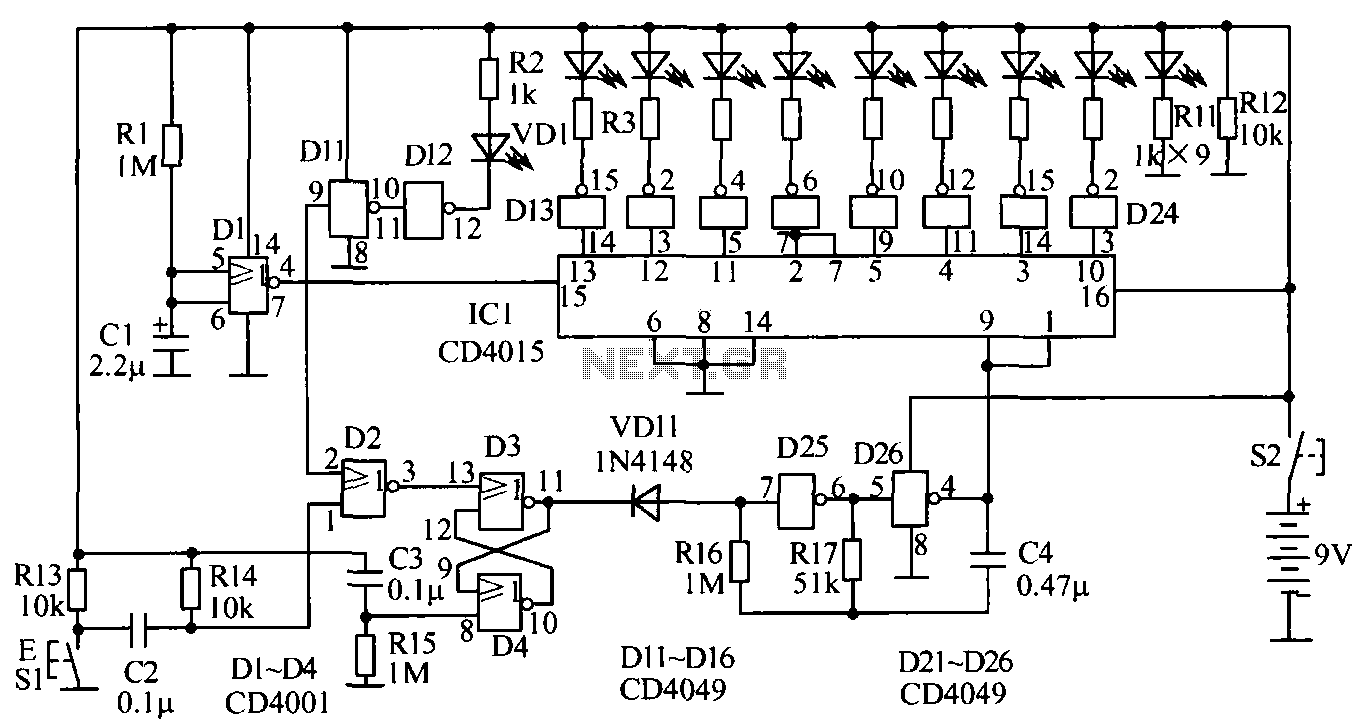

Human reaction speed test circuit

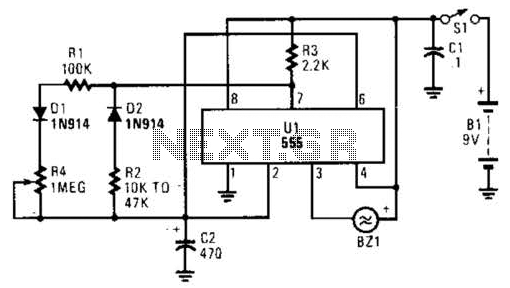

The circuit for testing human reaction speed is illustrated in the figure. It includes NAND gates D25 and D26, along with other components that generate a multivibrator output clock pulse with a period of approximately 50 milliseconds. The circuit is composed of an 8-bit register (IC1) and a boot delay circuit (D1) that produces an output signal for its serial input data. The output of D1 is "1" during the clock pulses, allowing the 8-bit storage unit (IC1) to quickly register all "1" values. After approximately 3 to 4 seconds, the output of D1 changes to "0," activating the test signal VD1. Meanwhile, the 8-bit storage unit, under the influence of clock pulses, resets from left to right to "0" until the participant presses the stop button (S1). The RS flip-flop composed of D3 and D4 outputs "0," which causes NAND gates D25 and D26 to stop vibrating. The IC1 then halts, and the results are displayed through a drive circuit (D13 to D16, D21 to D24) that activates the light-emitting diodes. The role of D2 is to ensure that the stop button (S1) only registers after the VD1 light is illuminated, making any premature press ineffective.

The human reaction speed test circuit is designed to measure the response time of an individual by utilizing a series of digital components that work in conjunction. The core of the circuit is the IC1, an 8-bit register that stores the timing data. The clock pulse, generated by the multivibrator circuit, operates at a frequency that allows for precise timing control, set at approximately 50 milliseconds. This timing is critical for accurately capturing the reaction times of participants.

The boot delay circuit, represented by D1, ensures that the system is initialized correctly before the test begins. When the output of D1 is high ("1"), the IC1 registers a series of high values in rapid succession. This setup remains active for a predetermined duration of 3 to 4 seconds, during which the participant is expected to respond to the test signal indicated by VD1. The transition of D1 to low ("0") signifies the start of the reaction test.

Once the test signal is activated, the 8-bit storage unit begins resetting its values from high ("1") to low ("0") under the clock pulse influence. The participant must then press the stop button (S1) to halt the test. The RS flip-flop, formed by D3 and D4, plays a crucial role in maintaining the state of the circuit, ensuring that the output signal to the NAND gates (D25 and D26) stops the vibration mechanism, thus concluding the timing sequence.

The results of the test are communicated through a series of drive circuits (D13 to D16 and D21 to D24), which control the activation of light-emitting diodes. These LEDs provide a visual representation of the participant's reaction time, making it easy to assess performance. Additionally, the inclusion of D2 serves a protective function, preventing the stop button from being registered until the test signal is fully operational, thereby ensuring the integrity of the test results. Overall, this circuit efficiently combines digital logic components to create an interactive and effective human reaction speed testing device.Human reaction speed test circuit as shown in FIG. NAND gate D25, D26 and other components multivibrator output clock pulse period is about 50ms. IC1 composition 8 right register, D1 composed of boot delay circuit output signal as its serial input data. Just machines, since D1 output is "1" in the clock pulses, IC1 8-bit storage unit quickly all "1"; after 3s ~ 4s, D1 output to "0", the test signal VD1 light, while, IC1 8-bit storage unit under the clock pulses from left to right to "0" until the person being tested press the stop button S1, the D3, RS flip-flop D4 composed of "0" so that D25, D26 stop vibration, IC1 is on hold, the result through the drive circuit D13 ~ D16, D21 ~ D24 drive the light emitting diode display. D2s role is to make the stop button S1 tests only after the bright lights VD1 acts invalid press ahead.

The human reaction speed test circuit is designed to measure the response time of an individual by utilizing a series of digital components that work in conjunction. The core of the circuit is the IC1, an 8-bit register that stores the timing data. The clock pulse, generated by the multivibrator circuit, operates at a frequency that allows for precise timing control, set at approximately 50 milliseconds. This timing is critical for accurately capturing the reaction times of participants.

The boot delay circuit, represented by D1, ensures that the system is initialized correctly before the test begins. When the output of D1 is high ("1"), the IC1 registers a series of high values in rapid succession. This setup remains active for a predetermined duration of 3 to 4 seconds, during which the participant is expected to respond to the test signal indicated by VD1. The transition of D1 to low ("0") signifies the start of the reaction test.

Once the test signal is activated, the 8-bit storage unit begins resetting its values from high ("1") to low ("0") under the clock pulse influence. The participant must then press the stop button (S1) to halt the test. The RS flip-flop, formed by D3 and D4, plays a crucial role in maintaining the state of the circuit, ensuring that the output signal to the NAND gates (D25 and D26) stops the vibration mechanism, thus concluding the timing sequence.

The results of the test are communicated through a series of drive circuits (D13 to D16 and D21 to D24), which control the activation of light-emitting diodes. These LEDs provide a visual representation of the participant's reaction time, making it easy to assess performance. Additionally, the inclusion of D2 serves a protective function, preventing the stop button from being registered until the test signal is fully operational, thereby ensuring the integrity of the test results. Overall, this circuit efficiently combines digital logic components to create an interactive and effective human reaction speed testing device.Human reaction speed test circuit as shown in FIG. NAND gate D25, D26 and other components multivibrator output clock pulse period is about 50ms. IC1 composition 8 right register, D1 composed of boot delay circuit output signal as its serial input data. Just machines, since D1 output is "1" in the clock pulses, IC1 8-bit storage unit quickly all "1"; after 3s ~ 4s, D1 output to "0", the test signal VD1 light, while, IC1 8-bit storage unit under the clock pulses from left to right to "0" until the person being tested press the stop button S1, the D3, RS flip-flop D4 composed of "0" so that D25, D26 stop vibration, IC1 is on hold, the result through the drive circuit D13 ~ D16, D21 ~ D24 drive the light emitting diode display. D2s role is to make the stop button S1 tests only after the bright lights VD1 acts invalid press ahead.