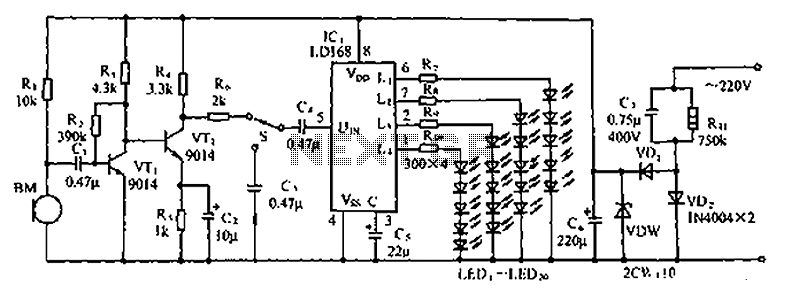

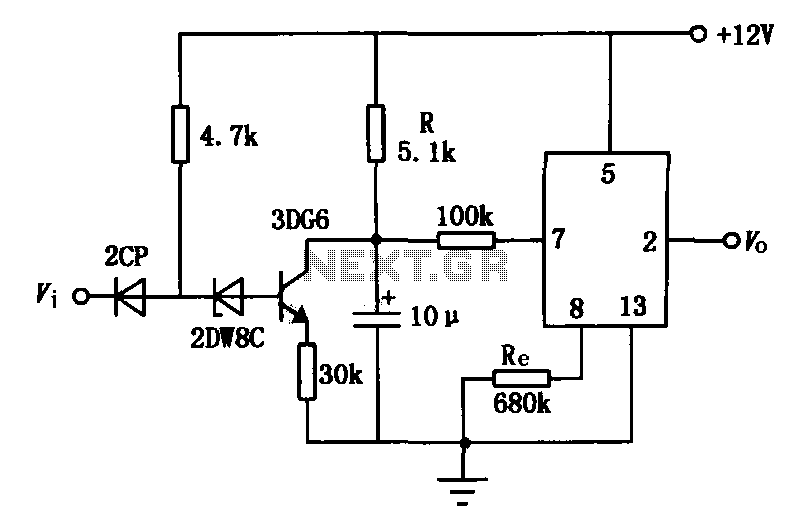

JEC-2 delay circuit diagram consisting of b

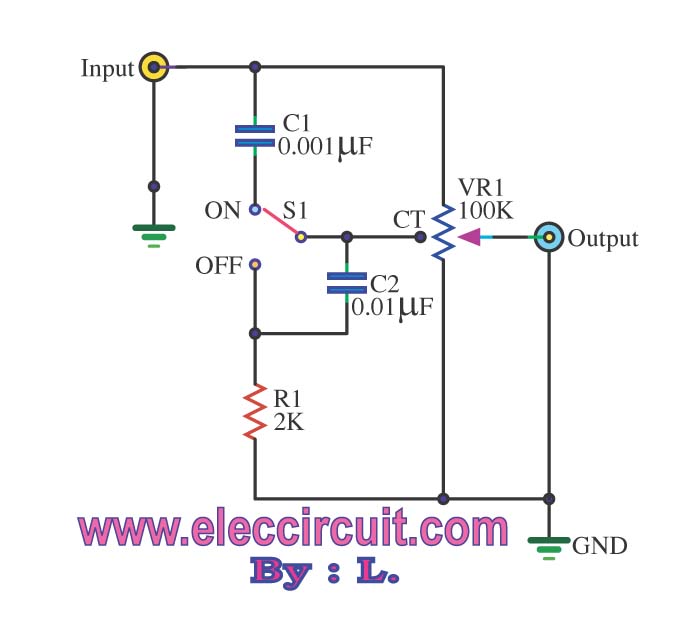

The delay application circuit is depicted in Figure JEC-2, which consists of two components. When the input transitions from logic level 0 to 1, the output also changes to 1 immediately. However, when the input transitions from high level 1 to low level 0, the output changes to 0 after a delay. The delay time is determined by the charging of a capacitor to a specific trigger level. The circuit allows for a delay time ranging from 0.02 to 10 seconds. To achieve a shorter delay time, the resistor (R) and capacitor (C) values can be adjusted, enabling correction of any timing errors.

The delay application circuit described utilizes a simple RC (resistor-capacitor) network to create a time delay in signal processing. In this configuration, the capacitor charges through the resistor when a high logic level is applied at the input. The time constant of the circuit, which dictates the delay, is defined by the product of the resistance (R) and capacitance (C) values (τ = R × C).

When the input signal transitions from a low state (0) to a high state (1), the output reflects this change immediately. Conversely, when the input signal transitions from a high state (1) to a low state (0), the capacitor discharges through the resistor, and the output remains high until the capacitor voltage drops below a certain threshold. This threshold is determined by the specific trigger level set within the circuit, which can be adjusted to fine-tune the response time of the output.

The circuit is designed to accommodate a broad range of delay times, from as short as 0.02 seconds to as long as 10 seconds. By selecting appropriate resistor and capacitor values, the time constant can be modified, allowing for precise control over the delay duration. For applications requiring shorter delays, decreasing the resistance or capacitance will result in a quicker response. Conversely, increasing either component will extend the delay period.

Furthermore, the circuit can be calibrated to correct any discrepancies in timing by adjusting the resistor and capacitor values. This flexibility makes the delay application circuit suitable for various electronic applications where timing control is critical, such as in signal processing, automation systems, and timing circuits.Delay application circuit is shown in Figure purposes JEC-2 consisting of two. When the input end is logic 0 to 1, the output also immediately end 1 ; but when the input end is high level 1 transition to low level 0, the output by the delay after it becomes 0, the delay time from 10 F capacitor charging to the trigger level to ask the decision. This circuit provides the delay time is 0.02 to 10 seconds, for the case where the delay time shorter.

Change R and C, you can change the delay time. Re value adjustment, you can correct errors.

The delay application circuit described utilizes a simple RC (resistor-capacitor) network to create a time delay in signal processing. In this configuration, the capacitor charges through the resistor when a high logic level is applied at the input. The time constant of the circuit, which dictates the delay, is defined by the product of the resistance (R) and capacitance (C) values (τ = R × C).

When the input signal transitions from a low state (0) to a high state (1), the output reflects this change immediately. Conversely, when the input signal transitions from a high state (1) to a low state (0), the capacitor discharges through the resistor, and the output remains high until the capacitor voltage drops below a certain threshold. This threshold is determined by the specific trigger level set within the circuit, which can be adjusted to fine-tune the response time of the output.

The circuit is designed to accommodate a broad range of delay times, from as short as 0.02 seconds to as long as 10 seconds. By selecting appropriate resistor and capacitor values, the time constant can be modified, allowing for precise control over the delay duration. For applications requiring shorter delays, decreasing the resistance or capacitance will result in a quicker response. Conversely, increasing either component will extend the delay period.

Furthermore, the circuit can be calibrated to correct any discrepancies in timing by adjusting the resistor and capacitor values. This flexibility makes the delay application circuit suitable for various electronic applications where timing control is critical, such as in signal processing, automation systems, and timing circuits.Delay application circuit is shown in Figure purposes JEC-2 consisting of two. When the input end is logic 0 to 1, the output also immediately end 1 ; but when the input end is high level 1 transition to low level 0, the output by the delay after it becomes 0, the delay time from 10 F capacitor charging to the trigger level to ask the decision. This circuit provides the delay time is 0.02 to 10 seconds, for the case where the delay time shorter.

Change R and C, you can change the delay time. Re value adjustment, you can correct errors.