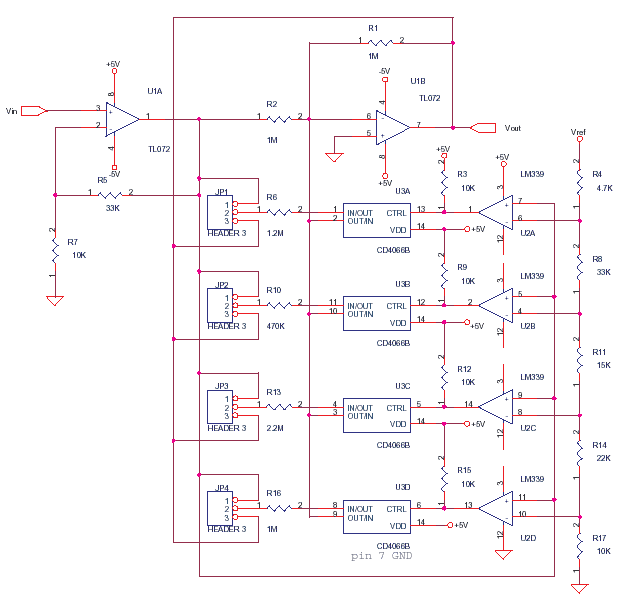

linearizing circuit for thermocouples

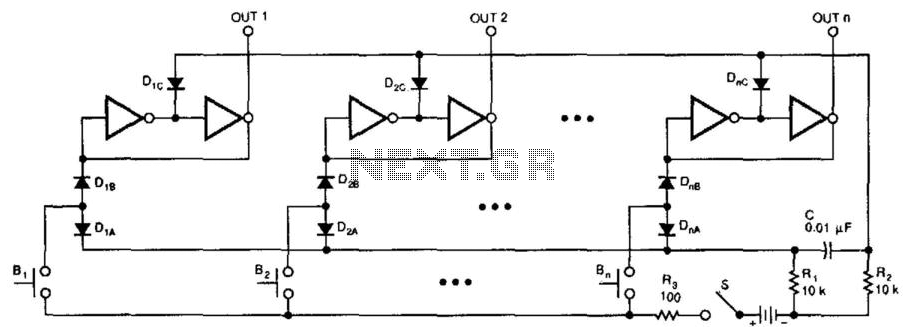

This circuit adjusts the gain of operational amplifier U1B in four distinct steps or segments. It is designed to achieve a linear output from various transducers at levels of 1%. Operational amplifier U1A serves as a buffering amplifier to elevate the signal to the necessary level. The resistor values provided are intended for a hypothetical transducer, and they should be tailored to fit the actual application. The buffered input signal is compared to reference switching points by the LM339 comparator. The LM339 modifies the gain resistors of U1B through the 4066 multiplexer switch. Jumpers JP1 to JP4 allow for the selection of either amplification or attenuation of the signal. The resistors switched by the 4066 can be connected across R1 or R2, depending on the configuration set by JP1 to JP4.

The circuit operates by utilizing two operational amplifiers, U1A and U1B, where U1A functions as a buffer to ensure that the input signal is adequately amplified before it is processed by U1B. The gain of U1B is adjusted through the manipulation of resistors that are switched in and out of the circuit by the 4066 multiplexer. This multiplexer allows for precise control over the gain settings, enabling the circuit to achieve different gain levels as required for various applications.

The LM339 comparator plays a critical role in this circuit by providing reference points for the switching of the gain resistors. It compares the buffered input signal against predetermined reference voltages. Based on this comparison, the LM339 controls the state of the 4066 multiplexer, effectively changing the configuration of the gain resistors connected to U1B. This switching mechanism is essential for achieving the desired amplification or attenuation.

The use of jumpers JP1 to JP4 allows for user-defined selection of gain settings, making the circuit versatile for different transducer types and applications. The configuration of the resistors switched by the 4066 can be adjusted to either amplify the signal through R1 or attenuate it through R2, depending on the specific needs of the application. Overall, this circuit design is suitable for applications requiring precise signal conditioning from transducers, providing flexibility and adaptability in gain settings.This circuit changes the gain of opamp U1B in four steps or segments. It can be used to get a linear output from most transducers to 1% levels. U1A is a amplifying buffer use it to boost the signal to the required level. The resistor values i have put are for an imaginary transducer, you have to design them. The buffered input signal is compared to reference switching points by LM339. LM339 changes the gain resistors of U1B thru the mux switch 4066. JP1 to JP4 can select either amplification or attenuation of signal. The resistor switched by 4066 can be across R1 or R2 based on JP1 to JP4. 🔗 External reference

The circuit operates by utilizing two operational amplifiers, U1A and U1B, where U1A functions as a buffer to ensure that the input signal is adequately amplified before it is processed by U1B. The gain of U1B is adjusted through the manipulation of resistors that are switched in and out of the circuit by the 4066 multiplexer. This multiplexer allows for precise control over the gain settings, enabling the circuit to achieve different gain levels as required for various applications.

The LM339 comparator plays a critical role in this circuit by providing reference points for the switching of the gain resistors. It compares the buffered input signal against predetermined reference voltages. Based on this comparison, the LM339 controls the state of the 4066 multiplexer, effectively changing the configuration of the gain resistors connected to U1B. This switching mechanism is essential for achieving the desired amplification or attenuation.

The use of jumpers JP1 to JP4 allows for user-defined selection of gain settings, making the circuit versatile for different transducer types and applications. The configuration of the resistors switched by the 4066 can be adjusted to either amplify the signal through R1 or attenuate it through R2, depending on the specific needs of the application. Overall, this circuit design is suitable for applications requiring precise signal conditioning from transducers, providing flexibility and adaptability in gain settings.This circuit changes the gain of opamp U1B in four steps or segments. It can be used to get a linear output from most transducers to 1% levels. U1A is a amplifying buffer use it to boost the signal to the required level. The resistor values i have put are for an imaginary transducer, you have to design them. The buffered input signal is compared to reference switching points by LM339. LM339 changes the gain resistors of U1B thru the mux switch 4066. JP1 to JP4 can select either amplification or attenuation of signal. The resistor switched by 4066 can be across R1 or R2 based on JP1 to JP4. 🔗 External reference