Mark 2 Memory circuit

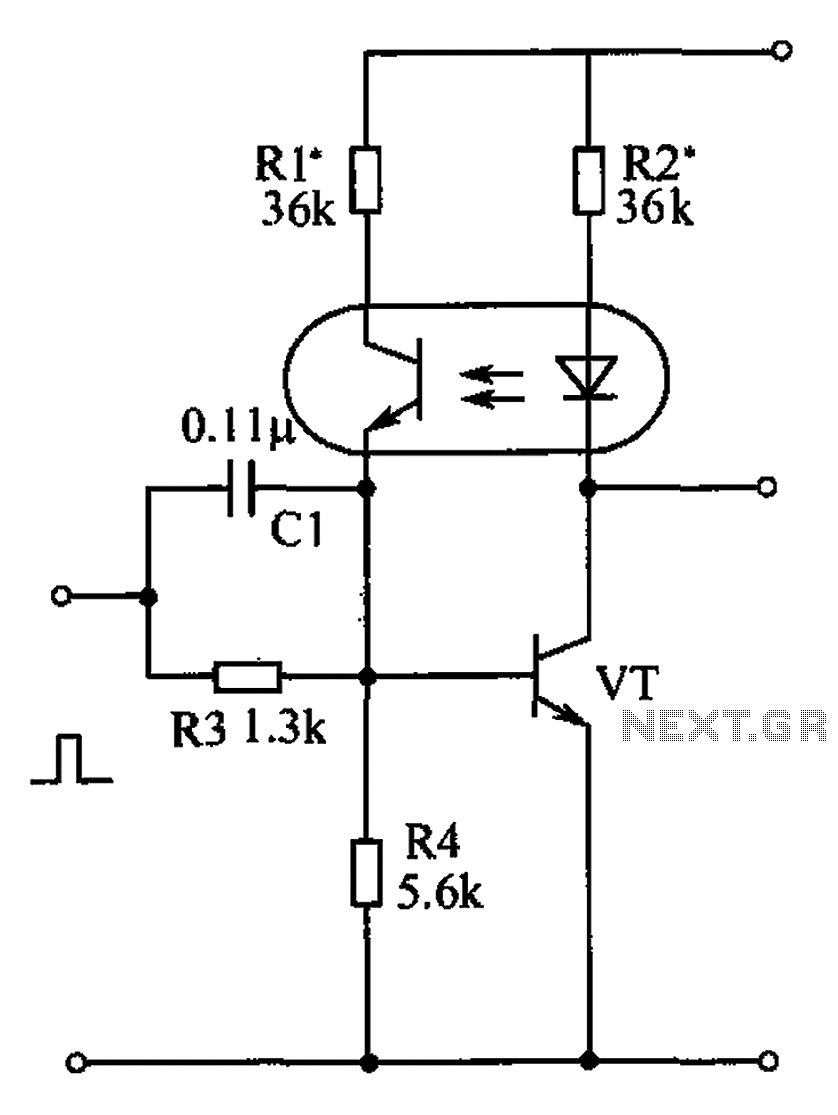

The memory component of the Mark 2 system is quite straightforward. It consists of two 32K SRAM chips, which are actually FRAM due to availability, but this does not impact functionality in this context. The selection of these chips is achieved through the logical OR of the MREQ signal and A15 (or the inverse of A15 for the upper chip). The boot code for the Z80 is stored in the PIC, which controls the entire address bus while keeping the Z80 in a reset state. After power-on, the boot code is written to standard RAM. This setup minimizes the need for complex decoding logic and eliminates the requirement for a ROM chip, allowing the entire memory space to be utilized by any running application without any "unwritable" regions. The logic used to generate the select signals does not involve OR gates, as none were available on the board; instead, NAND and NOT gates were employed, which were surplus from other functions. The conversion is based on De Morgan's Laws, which state that the equivalence of inverted operators can transform an AND gate into an OR gate when both inputs and outputs are inverted. Since a NAND gate's output is already inverted, inverting the inputs will yield a function equivalent to the OR gate truth table. This configuration requires only one additional gate, as A15 must be inverted anyway; the inverted version is used for selecting the other chip, while an extra NOT gate is used on the MREQ signal. Although FRAM chips are in use, they are not intended for data storage due to previous experiences with their reliability in homemade circuits. It is advisable to incorporate a pull-up resistor on the chip select pin to prevent glitches during power-on that could compromise memory data. A 10K or 4.7K resistor has been effective in enhancing resilience, making it a valuable addition even if the system is not expected to operate during transitional power states.

The memory architecture of the Mark 2 system is designed for efficiency and flexibility. The dual 32K FRAM chips enable a compact memory solution while allowing for quick access and manipulation of data. The use of the MREQ signal in conjunction with the A15 address line to select between the two chips optimizes the memory mapping, making it straightforward for the Z80 processor to interact with the memory. The design choice to forgo a ROM chip in favor of utilizing RAM for boot code storage provides a significant advantage in terms of resource utilization. This approach allows for dynamic memory allocation and eliminates the limitations commonly associated with fixed ROM storage.

The logic design implemented to generate the chip select signals exemplifies a practical application of digital logic principles. By using NAND and NOT gates, the circuit achieves the necessary functionality without the need for additional OR gates, thus simplifying the overall design. The implementation of De Morgan's Laws in this context showcases the versatility of digital logic, enabling the designer to adapt available components to meet specific requirements.

The consideration of using pull-up resistors with the FRAM chips highlights the importance of robust circuit design, particularly in ensuring data integrity during power transitions. The recommendation to use a 10K or 4.7K resistor demonstrates a proactive approach to mitigating potential issues that could arise from power fluctuations. This attention to detail can significantly enhance the reliability of the memory system, making it suitable for various applications where data retention during power cycles is critical. Overall, the memory architecture of the Mark 2 system is a well-thought-out design that balances simplicity, functionality, and reliability.The memory part of my Mark 2 system is extremely simple. There are two 32K SRAM chips (actually FRAM because I had them lying around, but there isn`t any significant difference in this application). These are selected with the logical OR of the MREQ signal and A15 (or inverse of A15 for the upper chip).

Because the boot code for the Z80 is held by the PIC and the PIC can control the whole address bus while it holds the Z80 in reset the boot code is written to normal RAM after power-on. This provides the advantage of less decode logic, and no ROM chip, as well as allowing the whole of the memory space to be used by whatever application is running as there are no "unwriteable" regions.

The actual logic I used to generate the select signals is not OR gates, as there were none of these on the board, but NAND and NOT gates as I had spare of these from various other functions. The translation is based on De Morgan`s Laws about equivalence of inverted operators. Basically if I invert both inputs and output of an and gate it becomes an or gate. However since I have a NAND gate the output is already inverted, so inverting the inputs will make the output equivalent to my OR gate truth table.

This actually only requires one extra gate as I would have to invert A15 anyway, the inverted version is just used in the select for the other chip now, and the extra gate is a NOT gate on the MREQ signal. I`ve mentioned here that I`m using FRAM chips. I currently don`t plan to use them for storage of data however, as I have found them somewhat "temperamental" in home made circuits in the past.

If you are interested in storing data in them through power-cycles, it`s worth noting that somewhere in the data sheet it suggests using a pull-up resistor on the chip select pin, this avoids any glitches during power-on that could destroy data in the memory. I`ve used a 10K, or possibly even a 4K7 in the past, and noticed much improved resilience, so even if you don`t think your system should be doing anything while power isn`t fully on or off, it`s worth adding that pull up.

🔗 External reference

The memory architecture of the Mark 2 system is designed for efficiency and flexibility. The dual 32K FRAM chips enable a compact memory solution while allowing for quick access and manipulation of data. The use of the MREQ signal in conjunction with the A15 address line to select between the two chips optimizes the memory mapping, making it straightforward for the Z80 processor to interact with the memory. The design choice to forgo a ROM chip in favor of utilizing RAM for boot code storage provides a significant advantage in terms of resource utilization. This approach allows for dynamic memory allocation and eliminates the limitations commonly associated with fixed ROM storage.

The logic design implemented to generate the chip select signals exemplifies a practical application of digital logic principles. By using NAND and NOT gates, the circuit achieves the necessary functionality without the need for additional OR gates, thus simplifying the overall design. The implementation of De Morgan's Laws in this context showcases the versatility of digital logic, enabling the designer to adapt available components to meet specific requirements.

The consideration of using pull-up resistors with the FRAM chips highlights the importance of robust circuit design, particularly in ensuring data integrity during power transitions. The recommendation to use a 10K or 4.7K resistor demonstrates a proactive approach to mitigating potential issues that could arise from power fluctuations. This attention to detail can significantly enhance the reliability of the memory system, making it suitable for various applications where data retention during power cycles is critical. Overall, the memory architecture of the Mark 2 system is a well-thought-out design that balances simplicity, functionality, and reliability.The memory part of my Mark 2 system is extremely simple. There are two 32K SRAM chips (actually FRAM because I had them lying around, but there isn`t any significant difference in this application). These are selected with the logical OR of the MREQ signal and A15 (or inverse of A15 for the upper chip).

Because the boot code for the Z80 is held by the PIC and the PIC can control the whole address bus while it holds the Z80 in reset the boot code is written to normal RAM after power-on. This provides the advantage of less decode logic, and no ROM chip, as well as allowing the whole of the memory space to be used by whatever application is running as there are no "unwriteable" regions.

The actual logic I used to generate the select signals is not OR gates, as there were none of these on the board, but NAND and NOT gates as I had spare of these from various other functions. The translation is based on De Morgan`s Laws about equivalence of inverted operators. Basically if I invert both inputs and output of an and gate it becomes an or gate. However since I have a NAND gate the output is already inverted, so inverting the inputs will make the output equivalent to my OR gate truth table.

This actually only requires one extra gate as I would have to invert A15 anyway, the inverted version is just used in the select for the other chip now, and the extra gate is a NOT gate on the MREQ signal. I`ve mentioned here that I`m using FRAM chips. I currently don`t plan to use them for storage of data however, as I have found them somewhat "temperamental" in home made circuits in the past.

If you are interested in storing data in them through power-cycles, it`s worth noting that somewhere in the data sheet it suggests using a pull-up resistor on the chip select pin, this avoids any glitches during power-on that could destroy data in the memory. I`ve used a 10K, or possibly even a 4K7 in the past, and noticed much improved resilience, so even if you don`t think your system should be doing anything while power isn`t fully on or off, it`s worth adding that pull up.

🔗 External reference