MkI Video digitiser circuit description

A video digitizer, also known as a frame grabber, captures images from a television set, camera, or video recorder and sends them to a computer for display, storage, or manipulation. This document describes a home-built digitizer that connects to an EPP (or bi-directional) parallel port on IBM PCs. This frame grabber digitizes images at high quality in monochrome (8-bit black & white). Although it is designed for the European 625-line / 50Hz TV standard, it can also work with the American 525-line / 60Hz standard with minimal modification. It should be noted that this design is not intended for capturing movies, as it can only manage a few frames per second. The circuit captures images from a succession of frames, requiring the image to remain relatively still for about half a second. A skilled constructor could opt for a larger and more expensive memory chip to simplify the circuit and overcome this limitation (refer to the Mk. II Video Digitizer). Television equipment utilizes a composite video signal that carries all picture information. Images are transmitted as a continuous sequence of frames, each lasting 1/25 second. Each frame consists of 625 horizontal scan lines, transmitted sequentially from top to bottom. To reduce flicker, each frame is transmitted as two consecutive fields, the first containing odd-numbered lines and the second filling in the even-numbered lines, a technique known as interlacing. This method increases the refresh rate to 50Hz without raising the signal bandwidth. Most video recorders and many televisions feature a composite video output, typically using a BNC or phono socket. The 21-pin SCART socket found on most domestic AV equipment also includes a video-out pin. In the signal, increasing voltage corresponds to increasing brightness. Picture lines are separated by a brief sync pulse, during which the voltage drops below the level of total blackness. The sync level is usually 0V, the black level is 0.3V, and peak white is 1.0V. In the diagram, region A represents the sync, region B represents the back porch (at black level), followed by the picture information and concluding with a brief front porch (also at black level) before the next line sync. Frames are separated by longer sync pulses.

European 625 system:

- Frame rate: 25Hz

- Field rate: 50Hz

- Line rate: 4.7μs

- Back porch: 5.8μs

- Picture data: 52.0μs

- Front porch: 1.5μs

- Total: 64.0μs

US 525 system:

- Frame rate: 30Hz

- Field rate: 60Hz

- Line rate: 4.7μs

- Back porch: 4.7μs

- Picture data: 52.66μs

- Front porch: 1.5μs

- Total: 63.56μs

It is important to note that the "625 lines" indicates that the line period is 1/625 of the frame rate. Due to frame syncs and the allocation of 25 lines at the top of the screen for teletext information, there are typically only 576 lines of visual data. A similar reduction applies to the 525/60 US system. To capture all the information in a picture, the composite video signal must be digitized at a rate of approximately 10 million samples per second. Since a standard parallel port cannot handle data at this rate, a hardware buffer is necessary to accept data at high speed and release it slowly to the computer's port. Modern high-speed First-In First-Out (FIFO) memory devices serve as convenient buffers. The Bt218KP-20 analog-to-digital converter was selected for its high specifications and reasonable price. Although a 256kb "frame buffer" FIFO could have been used to capture an entire frame at once, a 2048-byte FIFO, the Am7203A, was chosen for cost reasons and because of additional experimental ideas that required only a small buffer. As a consequence of using a smaller buffer, one image must be captured in segments.

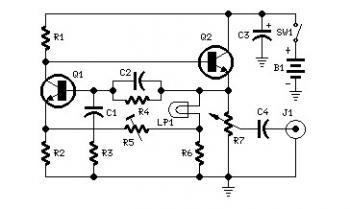

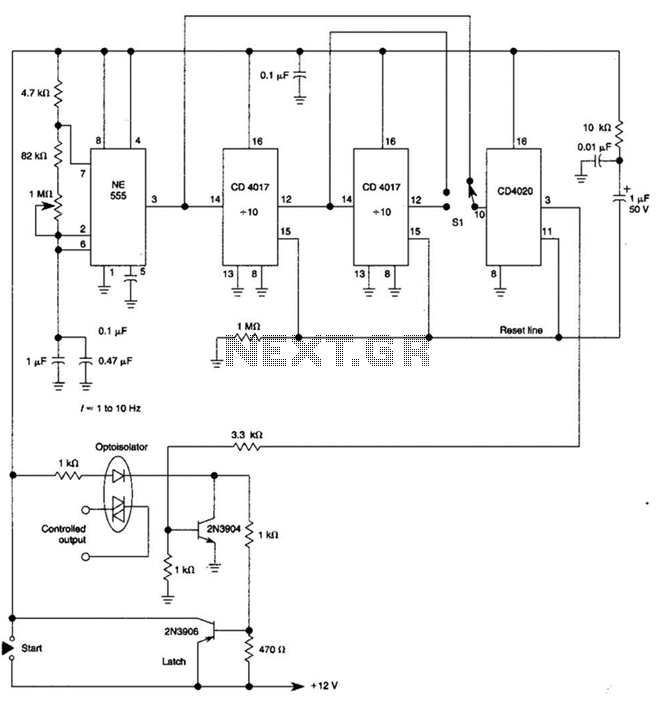

The circuit design includes a composite video input, which connects to the output of the video source. A sync separator circuit extracts the sync pulses from the composite video signal, allowing the digitizer to synchronize with the incoming frames. The analog-to-digital converter samples the analog video signal at the required rate, converting it into a digital format suitable for processing by the computer. The FIFO memory temporarily stores the digitized data, enabling the slower parallel port to retrieve the data without losing frames. The overall design emphasizes simplicity and cost-effectiveness while ensuring adequate performance for monochrome image capture. The circuit's layout should be carefully planned to minimize noise and signal degradation, particularly in the analog sections, to maintain image quality.A "video-digitiser" (also known as a "frame grabber") captures pictures from a TV set, camera, or video recorder, etc. , and forwards them to a computer for display, storage, or general manipulation. This document describes a home-built digitiser which interfaces to an EPP (or bi-directional) parallel port on IBM PCs.

This frame grabber design digitises pictures to very high quality in monochrome (8-bit black & white). Although designed for the European standard 625-line / 50Hz TV system, it should work with the American 525-line / 60Hz standard with minimal modification. Before embarking on the project, please be sure to realise that this design will not capture movies. At best, it can manage a couple of frames per second. Note also that as described, the circuit collects its picture from a succession of frames. Consequently the image must remain fairly still for the half-second or so taken to capture it. A competent constructor could purchase a larger and more expensive memory chip and modify (simplify) the circuit to overcome the latter limitation if desired (see the Mk.

II Video Digitiser ). Television equipment uses a simple composite video signal which carries all the picture information. Pictures are conveyed as a continuous sequence of frames, each taking 1/25 second. Within each frame are 625 horizontal scan lines, transmitted in turn starting at the top. [To reduce flicker, each frame is actually transmitted as two consecutive fields, the first containing odd-numbered lines, and the second filling in the even numbered, a technique known as interlacing. This cunning trick ups the refresh rate to 50Hz, without increasing the signal bandwidth. ] All video recorders and many TV sets will have a composite video output, usually using a BNC or phono socket.

The 21-pin SCART socket found on most domestic AV equipment these days also has a video-out pin. In the signal increasing voltage corresponds to increasing brightness. Picture lines are separated by a brief "sync pulse", during which the voltage goes below that of total blackness. Usually the "sync level" is 0V, black level 0. 3V, and peak white 1. 0V. In the diagram, region a is the sync, b is the "back porch" (at black level). These are followed by the picture information, finishing with a brief "front porch" (also at black level) before the next line sync.

Frames are separated by longer duration sync pulses. frame field line- back picture front line lines rate rate sync porch data porch total European 625 25Hz 50Hz 4. 7us 5. 8us 52. 0us 1. 5us 64. 0us system US system 525 30Hz 60Hz 4. 7us 4. 7us 52. 66us 1. 5us 63. 56us Note that the "625 lines" means that the line period is 1/625 that of the frame rate. Because the equivalent of several lines is spent in frame syncs, and a further 25 lines at the top of the screen are used to carry teletext information, there are only normally 576 lines of visual data.

Some similar decrease will apply to the 525/60 US system. Given the above information, in order to capture all the information in a picture it is clearly necessary to digitise the composite video signal at a rate of around 10 million samples per second. Since your average parallel port cannot possibly take data at that rate, some kind of hardware buffer is required - taking data on board at high speed, and releasing it slowly to the computer`s port.

Modern high-speed First-In First Out (FIFO) memory devices make incredibly simple and convenient buffers. I chose the Bt218KP-20 analog to digital converter because of its high specification and very reasonable price.

I could have chosen a 256kb "frame buffer" FIFO, which would permit capture of a whole frame in one go, but for reasons of cost (and because I had other ideas I wanted to experiment with which required only a small buffer), I have used only a 2048byte FIFO, the Am7203A. A natural consequence of using a small buffer is that one picture h 🔗 External reference

European 625 system:

- Frame rate: 25Hz

- Field rate: 50Hz

- Line rate: 4.7μs

- Back porch: 5.8μs

- Picture data: 52.0μs

- Front porch: 1.5μs

- Total: 64.0μs

US 525 system:

- Frame rate: 30Hz

- Field rate: 60Hz

- Line rate: 4.7μs

- Back porch: 4.7μs

- Picture data: 52.66μs

- Front porch: 1.5μs

- Total: 63.56μs

It is important to note that the "625 lines" indicates that the line period is 1/625 of the frame rate. Due to frame syncs and the allocation of 25 lines at the top of the screen for teletext information, there are typically only 576 lines of visual data. A similar reduction applies to the 525/60 US system. To capture all the information in a picture, the composite video signal must be digitized at a rate of approximately 10 million samples per second. Since a standard parallel port cannot handle data at this rate, a hardware buffer is necessary to accept data at high speed and release it slowly to the computer's port. Modern high-speed First-In First-Out (FIFO) memory devices serve as convenient buffers. The Bt218KP-20 analog-to-digital converter was selected for its high specifications and reasonable price. Although a 256kb "frame buffer" FIFO could have been used to capture an entire frame at once, a 2048-byte FIFO, the Am7203A, was chosen for cost reasons and because of additional experimental ideas that required only a small buffer. As a consequence of using a smaller buffer, one image must be captured in segments.

The circuit design includes a composite video input, which connects to the output of the video source. A sync separator circuit extracts the sync pulses from the composite video signal, allowing the digitizer to synchronize with the incoming frames. The analog-to-digital converter samples the analog video signal at the required rate, converting it into a digital format suitable for processing by the computer. The FIFO memory temporarily stores the digitized data, enabling the slower parallel port to retrieve the data without losing frames. The overall design emphasizes simplicity and cost-effectiveness while ensuring adequate performance for monochrome image capture. The circuit's layout should be carefully planned to minimize noise and signal degradation, particularly in the analog sections, to maintain image quality.A "video-digitiser" (also known as a "frame grabber") captures pictures from a TV set, camera, or video recorder, etc. , and forwards them to a computer for display, storage, or general manipulation. This document describes a home-built digitiser which interfaces to an EPP (or bi-directional) parallel port on IBM PCs.

This frame grabber design digitises pictures to very high quality in monochrome (8-bit black & white). Although designed for the European standard 625-line / 50Hz TV system, it should work with the American 525-line / 60Hz standard with minimal modification. Before embarking on the project, please be sure to realise that this design will not capture movies. At best, it can manage a couple of frames per second. Note also that as described, the circuit collects its picture from a succession of frames. Consequently the image must remain fairly still for the half-second or so taken to capture it. A competent constructor could purchase a larger and more expensive memory chip and modify (simplify) the circuit to overcome the latter limitation if desired (see the Mk.

II Video Digitiser ). Television equipment uses a simple composite video signal which carries all the picture information. Pictures are conveyed as a continuous sequence of frames, each taking 1/25 second. Within each frame are 625 horizontal scan lines, transmitted in turn starting at the top. [To reduce flicker, each frame is actually transmitted as two consecutive fields, the first containing odd-numbered lines, and the second filling in the even numbered, a technique known as interlacing. This cunning trick ups the refresh rate to 50Hz, without increasing the signal bandwidth. ] All video recorders and many TV sets will have a composite video output, usually using a BNC or phono socket.

The 21-pin SCART socket found on most domestic AV equipment these days also has a video-out pin. In the signal increasing voltage corresponds to increasing brightness. Picture lines are separated by a brief "sync pulse", during which the voltage goes below that of total blackness. Usually the "sync level" is 0V, black level 0. 3V, and peak white 1. 0V. In the diagram, region a is the sync, b is the "back porch" (at black level). These are followed by the picture information, finishing with a brief "front porch" (also at black level) before the next line sync.

Frames are separated by longer duration sync pulses. frame field line- back picture front line lines rate rate sync porch data porch total European 625 25Hz 50Hz 4. 7us 5. 8us 52. 0us 1. 5us 64. 0us system US system 525 30Hz 60Hz 4. 7us 4. 7us 52. 66us 1. 5us 63. 56us Note that the "625 lines" means that the line period is 1/625 that of the frame rate. Because the equivalent of several lines is spent in frame syncs, and a further 25 lines at the top of the screen are used to carry teletext information, there are only normally 576 lines of visual data.

Some similar decrease will apply to the 525/60 US system. Given the above information, in order to capture all the information in a picture it is clearly necessary to digitise the composite video signal at a rate of around 10 million samples per second. Since your average parallel port cannot possibly take data at that rate, some kind of hardware buffer is required - taking data on board at high speed, and releasing it slowly to the computer`s port.

Modern high-speed First-In First Out (FIFO) memory devices make incredibly simple and convenient buffers. I chose the Bt218KP-20 analog to digital converter because of its high specification and very reasonable price.

I could have chosen a 256kb "frame buffer" FIFO, which would permit capture of a whole frame in one go, but for reasons of cost (and because I had other ideas I wanted to experiment with which required only a small buffer), I have used only a 2048byte FIFO, the Am7203A. A natural consequence of using a small buffer is that one picture h 🔗 External reference