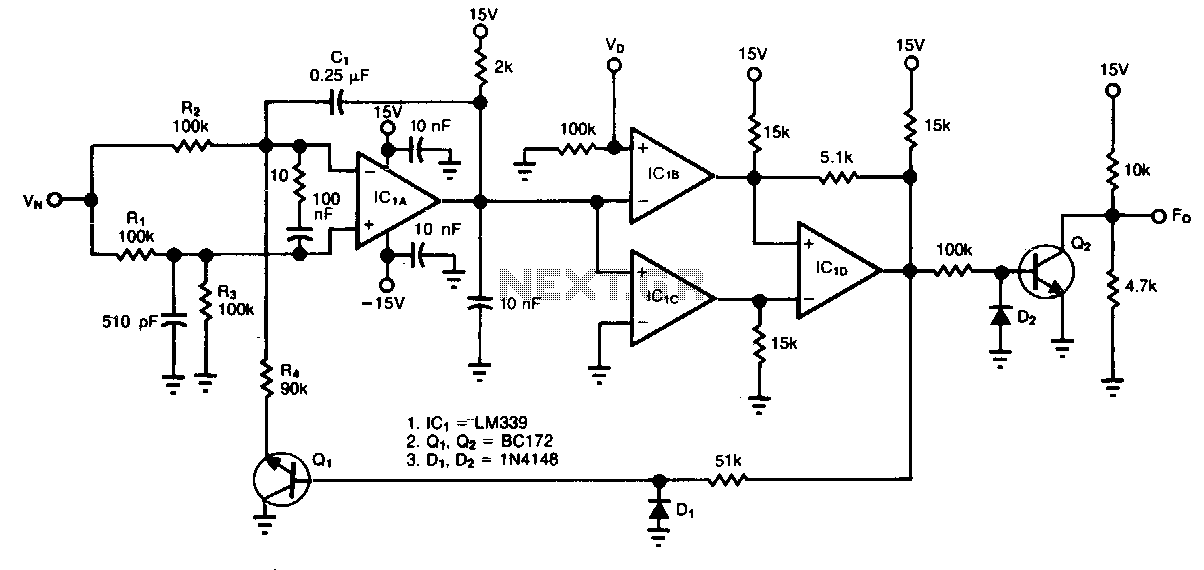

Period-To-Voltage Converter

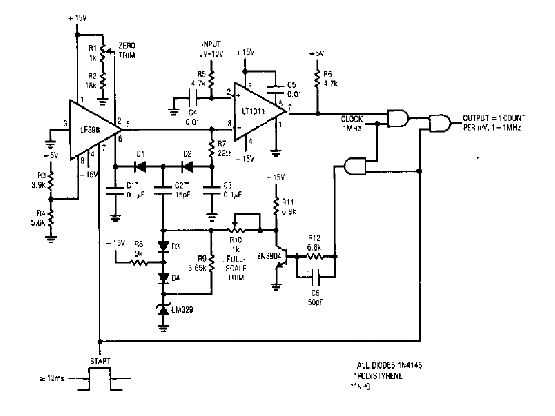

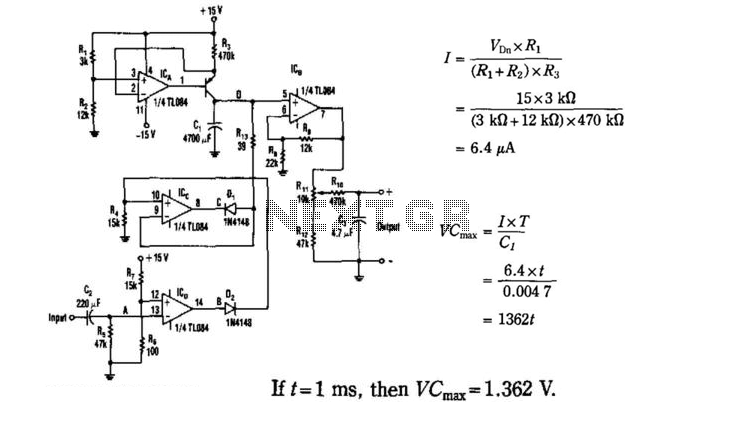

The input signal drives the ICD. Because the positive input (V+) of the ICD is slightly offset to +0.1 V, its steady-state output will be around +13 V. This voltage is sent to the ICC through D2, which sets the output of the ICC to +13 V. Therefore, point D is cut off by D1, and C1 is charged by the current source. Assuming the initial voltage on C1 is zero, the maximum voltage (Vmax) is given by: When the input transitions from low to high, a narrow positive pulse is generated at point A. This pulse becomes -13 V at point B, which cuts off D2. The V+ voltage of the ICC becomes zero. The charge on C1 will be absorbed by ICC in a short time. The time constant of C2 and R5 determines the discharge period, which is approximately 10 µs. ICB is a buffer whose gain is equal to (R8 + R9) / Rg = 1.5. The average voltage of the ICD will be (1362 ± 1.545) + 2 = 1052. R10 and C3 smooth the sawtooth waveform to a DC output.

The circuit described involves multiple components working in conjunction to process an input signal effectively. The input signal is applied to the ICD, which has a positive input offset of +0.1 V, resulting in a steady-state output voltage of approximately +13 V. This output is critical as it is fed into the ICC through diode D2, ensuring that the ICC's output mirrors the ICD's output voltage.

Diode D1 plays a crucial role by cutting off point D, which prevents any feedback that could destabilize the circuit. The capacitor C1 is charged by a current source, starting from an initial voltage of zero. The maximum voltage across C1, denoted as Vmax, indicates the peak charge the capacitor can hold, which is vital for the timing and operation of the circuit.

When the input signal transitions from a low to a high state, a narrow positive pulse is generated at point A. This pulse subsequently translates into a -13 V signal at point B, effectively cutting off diode D2 and causing the V+ of the ICC to drop to zero. This change allows the charge stored in C1 to be quickly absorbed by the ICC, ensuring rapid signal processing.

The discharge period of capacitor C2, in conjunction with resistor R5, is determined by their time constant, which is approximately 10 microseconds. This timing is essential for the circuit's response to input changes, allowing for a swift discharge and maintaining the integrity of the output signal.

The buffer ICB, designed to provide amplification, has a gain defined by the equation (R8 + R9) / Rg, yielding a gain of 1.5. This amplification is crucial for ensuring that the average voltage of the ICD remains stable, calculated to be approximately 1052 V when factoring in the variations and smoothing provided by resistors R10 and capacitor C3.

The combination of R10 and C3 serves to smooth out any sawtooth waveform generated within the circuit, converting it to a stable DC output. This smoothing is essential for applications requiring a consistent voltage level, free from fluctuations that could affect downstream components or systems. Overall, the circuit exemplifies a well-coordinated interaction between various components to achieve effective signal processing and output stabilization. The input signal drives ICD. Because ICD"s positive input (V+) is slightly offset to + 0.1 V, its steady state output will be around +13 V. This voltage is sent to ICC through D2, setting ICC"s output to +13 V. Therefore, point D is cut off by Dl, and CI is charged by the current source. Assuming the initial voltage on CI is zero, the maximum voltage (^Cinax) is given by: When the input goes from low to high, a narrow positive pulse is generated at point A. This pulse becomes -13 V at point B, which cuts off D2. ICC"s V+ voltage becomes zero. The charge on CI will be absorbed by ICC on in a short time. The time constant of C2 and R5 determines the discharge period— about 10 /is. ICB is a buffer whose gain is equal to (R& + R9)~Rg = lM5. ICD"s average voltage will be (1362f 1.545) + 2 = 1052/. RIO and C3 smooth the sawtooth waveform to a dc output.

The circuit described involves multiple components working in conjunction to process an input signal effectively. The input signal is applied to the ICD, which has a positive input offset of +0.1 V, resulting in a steady-state output voltage of approximately +13 V. This output is critical as it is fed into the ICC through diode D2, ensuring that the ICC's output mirrors the ICD's output voltage.

Diode D1 plays a crucial role by cutting off point D, which prevents any feedback that could destabilize the circuit. The capacitor C1 is charged by a current source, starting from an initial voltage of zero. The maximum voltage across C1, denoted as Vmax, indicates the peak charge the capacitor can hold, which is vital for the timing and operation of the circuit.

When the input signal transitions from a low to a high state, a narrow positive pulse is generated at point A. This pulse subsequently translates into a -13 V signal at point B, effectively cutting off diode D2 and causing the V+ of the ICC to drop to zero. This change allows the charge stored in C1 to be quickly absorbed by the ICC, ensuring rapid signal processing.

The discharge period of capacitor C2, in conjunction with resistor R5, is determined by their time constant, which is approximately 10 microseconds. This timing is essential for the circuit's response to input changes, allowing for a swift discharge and maintaining the integrity of the output signal.

The buffer ICB, designed to provide amplification, has a gain defined by the equation (R8 + R9) / Rg, yielding a gain of 1.5. This amplification is crucial for ensuring that the average voltage of the ICD remains stable, calculated to be approximately 1052 V when factoring in the variations and smoothing provided by resistors R10 and capacitor C3.

The combination of R10 and C3 serves to smooth out any sawtooth waveform generated within the circuit, converting it to a stable DC output. This smoothing is essential for applications requiring a consistent voltage level, free from fluctuations that could affect downstream components or systems. Overall, the circuit exemplifies a well-coordinated interaction between various components to achieve effective signal processing and output stabilization. The input signal drives ICD. Because ICD"s positive input (V+) is slightly offset to + 0.1 V, its steady state output will be around +13 V. This voltage is sent to ICC through D2, setting ICC"s output to +13 V. Therefore, point D is cut off by Dl, and CI is charged by the current source. Assuming the initial voltage on CI is zero, the maximum voltage (^Cinax) is given by: When the input goes from low to high, a narrow positive pulse is generated at point A. This pulse becomes -13 V at point B, which cuts off D2. ICC"s V+ voltage becomes zero. The charge on CI will be absorbed by ICC on in a short time. The time constant of C2 and R5 determines the discharge period— about 10 /is. ICB is a buffer whose gain is equal to (R& + R9)~Rg = lM5. ICD"s average voltage will be (1362f 1.545) + 2 = 1052/. RIO and C3 smooth the sawtooth waveform to a dc output.