precision phase locked loop circuit

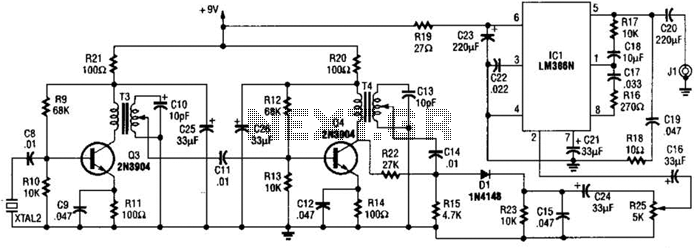

The precision Phase Locked Loop (PLL) in this circuit operates similarly to a basic PLL, but with several enhancements. The flip-flops in the detector are equipped with a gate G1 to clear them, allowing for a faster response. The currents that A1 integrates are directed through transistors Q1, Q2, Q3, and Q4, as transistors provide a quicker response time.

The precision Phase Locked Loop (PLL) circuit is designed to maintain a stable output frequency that is synchronized with a reference input frequency. This circuit utilizes a phase detector, a low-pass filter, and a voltage-controlled oscillator (VCO) to achieve its functionality. The enhancements implemented in this PLL include the incorporation of flip-flops with a clearing mechanism, which significantly improves the response time of the phase detector.

In this configuration, the phase detector compares the phase of the input signal with the output signal from the VCO. The output of the phase detector is a pulse-width modulated signal that represents the phase difference between the two signals. The presence of gate G1 allows for the immediate clearing of the flip-flops, ensuring that the phase detection process can quickly adapt to changes in the input signal.

The integration of currents by operational amplifier A1 is crucial for the PLL's performance. The steering of these currents through transistors Q1, Q2, Q3, and Q4 is strategically implemented to enhance the speed of the circuit. Transistors are selected for this purpose due to their rapid switching capabilities, which help in reducing latency in the phase comparison process.

The output from the low-pass filter, which processes the pulse-width modulation signal, is fed into the VCO. The VCO generates a frequency that is adjusted based on the filtered output, effectively locking onto the reference frequency. This feedback loop continues to operate, maintaining synchronization between the output frequency and the reference input frequency, even in the presence of varying load conditions or input signal variations.

In summary, the precision PLL circuit described is an advanced implementation that leverages the speed of transistors and the efficiency of flip-flops to achieve a highly responsive and stable frequency synchronization system. The design elements, such as the clearing gate and current steering through transistors, contribute to the overall performance and reliability of the PLL in various applications.The precision Phase Locked Loop PLL in this circuit acts very much the same as the basic PLL, with refinements in various places. The flip-flops in the detector have a gate G1 to CLEAR them, for quicker response. The currents which A1 integrates are steered through Q1, Q2 and Q3, Q4 because transistors are quicker..

🔗 External reference

The precision Phase Locked Loop (PLL) circuit is designed to maintain a stable output frequency that is synchronized with a reference input frequency. This circuit utilizes a phase detector, a low-pass filter, and a voltage-controlled oscillator (VCO) to achieve its functionality. The enhancements implemented in this PLL include the incorporation of flip-flops with a clearing mechanism, which significantly improves the response time of the phase detector.

In this configuration, the phase detector compares the phase of the input signal with the output signal from the VCO. The output of the phase detector is a pulse-width modulated signal that represents the phase difference between the two signals. The presence of gate G1 allows for the immediate clearing of the flip-flops, ensuring that the phase detection process can quickly adapt to changes in the input signal.

The integration of currents by operational amplifier A1 is crucial for the PLL's performance. The steering of these currents through transistors Q1, Q2, Q3, and Q4 is strategically implemented to enhance the speed of the circuit. Transistors are selected for this purpose due to their rapid switching capabilities, which help in reducing latency in the phase comparison process.

The output from the low-pass filter, which processes the pulse-width modulation signal, is fed into the VCO. The VCO generates a frequency that is adjusted based on the filtered output, effectively locking onto the reference frequency. This feedback loop continues to operate, maintaining synchronization between the output frequency and the reference input frequency, even in the presence of varying load conditions or input signal variations.

In summary, the precision PLL circuit described is an advanced implementation that leverages the speed of transistors and the efficiency of flip-flops to achieve a highly responsive and stable frequency synchronization system. The design elements, such as the clearing gate and current steering through transistors, contribute to the overall performance and reliability of the PLL in various applications.The precision Phase Locked Loop PLL in this circuit acts very much the same as the basic PLL, with refinements in various places. The flip-flops in the detector have a gate G1 to CLEAR them, for quicker response. The currents which A1 integrates are steered through Q1, Q2 and Q3, Q4 because transistors are quicker..

🔗 External reference