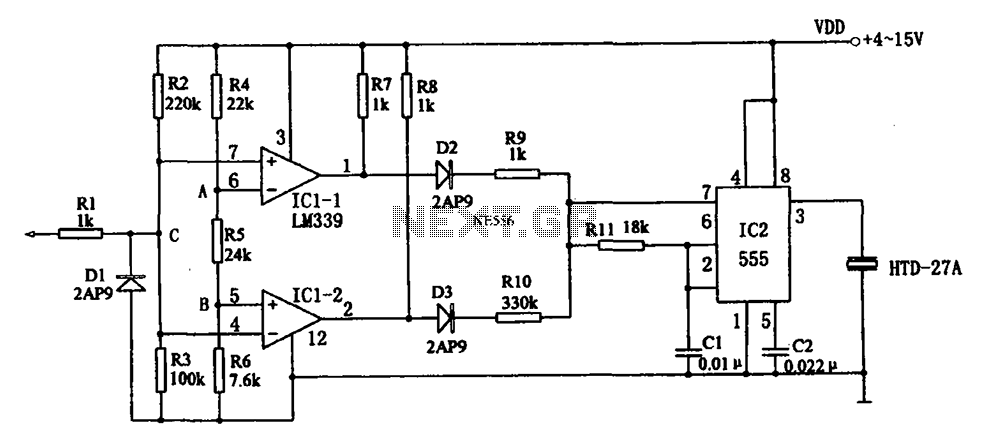

555 sound logic level probe

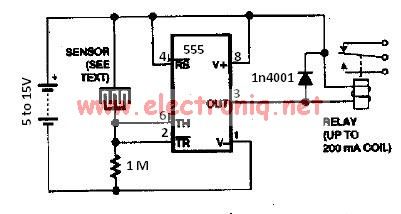

The acoustic logic level probe circuit consists of a voltage comparator, multivibrator, piezoelectric ceramics (HTD), and other components. The configuration of the audio circuit determines the frequency of the sound level to assess the logic levels of TTL or CMOS devices. The voltage comparator LM339 (IC1) utilizes two sections of the LM339, specifically IC1-1 and IC1-2. A voltage divider network formed by resistors R2 and R3 sets the voltage at point C to Vc at 1.9V when VDD is 6V. This voltage is lower than the reference voltage of IC1-1, while remaining higher than the reference voltage of IC1-2, causing diodes D2 and D3 to remain off, preventing the oscillator IC2 from activating. When the probe interacts with high, low, or pulse signals, IC1 detects the high level, while IC2 detects the low-level output signal, which drives D2 and D3 into conduction. This action allows capacitor C1 to charge through resistors R9, R10, and R11, initiating the startup of IC2 and generating sound from the HTD element. When the probe detects a high level, the output signal from IC1-1 turns on D2, charging C1 through R9 and R11. The startup of the oscillator leads to an oscillation frequency of fH = 1.44 / (R10 + 2R11) * C1, corresponding to approximately 4 kHz. Conversely, when a low level is detected, D3 conducts, and C1 charges through R10 and R11, resulting in a lower oscillation frequency fL = 1.44 / (R10 + 2R11) * C1, which is around 700 Hz. When bursts are detected, the HTD emits sound, creating a mix of tones or tremolo effects. The high-frequency sound indicates a high logic level, while low-frequency sound signifies a low logic level, thus enabling the probe to effectively detect logic levels through a series of pulse signals.

The acoustic logic level probe circuit is designed to provide an efficient means of assessing digital logic levels in TTL and CMOS devices through auditory feedback. The integration of a voltage comparator (LM339) allows for precise voltage level detection, while the multivibrator configuration facilitates the generation of distinct frequencies corresponding to the logic levels. The use of piezoelectric ceramics (HTD) as the sound-emitting element enhances the circuit's ability to provide audible indications of detected levels.

The voltage divider network composed of resistors R2 and R3 is crucial for establishing reference voltages necessary for the comparator's operation. By setting the voltage at point C to 1.9V, the circuit can differentiate between high and low logic levels effectively. The operation of diodes D2 and D3 plays a significant role in controlling the activation of the oscillator IC2, ensuring that sound generation occurs only when appropriate logic levels are detected.

The charging and discharging of capacitor C1 through resistors R9, R10, and R11 is fundamental in determining the oscillation frequencies. The calculated frequencies (approximately 4 kHz for high levels and 700 Hz for low levels) provide a clear auditory distinction between the logic states, allowing for immediate identification of the signal type. The ability to mix tones or produce tremolo effects when bursts are detected enhances the user experience, making the probe not only functional but also engaging.

Overall, this circuit exemplifies an innovative approach to logic level detection, utilizing auditory signals to convey information about digital states, making it a valuable tool for electronics engineers and technicians working with digital circuits. As shown for the acoustic logic level probe circuit. The probe consists of a voltage comparator, multivibrator, piezoelectric ceramics HTD and other components. Wherein the com position of the latter two audio circuit to the frequency of the sound level to determine the level of TTL or CMOS device level. Voltage comparator LM339 (IC1) in IC1-1, IC1-2 each 1/4 LM339. Divider network R2, R3 so that when VDD 6V voltage dividing point C is Vc F1.9V, which is lower than the reference voltage IC1-1, but higher than the reference voltage IC1-1, it usually diode D2, D3 are closing, oscillator IC2 does not work.

When the probe contacts the high, low, or pulse, is used to detect high IC1, IC2 for detecting low-level output signal corresponding driven D2, D3 conduction, and through R9, R10, R11 C1 to be charging the IC2 start-up, promote HTD sound. When the probe contacts the high level, IC1-1 output signal so that D2 is turned on, and through R9, R11 on the C1 is charged.

Oscillator start-up, the corresponding oscillation frequency fH 1.44/(R10 + 2R11) C1, the icon parameter corresponding frequency of approximately 4kHz. When the probe contacts the low level, the corresponding D3 conduction, C1 through R10, R11 for charging the corresponding oscillation frequency of the oscillation circuit after start-up is fL 1.44/(R10 + 2R11) C1, the frequency corresponding to the icon parameter is about to 700Hz.

When a burst is detected, the corresponding HTD emit sound mixing two or given tremolo sound. The high-frequency sound judgment circuit is high; low frequency sound judgment low; fat vibrato said probe is a series of pulses, thus realizing the logic level detection.

The acoustic logic level probe circuit is designed to provide an efficient means of assessing digital logic levels in TTL and CMOS devices through auditory feedback. The integration of a voltage comparator (LM339) allows for precise voltage level detection, while the multivibrator configuration facilitates the generation of distinct frequencies corresponding to the logic levels. The use of piezoelectric ceramics (HTD) as the sound-emitting element enhances the circuit's ability to provide audible indications of detected levels.

The voltage divider network composed of resistors R2 and R3 is crucial for establishing reference voltages necessary for the comparator's operation. By setting the voltage at point C to 1.9V, the circuit can differentiate between high and low logic levels effectively. The operation of diodes D2 and D3 plays a significant role in controlling the activation of the oscillator IC2, ensuring that sound generation occurs only when appropriate logic levels are detected.

The charging and discharging of capacitor C1 through resistors R9, R10, and R11 is fundamental in determining the oscillation frequencies. The calculated frequencies (approximately 4 kHz for high levels and 700 Hz for low levels) provide a clear auditory distinction between the logic states, allowing for immediate identification of the signal type. The ability to mix tones or produce tremolo effects when bursts are detected enhances the user experience, making the probe not only functional but also engaging.

Overall, this circuit exemplifies an innovative approach to logic level detection, utilizing auditory signals to convey information about digital states, making it a valuable tool for electronics engineers and technicians working with digital circuits. As shown for the acoustic logic level probe circuit. The probe consists of a voltage comparator, multivibrator, piezoelectric ceramics HTD and other components. Wherein the com position of the latter two audio circuit to the frequency of the sound level to determine the level of TTL or CMOS device level. Voltage comparator LM339 (IC1) in IC1-1, IC1-2 each 1/4 LM339. Divider network R2, R3 so that when VDD 6V voltage dividing point C is Vc F1.9V, which is lower than the reference voltage IC1-1, but higher than the reference voltage IC1-1, it usually diode D2, D3 are closing, oscillator IC2 does not work.

When the probe contacts the high, low, or pulse, is used to detect high IC1, IC2 for detecting low-level output signal corresponding driven D2, D3 conduction, and through R9, R10, R11 C1 to be charging the IC2 start-up, promote HTD sound. When the probe contacts the high level, IC1-1 output signal so that D2 is turned on, and through R9, R11 on the C1 is charged.

Oscillator start-up, the corresponding oscillation frequency fH 1.44/(R10 + 2R11) C1, the icon parameter corresponding frequency of approximately 4kHz. When the probe contacts the low level, the corresponding D3 conduction, C1 through R10, R11 for charging the corresponding oscillation frequency of the oscillation circuit after start-up is fL 1.44/(R10 + 2R11) C1, the frequency corresponding to the icon parameter is about to 700Hz.

When a burst is detected, the corresponding HTD emit sound mixing two or given tremolo sound. The high-frequency sound judgment circuit is high; low frequency sound judgment low; fat vibrato said probe is a series of pulses, thus realizing the logic level detection.

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713