10 Way Electronic Switch

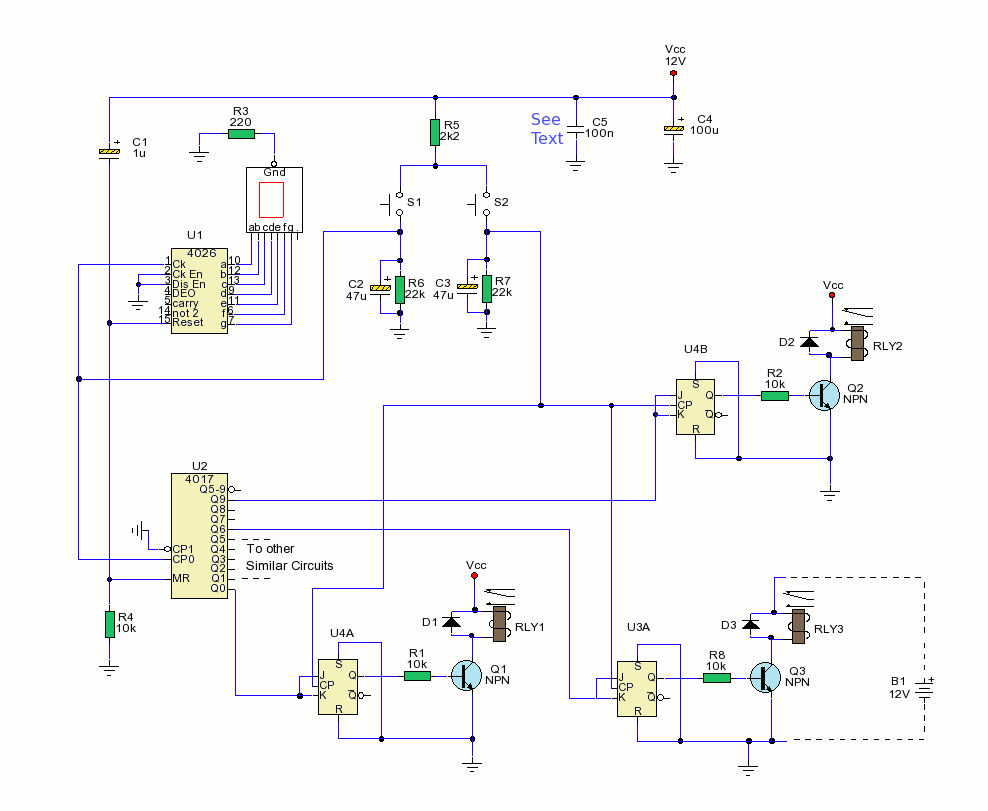

The schematic depicts two switches, S1 and S2, utilized for controlling the outputs. The primary function is executed by U2, a CMOS4017 decade counter divider integrated circuit (IC). Upon activation, capacitor C1 is swiftly charged through resistor R4, generating a brief reset pulse applied to the reset pins of both U1 and U2. Consequently, U1, which serves as a seven-segment display driver and decade counter, shows "zero" on the display, while pin 3 of the 4017 outputs a high signal. Each press of switch S1 increments the clock input of U2 by one count, allowing the display and the 4017 to cycle through all ten outputs. A separate reset switch is unnecessary since the display reflects the currently selected output. Each output can be toggled independently using a JK flip-flop, specifically a CMOS4027. When the 4017 is at a particular output, such as zero, the controlled circuit can be activated or deactivated using switch S2. To latch the output, a JK flip-flop is employed for each of the ten outputs. The 4027 includes two JK flip-flops, with only one flip-flop needed per output. If only five outputs are desired, three 4027 ICs would suffice, providing six JK flip-flops, with the unused flip-flop inputs grounded. The circuit operates as follows: when the 4017 is at output zero, pin 3 becomes high, enabling both JK inputs of the flip-flop (U4A at output zero), allowing toggling via pulses from switch S2. The Q output of each flip-flop drives an NPN transistor, which in turn activates a small relay. General-purpose NPN transistors such as 2N2222, BC108, or BC548 can be utilized. The relay facilitates control over external loads of varying voltage and current. It is important to note that VDD and VSS denote the drain and source power connections. The CMOS 4027 features two JK flip-flops, with pins S1, R1, J1, K1, CP1 representing the set, reset, J and K inputs, and clock pulse inputs for one half of the 4027. The other flip-flop is designated as S2, R2, etc. In the schematic, U3A represents one JK flip-flop or half of a 4027, while U4A and U4B utilize both JK flip-flops, constituting one complete 4027. For clarity, the schematic illustrates only outputs zero, six, and nine. Pinouts for the CMOS ICs 4017 and 4026 are also available in the practical section. If necessary, the external circuit's power supply can be employed to energize the driver transistor and relay, as indicated on output 6, with dotted lines representing power sourced from an external battery. Additionally, it is essential that the common negative terminal of the external circuit is connected to the common chassis (negative) terminal of this circuit.

The circuit design integrates a CMOS4017 decade counter and a CMOS4027 JK flip-flop to create a versatile output control system. The operation begins with the charging of capacitor C1, which ensures that both U1 and U2 are reset, setting the initial state of the system. The 4017 IC is programmed to count from 0 to 9, with each output corresponding to a specific state displayed on the seven-segment display driven by U1. The use of switch S1 allows for manual incrementing of the count, facilitating user interaction with the system.

The JK flip-flop configuration provided by the CMOS4027 adds flexibility to the output control, enabling each output to be independently set or reset. This is particularly useful in applications where multiple outputs need to be managed without interference. The inclusion of switch S2 allows for real-time toggling of the outputs, enhancing the system's responsiveness to user commands.

Transistor drivers are employed to manage larger loads through relays, providing isolation and protection for the control circuit from high-power applications. The choice of general-purpose NPN transistors ensures that the circuit can be easily assembled with commonly available components. The schematic's design also emphasizes ease of understanding, with clear labeling and logical flow, making it accessible for both novice and experienced electronics engineers.

In summary, this circuit exemplifies a practical application of digital counting and control using CMOS technology, showcasing the integration of decade counters and flip-flops to achieve a reliable and user-friendly output management system. The design considerations for power management and component selection further enhance the circuit's functionality and adaptability to various applications.The schematic is shown above, and two switches S1 and S2 are used to control the outputs. The main work is done by U2 a CMOS4017 decade counter divider IC. At switch on, C1 is quickly charged by R4 and a brief reset pulse is applied to to the reset pins of both U1 and U2. This results in U1, a 7 segment display display driver and decade counter sh owing "zero" on the 7 segment display and pin 3 (which is the output zero) of the 4017 becoming high. Each time S1 is pressed the clock input of U2 is incremented, by one count and the display and 4017 will cycle through all 10 outputs.

A separate reset switch is not provided as the display reads the currently selected output. Each output can be toggled (set or reset) independently by the use of a JK flip flop, a CMOS4027. When the 4017 is on a particular output, for example zero, then the controlled circuit can be turned on or off using switch S2. To latch the output a type JK flip-flop is used at each of the ten outputs. The 4027 contains two JK flip flops, and only one flip flop is required per output. If you only required 5 outputs, then only three 4027 IC`s are required. Three 4027 would give you six JK flip flops, the unused flip flop should have all unused inputs tied to ground.

The circuit works as follows. When the 4017 is at output zero, pin 3 will be high. This enables both JK inputs of the flip flop (U4A at output zero) and the circuit can then be toggled via pulses applied from switch S2. The `Q` output of each flip-flop drives and NPN transistor and then a small relay. The NPN transistors can be any general purpose type, e. g. 2N2222, BC108, BC548 etc. The relay allows external loads of different voltage and current to this circuit to be controlled. Please note that VDD and VSS represent the drain and source power connections. The CMOS 4027 contains two JK Flip Flops, the pins S1, R1, J1, K1, CP1 represent the set, reset, J and K inputs and clock pulse inputs for one half of the 4027.

The other flip flop is represented as S2, R2, etc. In the diagram U3A represents one JK flip flop or half of a 4027, and U4A and U4B use both JK flip flops or one complete 4027. For clarity, the schematic is drawn with outputs, zero, six and nine shown only. The pinouts for the CMOS IC`s 4017 and 4026 can be also be found in the practical section. If required, the external circuits power supply can be used to power the driver transistor and relay.

This is shown on output 6, the dotted lines representing the power coming from an external battery. The only other requirement here is that the external circuits common negative terminal is tied to this circuits common chassis (negative) terminal. 🔗 External reference

The circuit design integrates a CMOS4017 decade counter and a CMOS4027 JK flip-flop to create a versatile output control system. The operation begins with the charging of capacitor C1, which ensures that both U1 and U2 are reset, setting the initial state of the system. The 4017 IC is programmed to count from 0 to 9, with each output corresponding to a specific state displayed on the seven-segment display driven by U1. The use of switch S1 allows for manual incrementing of the count, facilitating user interaction with the system.

The JK flip-flop configuration provided by the CMOS4027 adds flexibility to the output control, enabling each output to be independently set or reset. This is particularly useful in applications where multiple outputs need to be managed without interference. The inclusion of switch S2 allows for real-time toggling of the outputs, enhancing the system's responsiveness to user commands.

Transistor drivers are employed to manage larger loads through relays, providing isolation and protection for the control circuit from high-power applications. The choice of general-purpose NPN transistors ensures that the circuit can be easily assembled with commonly available components. The schematic's design also emphasizes ease of understanding, with clear labeling and logical flow, making it accessible for both novice and experienced electronics engineers.

In summary, this circuit exemplifies a practical application of digital counting and control using CMOS technology, showcasing the integration of decade counters and flip-flops to achieve a reliable and user-friendly output management system. The design considerations for power management and component selection further enhance the circuit's functionality and adaptability to various applications.The schematic is shown above, and two switches S1 and S2 are used to control the outputs. The main work is done by U2 a CMOS4017 decade counter divider IC. At switch on, C1 is quickly charged by R4 and a brief reset pulse is applied to to the reset pins of both U1 and U2. This results in U1, a 7 segment display display driver and decade counter sh owing "zero" on the 7 segment display and pin 3 (which is the output zero) of the 4017 becoming high. Each time S1 is pressed the clock input of U2 is incremented, by one count and the display and 4017 will cycle through all 10 outputs.

A separate reset switch is not provided as the display reads the currently selected output. Each output can be toggled (set or reset) independently by the use of a JK flip flop, a CMOS4027. When the 4017 is on a particular output, for example zero, then the controlled circuit can be turned on or off using switch S2. To latch the output a type JK flip-flop is used at each of the ten outputs. The 4027 contains two JK flip flops, and only one flip flop is required per output. If you only required 5 outputs, then only three 4027 IC`s are required. Three 4027 would give you six JK flip flops, the unused flip flop should have all unused inputs tied to ground.

The circuit works as follows. When the 4017 is at output zero, pin 3 will be high. This enables both JK inputs of the flip flop (U4A at output zero) and the circuit can then be toggled via pulses applied from switch S2. The `Q` output of each flip-flop drives and NPN transistor and then a small relay. The NPN transistors can be any general purpose type, e. g. 2N2222, BC108, BC548 etc. The relay allows external loads of different voltage and current to this circuit to be controlled. Please note that VDD and VSS represent the drain and source power connections. The CMOS 4027 contains two JK Flip Flops, the pins S1, R1, J1, K1, CP1 represent the set, reset, J and K inputs and clock pulse inputs for one half of the 4027.

The other flip flop is represented as S2, R2, etc. In the diagram U3A represents one JK flip flop or half of a 4027, and U4A and U4B use both JK flip flops or one complete 4027. For clarity, the schematic is drawn with outputs, zero, six and nine shown only. The pinouts for the CMOS IC`s 4017 and 4026 can be also be found in the practical section. If required, the external circuits power supply can be used to power the driver transistor and relay.

This is shown on output 6, the dotted lines representing the power coming from an external battery. The only other requirement here is that the external circuits common negative terminal is tied to this circuits common chassis (negative) terminal. 🔗 External reference