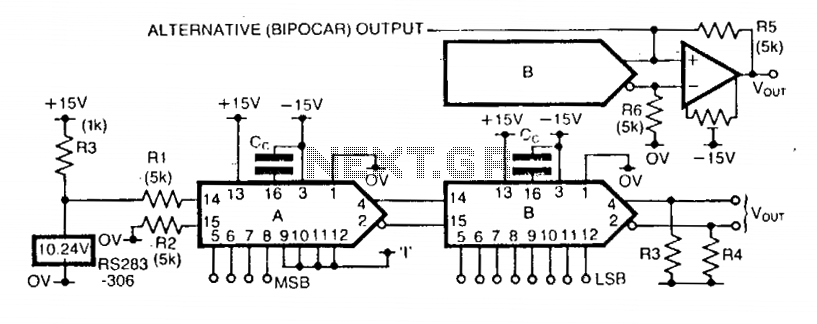

12-Bit dac with variable step size

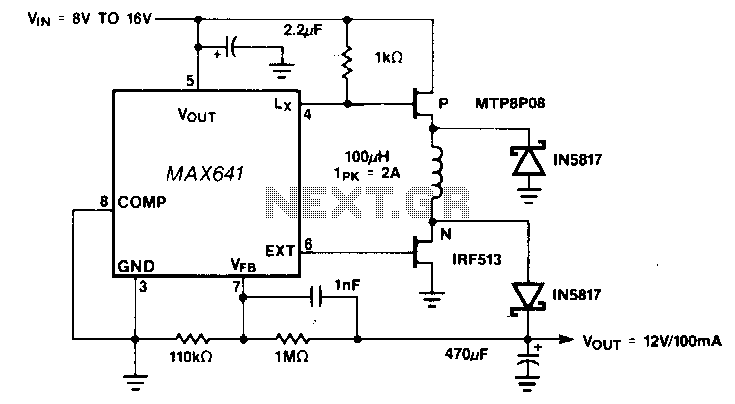

The step size of the converter is variable by selecting the high-order data bits. The first DAC, A, has a stable reference current supplied via a 10.24 V reference IC and resistor R1. Resistor R2 provides bias cancellation. Only the first four most significant bit (MSB) inputs are utilized, resulting in a step size of 225/256 * 2.048/16 = 0.127 mA. This current serves as the reference for DAC B, whose step size is then 0.1275/256 = 0.498 µA. Complementary voltage outputs are available for unipolar output, and with R3 and R4 set to 10 kΩ, the output voltage (Vout) is approximately ±10.2 V, with a step size (1 LSB) of about 5 mV. An operational amplifier can be added to the output to provide a low-impedance output with bipolar output symmetrical about ground, provided that resistors R5 and R6 are matched within 0.05%. Additionally, an offset null is required, and all resistors except R2 and R3 should be 1% high-stability types. By using lower-order address lines than those illustrated for DAC A, a smaller step size (and therefore a reduced full-scale output) can be achieved. Unused high-order bits can be manipulated to either a high or low state to alter the relative position of the full-scale output.

The described circuit utilizes a digital-to-analog converter (DAC) configuration that allows for precise control over the output current and voltage levels. The first DAC, referred to as DAC A, operates with a stable reference current sourced from a 10.24 V reference integrated circuit (IC) and a resistor (R1). The bias cancellation is achieved through the use of resistor R2, which ensures that any offset errors do not affect the output accuracy.

The choice of using only the first four MSB inputs enables the circuit to achieve a specific step size of 0.127 mA. This current is critical as it serves as the reference for the second DAC (DAC B), which has a refined step size of 0.498 µA. The complementary voltage outputs facilitate unipolar output configurations, and the design allows for an output voltage swing of approximately ±10.2 V when resistors R3 and R4 are set at 10 kΩ. The step size for the output voltage is approximately 5 mV per least significant bit (LSB), providing sufficient resolution for various applications.

In scenarios where a low-impedance output is necessary, the addition of an operational amplifier at the output stage is recommended. This amplifier can be configured to provide a bipolar output that is symmetrical about ground, contingent upon matching resistors R5 and R6 to a tolerance of 0.05%. The inclusion of an offset null feature is essential to enhance the accuracy of the output, ensuring that any inherent offsets are compensated effectively.

The circuit design also allows for flexibility in configuring the DACs. By selecting lower-order address lines for DAC A, it is possible to achieve a smaller step size and a reduced full-scale output. This capability is particularly useful in applications requiring fine-tuning of output levels. Additionally, manipulating unused high-order bits to either a high or low state can adjust the relative positioning of the full-scale output, providing further customization for specific operational requirements. This design approach ensures that the circuit can be tailored to meet a wide range of performance criteria while maintaining high accuracy and stability.The step size of the converter is variable by selection of the high order data bits. The first DAC, A, has a stable reference current supplied via the 10.24 V reference IC and Rl. R2 provides bias cancellation. As shown, only the first 4 MSB inputs are used, giving a step size of 225/256 2.048/16 = 0.127 mA. This current supplies the reference for DAC whose step size is then 0.1275/256 = 0.498 µ. Complementary voltage outputs are available for unipolar output and using R3 - R4 = 10, Vout is ± 10.2 V approximately, with a step size (1 LSB) of approximately 5 mV. If desired an op amp can be added to the output to provide a low impedance output with bipolar output symmetrical about ground, if R5 = R6 within 0.05%.

Note that offset null is required, and all resistors except R2 and R3 should be 1% high stability types. By using lower order address lines than illustrated for DAC A, a smaller step size (and therefore full-scale output) can be obtained.

Unused high order bits can be manipulated high or low to change the relative position of the full-scale output.

The described circuit utilizes a digital-to-analog converter (DAC) configuration that allows for precise control over the output current and voltage levels. The first DAC, referred to as DAC A, operates with a stable reference current sourced from a 10.24 V reference integrated circuit (IC) and a resistor (R1). The bias cancellation is achieved through the use of resistor R2, which ensures that any offset errors do not affect the output accuracy.

The choice of using only the first four MSB inputs enables the circuit to achieve a specific step size of 0.127 mA. This current is critical as it serves as the reference for the second DAC (DAC B), which has a refined step size of 0.498 µA. The complementary voltage outputs facilitate unipolar output configurations, and the design allows for an output voltage swing of approximately ±10.2 V when resistors R3 and R4 are set at 10 kΩ. The step size for the output voltage is approximately 5 mV per least significant bit (LSB), providing sufficient resolution for various applications.

In scenarios where a low-impedance output is necessary, the addition of an operational amplifier at the output stage is recommended. This amplifier can be configured to provide a bipolar output that is symmetrical about ground, contingent upon matching resistors R5 and R6 to a tolerance of 0.05%. The inclusion of an offset null feature is essential to enhance the accuracy of the output, ensuring that any inherent offsets are compensated effectively.

The circuit design also allows for flexibility in configuring the DACs. By selecting lower-order address lines for DAC A, it is possible to achieve a smaller step size and a reduced full-scale output. This capability is particularly useful in applications requiring fine-tuning of output levels. Additionally, manipulating unused high-order bits to either a high or low state can adjust the relative positioning of the full-scale output, providing further customization for specific operational requirements. This design approach ensures that the circuit can be tailored to meet a wide range of performance criteria while maintaining high accuracy and stability.The step size of the converter is variable by selection of the high order data bits. The first DAC, A, has a stable reference current supplied via the 10.24 V reference IC and Rl. R2 provides bias cancellation. As shown, only the first 4 MSB inputs are used, giving a step size of 225/256 2.048/16 = 0.127 mA. This current supplies the reference for DAC whose step size is then 0.1275/256 = 0.498 µ. Complementary voltage outputs are available for unipolar output and using R3 - R4 = 10, Vout is ± 10.2 V approximately, with a step size (1 LSB) of approximately 5 mV. If desired an op amp can be added to the output to provide a low impedance output with bipolar output symmetrical about ground, if R5 = R6 within 0.05%.

Note that offset null is required, and all resistors except R2 and R3 should be 1% high stability types. By using lower order address lines than illustrated for DAC A, a smaller step size (and therefore full-scale output) can be obtained.

Unused high order bits can be manipulated high or low to change the relative position of the full-scale output.