4-Bit Analogue to Digital Converter

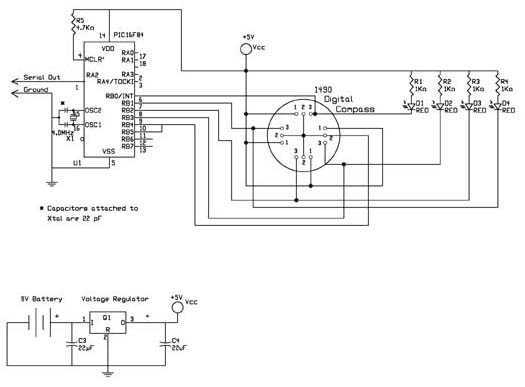

The operation of the converter relies on the weighted addition and transfer of the analog input levels to the digital output levels. It comprises comparators and resistors. Although, theoretically, the number of bits is unlimited, each bit requires a comparator and several coupling resistors. The diagram illustrates a 4-bit version. The resistor values must adhere to specific criteria: the linearity of the converter is contingent on the precision of the resistor values relative to the converter's resolution and the accuracy of the comparators' threshold voltage. This threshold level should ideally be equal to or close to half of the supply voltage. Furthermore, the comparators should exhibit minimal output resistance and maximal input resistance concerning the load resistors. Any deviation from these specifications negatively impacts the converter's linearity. When resistor values are sufficiently high, employing inverters with a field-effect transistor (FET) input creates an optimal scenario. In this converter, complementary metal-oxide semiconductor (CMOS) inverters are utilized, which, despite their low gain, provide satisfactory performance. If standard comparators are employed, it is important to consider the output voltage range and ensure that the potential at their non-inverting inputs is set to half the supply voltage. For high accuracy, comparators such as the TLC3074 or similar should be utilized, as this type features a totem-pole output. The non-inverting inputs should be interconnected and linked to the tap of a voltage divider made up of two 10 kΩ resistors across the supply lines. It is crucial for the converter to be powered by a low-resistance source, which can be achieved through an appropriate operational amplifier input buffer. The converter operates with a current draw not exceeding 5 mA.

The electronic schematic for this converter can be constructed by integrating several key components that fulfill the outlined specifications. The core of the circuit consists of multiple comparators, each configured to compare the input analog voltage against a reference voltage, which is set to half the supply voltage. This reference voltage is generated using a voltage divider composed of two resistors, each valued at 10 kΩ, ensuring that the non-inverting inputs of the comparators are consistently at the desired threshold.

Resistors play a critical role in determining the weighting of the input signals. The values of these resistors must be chosen with precision to maintain the linearity of the converter. High-precision resistors should be utilized to minimize the effects of tolerance on the overall performance of the circuit. For applications requiring high accuracy, the TLC3074 comparator is recommended due to its favorable characteristics, including a totem-pole output configuration that enhances the drive capability.

To mitigate issues related to output loading, the output of each comparator can be buffered using CMOS inverters. Although these inverters typically have a lower gain, their high input resistance and low output resistance are beneficial in preserving signal integrity throughout the conversion process. Additionally, the circuit should be designed to ensure that the current draw remains within the specified limit of 5 mA, which is crucial for battery-operated or low-power applications.

In summary, the design of this analog-to-digital converter involves careful consideration of component selection, particularly resistors and comparators, as well as the implementation of appropriate buffering to achieve optimal performance and accuracy in converting analog signals to digital outputs.The operation of the converter is based on the weighted adding and transferring of the analogue input levels and the digital output levels. It consists of comparators and resistors. In theory, the number of bits is unlimited, but each bit needs a comparator and several coupling resistors.

The diagram shows a 4-bit version. The value of the resisto rs must meet the following criteria: The linearity of the converter depends on the degree of precision of the value of the resistors with respect to the resolution of the converter, and on the accuracy of the threshold voltage of the comparators. This threshold level must be equal, or nearly so, to half the supply voltage. Moreover, the comparators must have as low an output resistance as possible and as high an input resistance with respect to the load resistors as feasible.

Any deviation from these requirements affects the linearity of the converter adversely. If the value of the resistors is not too low, the use of inverters with an FET (field-effect transistor) input leads to a near-ideal situation. In the present converter, complementary metal-oxide semiconductor (CMOS) inverters are used, which, in spite of their low gain, give a reasonably good performance.

If standard comparators are used, take into account the output voltage range and make sure that the potential at their non-inverting inputs is set to half the supply voltage. If high accuracy is a must, comparators Type TLC3074 or similar should be used. This type has a totem-pole output. The non-inverting inputs should be interlinked and connected to the tap of a a divider consisting of two 10 k resistors across the supply lines.

It is essential that the converter is driven by a low-resistance source. If necessary, this can be arranged via a suitable op amp input buffer. The converter draws a current not exceeding 5 mA. 🔗 External reference

The electronic schematic for this converter can be constructed by integrating several key components that fulfill the outlined specifications. The core of the circuit consists of multiple comparators, each configured to compare the input analog voltage against a reference voltage, which is set to half the supply voltage. This reference voltage is generated using a voltage divider composed of two resistors, each valued at 10 kΩ, ensuring that the non-inverting inputs of the comparators are consistently at the desired threshold.

Resistors play a critical role in determining the weighting of the input signals. The values of these resistors must be chosen with precision to maintain the linearity of the converter. High-precision resistors should be utilized to minimize the effects of tolerance on the overall performance of the circuit. For applications requiring high accuracy, the TLC3074 comparator is recommended due to its favorable characteristics, including a totem-pole output configuration that enhances the drive capability.

To mitigate issues related to output loading, the output of each comparator can be buffered using CMOS inverters. Although these inverters typically have a lower gain, their high input resistance and low output resistance are beneficial in preserving signal integrity throughout the conversion process. Additionally, the circuit should be designed to ensure that the current draw remains within the specified limit of 5 mA, which is crucial for battery-operated or low-power applications.

In summary, the design of this analog-to-digital converter involves careful consideration of component selection, particularly resistors and comparators, as well as the implementation of appropriate buffering to achieve optimal performance and accuracy in converting analog signals to digital outputs.The operation of the converter is based on the weighted adding and transferring of the analogue input levels and the digital output levels. It consists of comparators and resistors. In theory, the number of bits is unlimited, but each bit needs a comparator and several coupling resistors.

The diagram shows a 4-bit version. The value of the resisto rs must meet the following criteria: The linearity of the converter depends on the degree of precision of the value of the resistors with respect to the resolution of the converter, and on the accuracy of the threshold voltage of the comparators. This threshold level must be equal, or nearly so, to half the supply voltage. Moreover, the comparators must have as low an output resistance as possible and as high an input resistance with respect to the load resistors as feasible.

Any deviation from these requirements affects the linearity of the converter adversely. If the value of the resistors is not too low, the use of inverters with an FET (field-effect transistor) input leads to a near-ideal situation. In the present converter, complementary metal-oxide semiconductor (CMOS) inverters are used, which, in spite of their low gain, give a reasonably good performance.

If standard comparators are used, take into account the output voltage range and make sure that the potential at their non-inverting inputs is set to half the supply voltage. If high accuracy is a must, comparators Type TLC3074 or similar should be used. This type has a totem-pole output. The non-inverting inputs should be interlinked and connected to the tap of a a divider consisting of two 10 k resistors across the supply lines.

It is essential that the converter is driven by a low-resistance source. If necessary, this can be arranged via a suitable op amp input buffer. The converter draws a current not exceeding 5 mA. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713