5-channel low-power interface circuit programmable sensor signal processor AD7714 and DSP

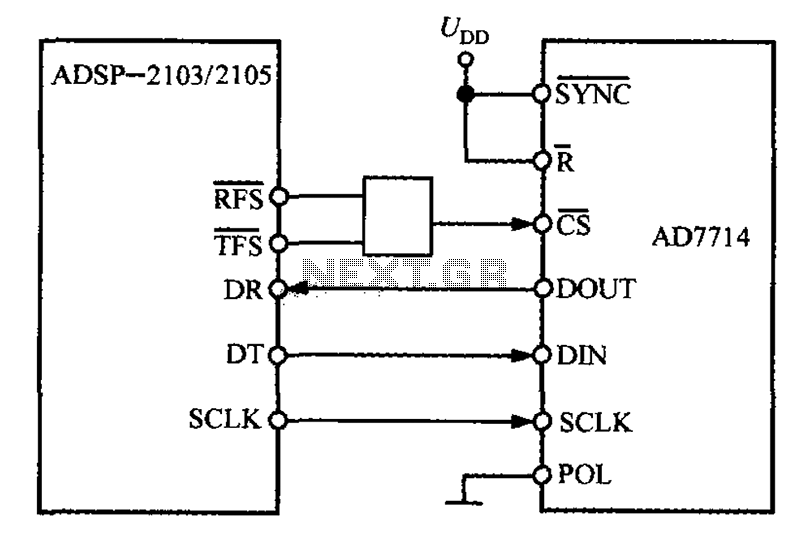

The ADSP-2103 and ADSP-2105 are digital signal processors that interface with the AD7714. When the output is active, the ADSP-2103/2105 configuration includes the RFS non-TES non-terminal set to a low level, while the SCLK terminal is configured for serial clock output. The AD7714 operates with a low level of POL termination. To ensure proper functionality of the AD7714, the serial clock frequency of the ADSP-2103/2105 must be limited to less than 3 MHz.

The ADSP-2103 and ADSP-2105 digital signal processors are designed for high-performance signal processing applications. These processors are capable of executing complex algorithms efficiently, making them suitable for various applications such as audio processing, telecommunications, and control systems.

The interface circuit with the AD7714 is critical for ensuring seamless communication between the digital signal processor and the analog-to-digital converter (ADC). The configuration of the RFS (Receive Frame Sync) non-TES (non-terminal) to a low level indicates that the processor is ready to receive data, which is essential for synchronized data transfer.

The SCLK (Serial Clock) terminal, configured for serial clock output, serves as the timing reference for data transmission between the ADSP-2103/2105 and the AD7714. It is important to maintain the serial clock frequency below 3 MHz to prevent potential data corruption and ensure reliable operation of the AD7714. Exceeding this frequency can lead to timing issues that may disrupt the ADC's ability to accurately convert analog signals to digital form.

In summary, the integration of the ADSP-2103/2105 with the AD7714 involves careful attention to configuration settings and timing requirements to achieve optimal performance. Proper setup of the RFS and SCLK terminals is crucial for the effective operation of the overall system, facilitating accurate data conversion and processing.ADSP-2103 or ADIs ADSP-2105 is produced by a digital signal processor. AD7714 and the ADSP-2103/2105 interface circuit as shown in FIG. When the output is active ADSP-2103/2105 and the RFS non-TES non-terminal configuration to the low level, the SCLK terminal is configured to serial clock output. AD7714 low level of POL termination. To ensure the AD7714 to work properly, ADSP-2103/2105 serial clock frequency should be limited to less than 3MHz.

The ADSP-2103 and ADSP-2105 digital signal processors are designed for high-performance signal processing applications. These processors are capable of executing complex algorithms efficiently, making them suitable for various applications such as audio processing, telecommunications, and control systems.

The interface circuit with the AD7714 is critical for ensuring seamless communication between the digital signal processor and the analog-to-digital converter (ADC). The configuration of the RFS (Receive Frame Sync) non-TES (non-terminal) to a low level indicates that the processor is ready to receive data, which is essential for synchronized data transfer.

The SCLK (Serial Clock) terminal, configured for serial clock output, serves as the timing reference for data transmission between the ADSP-2103/2105 and the AD7714. It is important to maintain the serial clock frequency below 3 MHz to prevent potential data corruption and ensure reliable operation of the AD7714. Exceeding this frequency can lead to timing issues that may disrupt the ADC's ability to accurately convert analog signals to digital form.

In summary, the integration of the ADSP-2103/2105 with the AD7714 involves careful attention to configuration settings and timing requirements to achieve optimal performance. Proper setup of the RFS and SCLK terminals is crucial for the effective operation of the overall system, facilitating accurate data conversion and processing.ADSP-2103 or ADIs ADSP-2105 is produced by a digital signal processor. AD7714 and the ADSP-2103/2105 interface circuit as shown in FIG. When the output is active ADSP-2103/2105 and the RFS non-TES non-terminal configuration to the low level, the SCLK terminal is configured to serial clock output. AD7714 low level of POL termination. To ensure the AD7714 to work properly, ADSP-2103/2105 serial clock frequency should be limited to less than 3MHz.

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713