Class D amp made easy with 555 timer IC

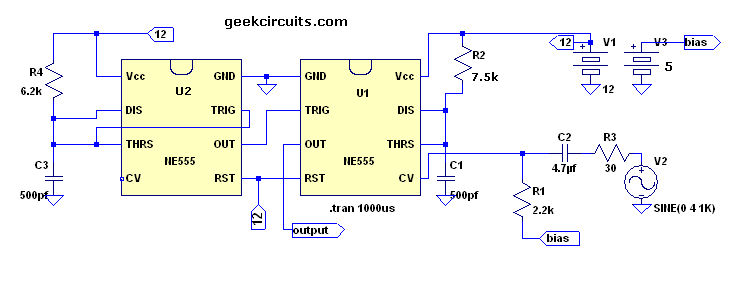

This text continues the discussion on a Class D amplifier utilizing a 555 timer chip. In reviewing previous schematics, the inclusion of a second 555 timer (U2) raises questions. The primary function of U2 is to provide a constant frequency trigger to pin 2 of U1, ensuring a stable PWM carrier frequency during audio modulation. Analyzing the circuit's performance using LTSpice simulator and testing it on a breadboard indicates that the sound quality is satisfactory. There are alternative methods to achieve similar results; however, the author is intrigued by the possibility of using U1 alone without U2 to reduce size and costs. By feeding back the output from pin 3 to the RC timing network on pins 6 and 2, the circuit operates in an astable mode with a 50% duty cycle. When audio input is applied to pin 5, distortion occurs even at lower volumes. The schematic depicted in Fig. 1 features a 555 circuit with negative feedback implemented. It is important to note that the 2N3904 transistor's hFE can vary based on production binning, potentially affecting sound quality. An op-amp may be a better choice for consistent results. By applying negative feedback through the 2N3904 transistor for self-biasing, the resulting audio quality surpasses that of using two chips. The author does not have a definitive explanation for this observation, but the waveform analysis indicates a combination of PWM and FM modulation. This unexpected outcome highlights the unique characteristics of Class D amplifiers designed in a self-oscillating mode, which are often preferred by audiophiles. Further circuit designs will be presented.

The Class D amplifier circuit described employs a 555 timer IC as the core component for generating the necessary PWM signal. The circuit utilizes two 555 timer chips, where U1 is the primary timer generating the PWM signal and U2 serves the role of maintaining a stable frequency trigger for U1. This design choice is critical for ensuring that the PWM carrier frequency remains consistent, particularly during audio modulation.

The feedback mechanism is established by connecting the output of U1 (pin 3) back to the RC timing network at pins 6 and 2. This configuration allows the circuit to operate in an astable mode, achieving a duty cycle of 50%. The astable operation is essential for effective PWM generation, which is crucial for driving the output stage of the Class D amplifier. The audio signal is applied to pin 5 of U1; however, care must be taken as distortion may occur at higher modulation levels, particularly when using the circuit at lower volume settings.

The implementation of negative feedback through a 2N3904 transistor is a notable enhancement to the circuit. This transistor allows for self-biasing of the amplifier, which can significantly improve audio fidelity by stabilizing the operating point of the output stage. It is important to consider the variations in the hFE of the 2N3904, as these can lead to differences in sound quality. For applications requiring greater consistency, the use of an operational amplifier may be advisable.

The unexpected audio quality resulting from the self-oscillating nature of the circuit presents an intriguing characteristic, as it combines both PWM and FM modulation effects. This phenomenon may provide insights into the advantages of self-oscillating Class D amplifier designs, which are often favored in high-fidelity audio applications. Future designs and modifications to this circuit will explore additional enhancements and configurations to further optimize performance.This is a continuation of my previous article regarding class d amp using 555 timer chip. Looking back to several schematics on that article, some of you may wonder why I include another 555 as U2 in the drawing. The main purpose of this U2 is to establish constant frequency trigger on pin 2 of U1 in such a way of maintaining stable PWM carrier fr

equency during audio input modulation. By scrutinizing the behavior of the circuit in LT spice simulator, and listening to their sound thru the breadboard circuit layout, the sound is good and clean. Of course there are some interesting ways in doing this but the most interesting thing for me to satisfy my curiosity is to try to use U1 alone without the trigger U2 to conserve space and cost to the lowest value as possible.

In this case, by feeding back the output pin 3 to the RC time network on pin 6 & 2 the resulting switching mode is astable with 50% duty cycle. I tried to apply music to pin 5 as usual but noticed a distorting sound even at lower volume settings.

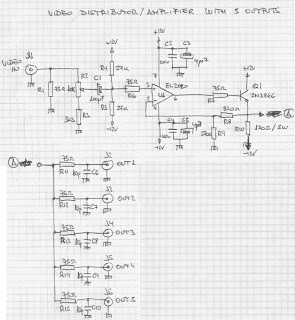

Fig. 1 Schematic of 555 circuit with negative FB added. Please take note that 2N3904 varies on their hfe depending on it`s production binning. So you may get different sound quality due to this variations. Better opt for opamp if you want. By implementing negative feedback thru the help of 2N3904 transistor to self bias it in a conventional way, (see fig. 1) the resulting sound was so good that it seems better than the sound produced by using 2 chips. Why Well, I don`t have specific answer for this question at the moment and by observing the behavior of the waveforms while the circuit is being modulated reveals a mixture of PWM and FM at the same time.

It is quite surprising for me to hear a music in class d amp having a mixture of PWM with FM owing to the fact that most of my class d design works are always time based as opposed to self oscillating approach. I think class d amp design based in self oscillating mode experience the same thing like this which makes it (self oscillating) more favored my most audiophiles.

More circuits to follow. 🔗 External reference

The Class D amplifier circuit described employs a 555 timer IC as the core component for generating the necessary PWM signal. The circuit utilizes two 555 timer chips, where U1 is the primary timer generating the PWM signal and U2 serves the role of maintaining a stable frequency trigger for U1. This design choice is critical for ensuring that the PWM carrier frequency remains consistent, particularly during audio modulation.

The feedback mechanism is established by connecting the output of U1 (pin 3) back to the RC timing network at pins 6 and 2. This configuration allows the circuit to operate in an astable mode, achieving a duty cycle of 50%. The astable operation is essential for effective PWM generation, which is crucial for driving the output stage of the Class D amplifier. The audio signal is applied to pin 5 of U1; however, care must be taken as distortion may occur at higher modulation levels, particularly when using the circuit at lower volume settings.

The implementation of negative feedback through a 2N3904 transistor is a notable enhancement to the circuit. This transistor allows for self-biasing of the amplifier, which can significantly improve audio fidelity by stabilizing the operating point of the output stage. It is important to consider the variations in the hFE of the 2N3904, as these can lead to differences in sound quality. For applications requiring greater consistency, the use of an operational amplifier may be advisable.

The unexpected audio quality resulting from the self-oscillating nature of the circuit presents an intriguing characteristic, as it combines both PWM and FM modulation effects. This phenomenon may provide insights into the advantages of self-oscillating Class D amplifier designs, which are often favored in high-fidelity audio applications. Future designs and modifications to this circuit will explore additional enhancements and configurations to further optimize performance.This is a continuation of my previous article regarding class d amp using 555 timer chip. Looking back to several schematics on that article, some of you may wonder why I include another 555 as U2 in the drawing. The main purpose of this U2 is to establish constant frequency trigger on pin 2 of U1 in such a way of maintaining stable PWM carrier fr

equency during audio input modulation. By scrutinizing the behavior of the circuit in LT spice simulator, and listening to their sound thru the breadboard circuit layout, the sound is good and clean. Of course there are some interesting ways in doing this but the most interesting thing for me to satisfy my curiosity is to try to use U1 alone without the trigger U2 to conserve space and cost to the lowest value as possible.

In this case, by feeding back the output pin 3 to the RC time network on pin 6 & 2 the resulting switching mode is astable with 50% duty cycle. I tried to apply music to pin 5 as usual but noticed a distorting sound even at lower volume settings.

Fig. 1 Schematic of 555 circuit with negative FB added. Please take note that 2N3904 varies on their hfe depending on it`s production binning. So you may get different sound quality due to this variations. Better opt for opamp if you want. By implementing negative feedback thru the help of 2N3904 transistor to self bias it in a conventional way, (see fig. 1) the resulting sound was so good that it seems better than the sound produced by using 2 chips. Why Well, I don`t have specific answer for this question at the moment and by observing the behavior of the waveforms while the circuit is being modulated reveals a mixture of PWM and FM at the same time.

It is quite surprising for me to hear a music in class d amp having a mixture of PWM with FM owing to the fact that most of my class d design works are always time based as opposed to self oscillating approach. I think class d amp design based in self oscillating mode experience the same thing like this which makes it (self oscillating) more favored my most audiophiles.

More circuits to follow. 🔗 External reference