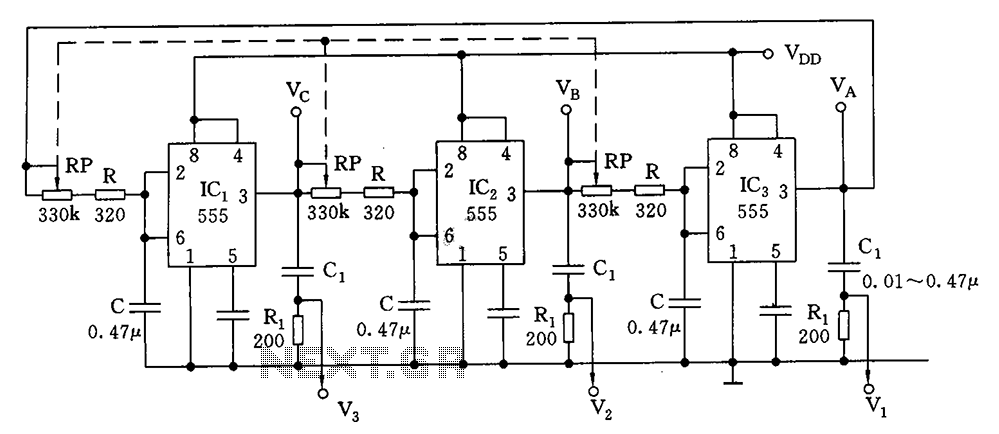

Closed-loop three-phase multivibrator

This circuit is a closed loop consisting of three identical Schmitt triggers connected in series. Each flip-flop has a delay time of td = (RP + R)C, where C represents the capacitance and RP is the resistance in the circuit. The delay rise time required to reach 1/3 of VDD is determined by this configuration. When the 555 timer is reset, the capacitor C charges through the resistor R, while the output at the third stage of the integrated circuit (pin 3) sinks current to discharge the capacitor. This results in a charging time constant for C that is consistent throughout the loop. Consequently, each output from the flip-flop requires a transition time that involves three monostable trigger circuits, leading to a total output period of Td = 6td. The corresponding frequency can be calculated based on this output period.

The circuit described features a closed-loop configuration of three identical Schmitt triggers, which serve as key elements in generating delayed output signals. Each Schmitt trigger flip-flop introduces a defined delay, calculated as td = (RP + R)C, where RP is the resistance associated with the charging path and R is an additional resistance in the circuit. The charging and discharging behavior of the capacitor C is critical for the timing characteristics of the entire circuit.

The rise time to achieve 1/3 of the supply voltage (VDD) is a significant parameter, as it establishes the responsiveness of the circuit during transitions. The 555 timer, a versatile component often used in timing applications, is reset to initiate the charging process of capacitor C through resistor R. The output from the third stage of the Schmitt trigger configuration (pin 3 of the IC) plays a crucial role in controlling the discharge path for the capacitor, effectively managing the time constant for charging and discharging cycles.

Each transition at the output of the flip-flop necessitates the engagement of three monostable trigger circuits, thereby amplifying the total time required for a complete output cycle. As a result, the overall output period (Td) is expressed as Td = 6td, indicating that the output signal's frequency is inversely proportional to this period. The design ensures that precise timing intervals can be achieved, making it suitable for applications that require controlled signal generation and timing management. This configuration is particularly advantageous in various electronic applications where timing accuracy is critical. As shown, this is a closed loop made up of three identical composition of the Schmitt trigger, end to end. Each flip-flop delay is td l. 1 (RP + R) C, i.e., the voltage on C td delay rise time required for the 1/3 VDD. The 555 is reset, the charge on C by R, W output end of the previous stage IC (3 feet) of sink current discharge, and thus the charging time constant C of the same. Thus, each output of the flip-flop every time you want to change through three monostable trigger circuit transmission, the time required is 3td.

Therefore, each IC output period Td 6td. The corresponding frequency

The circuit described features a closed-loop configuration of three identical Schmitt triggers, which serve as key elements in generating delayed output signals. Each Schmitt trigger flip-flop introduces a defined delay, calculated as td = (RP + R)C, where RP is the resistance associated with the charging path and R is an additional resistance in the circuit. The charging and discharging behavior of the capacitor C is critical for the timing characteristics of the entire circuit.

The rise time to achieve 1/3 of the supply voltage (VDD) is a significant parameter, as it establishes the responsiveness of the circuit during transitions. The 555 timer, a versatile component often used in timing applications, is reset to initiate the charging process of capacitor C through resistor R. The output from the third stage of the Schmitt trigger configuration (pin 3 of the IC) plays a crucial role in controlling the discharge path for the capacitor, effectively managing the time constant for charging and discharging cycles.

Each transition at the output of the flip-flop necessitates the engagement of three monostable trigger circuits, thereby amplifying the total time required for a complete output cycle. As a result, the overall output period (Td) is expressed as Td = 6td, indicating that the output signal's frequency is inversely proportional to this period. The design ensures that precise timing intervals can be achieved, making it suitable for applications that require controlled signal generation and timing management. This configuration is particularly advantageous in various electronic applications where timing accuracy is critical. As shown, this is a closed loop made up of three identical composition of the Schmitt trigger, end to end. Each flip-flop delay is td l. 1 (RP + R) C, i.e., the voltage on C td delay rise time required for the 1/3 VDD. The 555 is reset, the charge on C by R, W output end of the previous stage IC (3 feet) of sink current discharge, and thus the charging time constant C of the same. Thus, each output of the flip-flop every time you want to change through three monostable trigger circuit transmission, the time required is 3td.

Therefore, each IC output period Td 6td. The corresponding frequency