Cosimulation with Analog-RF Systems

The simulation of behavioral DSP designs alongside analog/RF circuit designs is essential for the successful integration of components, devices, and subsystems in modern wireless applications. Verifying the effects of real-world analog/RF issues on DSP algorithms, and vice versa, within a tightly integrated environment is highly advantageous. For simpler designs, separate simulators can be employed for signal processing and analog/RF segments, and their results can be integrated. However, contemporary designs that integrate analog/RF components with dedicated on-chip DSP blocks demand a high degree of integration at the boundary of these two environments. Advanced Design System (ADS) co-simulation capabilities address this requirement. ADS Ptolemy facilitates signal processing simulation, while either the Circuit Envelope or High-Frequency SPICE (Transient) simulators handle analog/RF simulation. Other co-simulation methods may involve incorporating MATLAB components or HDL blocks within a signal processing simulation. This document discusses co-simulation with analog/RF systems. For details on analog/RF co-simulation using Cadence, refer to the Cadence Library Integration documentation. Specific instructions can be found in the section on running a DSP and Analog - RF co-simulation with RFIC Dynamic Link. A figure illustrates a combination of RF circuitry and DSP components. ADS offers various analog/RF circuit simulators, including Linear, Harmonic Balance, Circuit Envelope, High-Frequency SPICE, and Convolution. For signal processing simulation, ADS Ptolemy is utilized. Only circuits simulated with Circuit Envelope or High-Frequency SPICE can be instantiated as subnetworks and integrated into a signal processing schematic. These circuit blocks can be simulated in conjunction with signal processing components. The necessary steps for co-simulation are outlined in the subsequent section. In the analog/RF circuit schematic window, create a circuit schematic that includes a simulation component for either Circuit Envelope (denoted as ENV) or High-Frequency SPICE simulation (denoted as TRAN). In the preceding figure, a diode rectifier is set to be simulated using the Circuit Envelope simulator. Subsequently, this subnetwork will be placed in the signal processing schematic, represented as a block. To include the previously created circuit subnetwork(s) in the signal processing schematic, select Component > Component Library. Opened projects will be displayed at the top of the list. Circuit projects are labeled with (A/RF) at the end. As previously mentioned, ADS Ptolemy can only co-simulate with the Circuit Envelope or High-Frequency SPICE simulators. Any circuit simulation control components other than ENV or TRAN (such as those for harmonic balance or S-parameter simulation) will be disregarded in the co-simulation from the signal processing schematic. Both Circuit Envelope and Transient simulators manage time-domain signals. Consequently, signal processing components connected to the circuit subnetwork must be of the timed type. If the input component (linking signal processing components to the circuit) generates numeric data, an appropriate numeric-to-timed converter (such as float-to-timed or complex-to-timed) must be included in the schematic. These components, found in the Signal Converters library, ensure that the input to the circuit subnetwork is in the time domain. For additional information, refer to Time Converters. Automatic Verification Modeling is a simulation mode that can significantly expedite previously lengthy co-simulations of analog/RF circuits. This mode can be activated in the Circuit Envelope Simulation Controller. When enabled, it characterizes an analog subcircuit into a behavioral model, which is then used to predict the response of the subcircuit at each time point. For more details about Automatic Verification Modeling, see the relevant documentation. On UNIX platforms, it is necessary to copy an example project to a directory with write permissions. On Windows platforms, it is possible to work directly within the Examples directories; however, copying examples to a working directory is preferred. In the To Project area, select Startup Directory or Working Directory to designate the destination directory for the copied project. Click Browse to choose an alternate directory. In the ADS Main window, select File > Open Project to access the Open Project dialog box. In the Directories list, select the directory where the example was copied. In the DUT_Mixer, double-click the Envelope simulation controller to open its configuration dialog. Select the Cosim tab and click Enable AVM (Fast Cosim) to activate the mode. To enable AVM (Fast Cosim) directly on the schematic, click the Display tab on the Circuit Envelope setup dialog. Set the ABM_Mode parameter to yes to enable the mode, or to no to disable it. Clustering defines the boundaries between signal processing and analog/RF simulators. Initially, this boundary is established through circuit schematics, where circuit subnetworks are defined and subsequently instantiated on the Signal Processing schematic. However, clustering involves additional considerations beyond the two schematics. Circuit subnetworks that are directly connected in the Signal Processing schematic are automatically clustered and treated as a single circuit subnetwork. Therefore, only one circuit simulation control component should be used in any directly connected subnetworks. If two circuit subnetworks defined on separate circuit schematics are linked on a Signal Processing schematic, they will be clustered into one automatically, a process that does not require user intervention. Nonetheless, if each subnetwork employs its own simulation controller, the circuit engine may encounter ambiguity regarding which controller to utilize, resulting in an error message. Another aspect of clustering occurs when circuit components available on the Signal Processing schematic (such as resistors in the initial release of Advanced Design System) are connected to a circuit subnetwork. In such cases, these resistors will be absorbed into the circuit subnetwork during clustering and simulated as part of that subnetwork. Circuit subnetworks that create a feedback loop through signal processing components necessitate the inclusion of a delay component in the feedback loop to facilitate scheduling of the signal processing simulation. If a delay is absent, an error message will be generated. To enable automatic insertion of the delay, it is essential to modify the parameters of the DF (data flow) controller. This can be accomplished by double-clicking the controller, selecting the Options tab, and then adjusting the eq parameter.Simulation of behavioral DSP designs along with analog/RF circuit designs is critical to the success of the integrated components, devices, and subsystems used in today`s wireless applications. The need to verify the impact of real-world analog/RF issues on the DSP algorithms and vice versa in a tightly integrated environment is highly desirable.

For designs of low complexity, it is possible to use separate simulators for the signal processing and analog/RF portions and then integrate the results. However, today`s state-of-the-art designs using a mix of analog/RF and dedicated on-chip DSP blocks require high levels of integration at the two-environment boundary.

Advanced Design System cosimulation between signal processing and circuits addresses this need. ADS Ptolemy provides the signal processing simulation, while the analog/RF simulation is provided by either the Circuit Envelope or High-Frequency SPICE (Transient) simulators. Other types of cosimulation include placing MATLAB components or HDL blocks in a signal processing simulation.

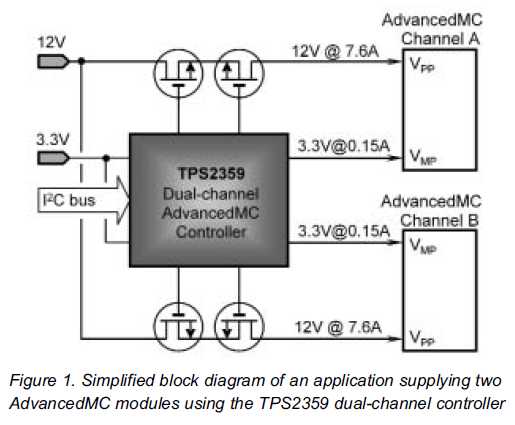

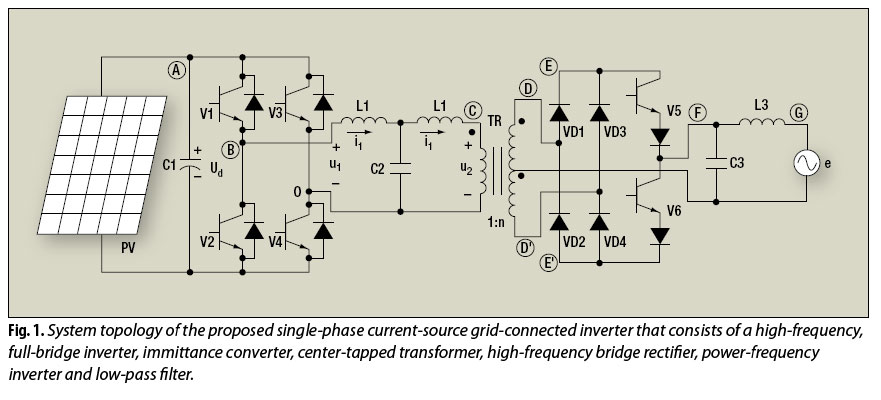

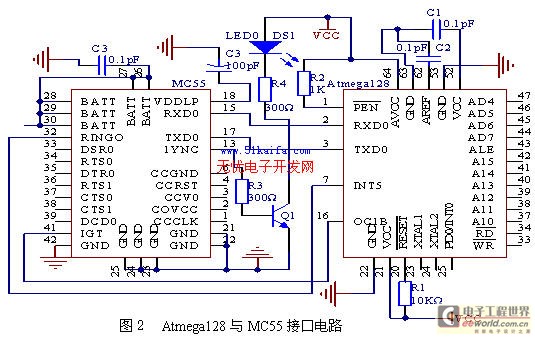

This topic describes cosimulation with analog/RF systems. For information on A/RF cosimulation with Cadence refer to the Cadence Library Integration documentation. For specific details, see Running a DSP and Analog - RF Cosimulation with RFIC Dynamic Link. The following figure shows a mixture of RF circuitry and DSP components. ADS provides a variety of analog/RF circuit simulators, including Linear, Harmonic Balance, Circuit Envelope, High-Frequency SPICE, and Convolution.

For signal processing simulation, ADS Ptolemy is used. Only circuits simulated with either Circuit Envelope or High-Frequency SPICE can be instantiated as a subnetwork and included in a signal processing schematic. These circuit blocks can then be simulated along with signal processing components. The steps needed for cosimulation are described in the next section. In the analog/RF circuit Schematic window, create a circuit schematic that includes a simulation component for either Circuit Envelope (called ENV) or High-Frequency SPICE simulation (called TRAN).

In the previous figure, a diode rectifier is set to be simulated with the Circuit Envelope simulator. Next, we will place this subnetwork in the signal processing schematic where it will be represented as a block.

To place the circuit subnetwork(s) you have already created in the signal processing schematic, choose Component > Component Library. Your opened projects are listed at the top of the list. Circuit projects have (A/RF) at the end. As stated earlier, ADS Ptolemy can cosimulate with only the Circuit Envelope or High-Frequency SPICE simulators.

Any circuit simulation control components other than ENV or TRAN (such as for harmonic balance or S-parameter simulation) are ignored in the cosimulation from the signal processing schematic. Both Circuit Envelope and Transient simulators deal with time-domain signals. Therefore, signal processing components connected to the circuit subnetwork must be the timed type. If the input component (connecting signal processing components to the circuit) produces numeric data, place an appropriate numeric-to-timed converter (such as float-to-timed or complex-to-timed) in your schematic.

These components (located in the Signal Converters library) ensure that the input into the circuit subnetwork is in the time domain. Refer to Time Converters for more information. Automatic Verification Modeling is a simulation mode that can significantly accelerate formerly lengthy cosimulations of Analog/RF circuits.

You can enable Automatic Verification Modeling in the Circuit Envelope Simulation Controller. When enabled, this mode characterizes an analog subcircuit into a behavior model, then the model is used to predict the response of the subcircuit at each time point. For details about Automatic Verification Modeling, see Automatic Verification Modeling. On UNIX platforms, you must copy an example project to a directory for which you have write permission.

On Windows platforms, you can work directly in the Examples directories; however, it`s better to copy examples to a working directory. In the To Project area, click Startup Directory or Working Directory to select the destination directory for the copied project.

Click Browse to select another directory. In the ADS Main window, choose File > Open Project to open the Open Project dialog box. In the Directories list, select the directory to which you copied the example. In the DUT_Mixer, double-click the Envelope simulation controller to open its setup dialog. Select the Cosim tab, and click Enable AVM (Fast Cosim) to enable the mode. To enable AVM (Fast Cosim) directly on the schematic, click the Display tab on the Circuit Envelope setup dialog. Enable the ABM_Mode parameter. On the schematic, set ABM_Mode=yes to enable the mode; set ABM_Mode=no to disable the mode. Clustering is the process of defining the boundaries of the signal processing and analog/RF simulators.

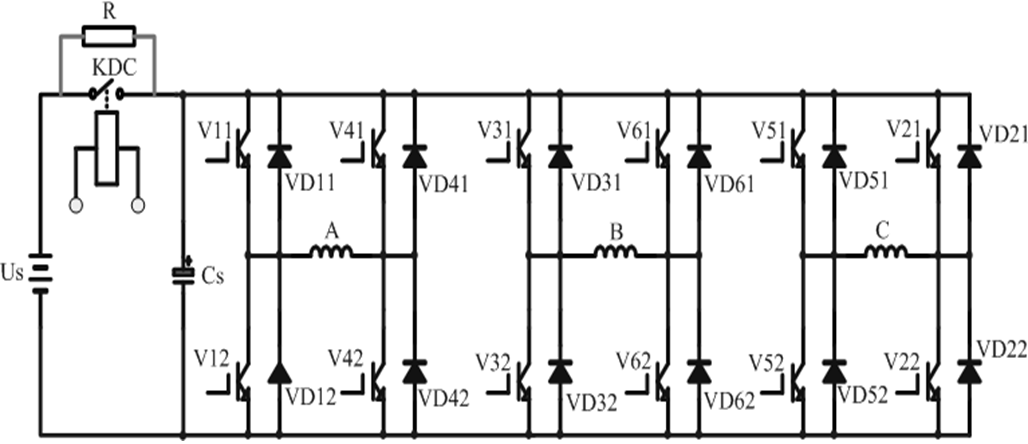

Initially, this boundary is defined by circuit schematics, where you define the circuit subnetworks and then make an instance of those on the Signal Processing schematic. However, there is a bit more to clustering than what is on the two schematics. Circuit subnetworks directly connected in the Signal Processing schematic are automatically clustered and treated as one circuit subnetwork, as shown in the following figure.

Therefore, use only one circuit simulation control component in either of the two (or more) directly connected subnetworks. When two circuit subnetworks defined on two different circuit schematics are connected on a Signal Processing schematic, the two circuit subnetworks are clustered into one (this is done transparently and should not concern the user).

However, if each of these two circuit subnetworks use their own simulation controller, then the circuit engine would not know which one to choose for simulation and would result in an error message. Another aspect of clustering is when circuit components available on the Signal Processing schematic (resistors in the first release of Advanced Design System) are connected to a circuit subnetwork.

In this case, such resistors will be absorbed into the circuit subnetwork during the clustering and will be simulated by the circuit engine as part of circuit subnetwork. Circuit subnetworks that form a feedback loop via signal processing components require a delay component in the feedback loop to facilitate the signal processing simulation scheduling, as shown in the following two figures.

If such a delay is not present, an error message will be issued. To have the program automatically insert the delay, you must edit the DF (data flow) controller parameters. To do this, double-click the controller, choose the Options tab, then eq parameter. 🔗 External reference

For designs of low complexity, it is possible to use separate simulators for the signal processing and analog/RF portions and then integrate the results. However, today`s state-of-the-art designs using a mix of analog/RF and dedicated on-chip DSP blocks require high levels of integration at the two-environment boundary.

Advanced Design System cosimulation between signal processing and circuits addresses this need. ADS Ptolemy provides the signal processing simulation, while the analog/RF simulation is provided by either the Circuit Envelope or High-Frequency SPICE (Transient) simulators. Other types of cosimulation include placing MATLAB components or HDL blocks in a signal processing simulation.

This topic describes cosimulation with analog/RF systems. For information on A/RF cosimulation with Cadence refer to the Cadence Library Integration documentation. For specific details, see Running a DSP and Analog - RF Cosimulation with RFIC Dynamic Link. The following figure shows a mixture of RF circuitry and DSP components. ADS provides a variety of analog/RF circuit simulators, including Linear, Harmonic Balance, Circuit Envelope, High-Frequency SPICE, and Convolution.

For signal processing simulation, ADS Ptolemy is used. Only circuits simulated with either Circuit Envelope or High-Frequency SPICE can be instantiated as a subnetwork and included in a signal processing schematic. These circuit blocks can then be simulated along with signal processing components. The steps needed for cosimulation are described in the next section. In the analog/RF circuit Schematic window, create a circuit schematic that includes a simulation component for either Circuit Envelope (called ENV) or High-Frequency SPICE simulation (called TRAN).

In the previous figure, a diode rectifier is set to be simulated with the Circuit Envelope simulator. Next, we will place this subnetwork in the signal processing schematic where it will be represented as a block.

To place the circuit subnetwork(s) you have already created in the signal processing schematic, choose Component > Component Library. Your opened projects are listed at the top of the list. Circuit projects have (A/RF) at the end. As stated earlier, ADS Ptolemy can cosimulate with only the Circuit Envelope or High-Frequency SPICE simulators.

Any circuit simulation control components other than ENV or TRAN (such as for harmonic balance or S-parameter simulation) are ignored in the cosimulation from the signal processing schematic. Both Circuit Envelope and Transient simulators deal with time-domain signals. Therefore, signal processing components connected to the circuit subnetwork must be the timed type. If the input component (connecting signal processing components to the circuit) produces numeric data, place an appropriate numeric-to-timed converter (such as float-to-timed or complex-to-timed) in your schematic.

These components (located in the Signal Converters library) ensure that the input into the circuit subnetwork is in the time domain. Refer to Time Converters for more information. Automatic Verification Modeling is a simulation mode that can significantly accelerate formerly lengthy cosimulations of Analog/RF circuits.

You can enable Automatic Verification Modeling in the Circuit Envelope Simulation Controller. When enabled, this mode characterizes an analog subcircuit into a behavior model, then the model is used to predict the response of the subcircuit at each time point. For details about Automatic Verification Modeling, see Automatic Verification Modeling. On UNIX platforms, you must copy an example project to a directory for which you have write permission.

On Windows platforms, you can work directly in the Examples directories; however, it`s better to copy examples to a working directory. In the To Project area, click Startup Directory or Working Directory to select the destination directory for the copied project.

Click Browse to select another directory. In the ADS Main window, choose File > Open Project to open the Open Project dialog box. In the Directories list, select the directory to which you copied the example. In the DUT_Mixer, double-click the Envelope simulation controller to open its setup dialog. Select the Cosim tab, and click Enable AVM (Fast Cosim) to enable the mode. To enable AVM (Fast Cosim) directly on the schematic, click the Display tab on the Circuit Envelope setup dialog. Enable the ABM_Mode parameter. On the schematic, set ABM_Mode=yes to enable the mode; set ABM_Mode=no to disable the mode. Clustering is the process of defining the boundaries of the signal processing and analog/RF simulators.

Initially, this boundary is defined by circuit schematics, where you define the circuit subnetworks and then make an instance of those on the Signal Processing schematic. However, there is a bit more to clustering than what is on the two schematics. Circuit subnetworks directly connected in the Signal Processing schematic are automatically clustered and treated as one circuit subnetwork, as shown in the following figure.

Therefore, use only one circuit simulation control component in either of the two (or more) directly connected subnetworks. When two circuit subnetworks defined on two different circuit schematics are connected on a Signal Processing schematic, the two circuit subnetworks are clustered into one (this is done transparently and should not concern the user).

However, if each of these two circuit subnetworks use their own simulation controller, then the circuit engine would not know which one to choose for simulation and would result in an error message. Another aspect of clustering is when circuit components available on the Signal Processing schematic (resistors in the first release of Advanced Design System) are connected to a circuit subnetwork.

In this case, such resistors will be absorbed into the circuit subnetwork during the clustering and will be simulated by the circuit engine as part of circuit subnetwork. Circuit subnetworks that form a feedback loop via signal processing components require a delay component in the feedback loop to facilitate the signal processing simulation scheduling, as shown in the following two figures.

If such a delay is not present, an error message will be issued. To have the program automatically insert the delay, you must edit the DF (data flow) controller parameters. To do this, double-click the controller, choose the Options tab, then eq parameter. 🔗 External reference