Current Limiter - Support Material

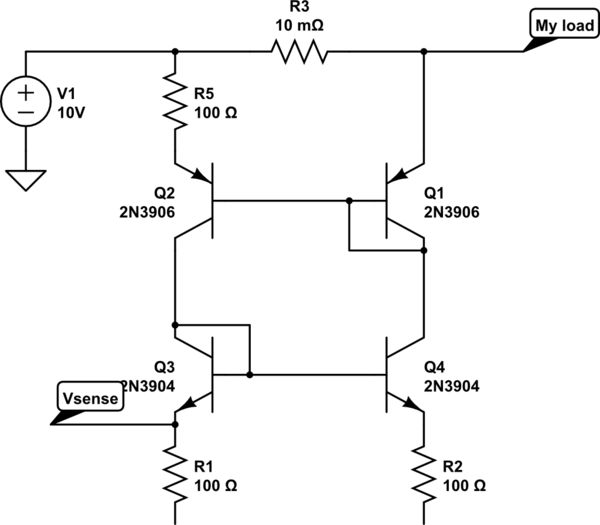

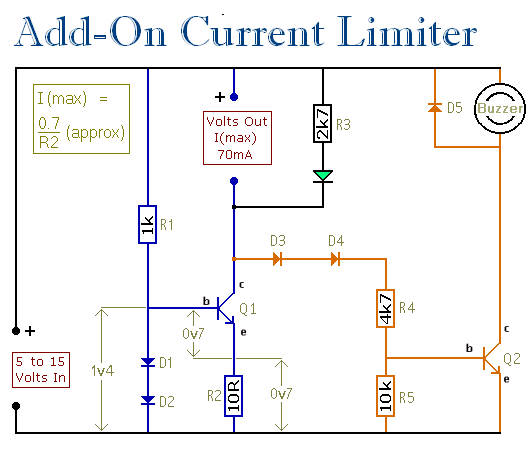

This circuit establishes a maximum limit on the current available from the output terminals by controlling the maximum current that can flow through Q1. The output terminals are in series with Q1, meaning that limiting the current through Q1 also restricts the output current. The negative output terminal connects to the collector of Q1, so any current drawn from the positive terminal flows into the collector of Q1. Consequently, the collector current is supplied by the output terminals. The base current of Q1 is provided by R1, while the emitter current flows to ground through R2 and is the sum of the collector and base currents. Due to the relatively small base current, it can be disregarded for practical purposes, allowing the emitter current to be considered equal to the collector current. Thus, setting a limit on the emitter current also limits the collector current, which in turn limits the current available from the output terminals. The key to limiting the Q1 emitter current is to establish a maximum limit on the transistor's base voltage, which is the role of diodes D1 and D2. Each diode has a forward voltage drop of approximately 0.7V, and together they prevent the base voltage of Q1 from exceeding about 1.4V. While it may be lower, it cannot exceed this value. Effectively, D1 and D2 function like a 1.4V zener diode. The voltage on the base of a silicon NPN transistor is typically about 0.7V higher than the emitter voltage. Therefore, when D1 and D2 restrict the base voltage of Q1 to a maximum of 1.4V, they also limit the voltage across R2 to about 0.7V. If the maximum voltage across R2 is 0.7V, then the maximum current through it is 0.7V / R2. In the schematic, R2 is a 10-ohm resistor, resulting in a maximum current of 0.7V / 10Ω = 70mA. R2 is connected in series with Q1 and the output terminals, meaning that if 70mA is the maximum current through R2, it is also the maximum current through the transistor and between the output terminals, even in the event of a short circuit. To illustrate this functionality, consider the scenario without the diodes, where the output terminals are shorted. As the base current through R1 activates the transistor, current begins to flow through both the transistor and R2, causing the voltage across R2 to increase. This rise in voltage results in an increase in emitter voltage. Since the base voltage is always 0.7V higher than the emitter voltage, the base voltage will likewise increase. Eventually, with a 12V supply, the maximum current flowing through the output terminals, the transistor, and R2 could reach approximately (V / R) = (12V / 10Ω) = 1.2A. However, with D1 and D2 in place, the base of Q1 is limited to a maximum of 1.4V, preventing the base voltage from rising with the emitter voltage. As a result, the emitter voltage cannot exceed 0.7V, ensuring that the maximum current flowing between the output terminals is one that results in a 0.7V drop across R2: I(max) = (V / R2) = (0.7V / 10Ω) = 70mA. If the emitter voltage attempts to exceed 0.7V, the base-emitter junction will lose its forward bias, causing the transistor to begin turning off. This will decrease the current through R2, leading to a voltage drop across it, which in turn restores the forward bias to the base-emitter junction, allowing the current through R2 to stabilize.This circuit places a maximum limit on the current available from the output terminals. It does this by limiting the maximum current that can flow through Q1. Because the output terminals are in series with Q1 - limiting the Q1 current also limits the output current. = The negative output terminal is connected to the collector of Q1. So any curren t drawn from the positive terminal - flows into the collector of Q1. = Thus - the Q1 collector current is supplied by the output terminals. The Q1 base current is supplied by R1. And the Q1 emitter current - flowing to ground through R2 - is the sum of the collector current and the base current. Because the base current is relatively small - for present purposes - it can be ignored. And you can think of the emitter current as being equal to the collector current. = Or - to put it the other way round - the collector current is equal to the emitter current. So - if you set a limit on the size of the emitter current - you also set a limit on the size of the collector current.

That is - you set a limit on the amount of current available from the output terminals. = The key to limiting the Q1 emitter current - is to set a maximum limit on the transistor`s base voltage. That`s the purpose of D1 & D2 Each diode has a forward voltage drop of about 0v7. The two together prevent the base voltage of Q1 from rising above about 1v4. It may be lower than 1v4 - but it cannot go higher than 1v4. In effect - D1 & D2 are acting like a 1v4 zener diode. = The voltage on the base of a silicon NPN transistor is always about 0v7 higher than the voltage on its emitter.

So - when D1 & D2 prevent the voltage on the base of Q1 from rising above 1v4 - they also prevent the voltage across R2 from rising above about 0v7. It may be lower than 0v7 - but it cannot go higher than 0v7. = If the maximum possible voltage across R2 is 0v7 - then the maximum possible current through it is 0.

7 G· R2. In the drawing - R2 is a 10 ohm resistor. And the maximum current that will flow through it is: - 0. 7 G· 10 = 70mA. = R2 is connected in series with Q1 and the output terminals. If 70mA is the largest current that can flow through R2 - it`s also the largest current that will flow through the transistor. And - it`s the maximum current that will flow between the output terminals - even if they`re shorted together.

= To understand how this works - first consider what would happen if the diodes were not present - and the output terminals were shorted together. = As the base current through R1 begins to turn the transistor on - current will start to flow through both the transistor and R2.

So the voltage across R2 will begin to rise. This causes the voltage on the emitter to rise. And - since the base is always 0v7 higher than the emitter - the voltage on the base is carried upwards by the emitter. = Eventually, virtually the whole of the supply voltage will appears across R2. So - with a 12-volt supply - the maximum current flowing through the output terminals, the transistor and R2 is roughly (V G· R) = (12 G· 10) = 1.

2 amps = Now consider the same situation with D1 & D2 in place. The two diodes prevent the base of Q1 from rising above 1v4. This means that the base voltage cannot ride up on the back of the emitter. = The base cannot go higher than 1v4. So the emitter voltage cannot go higher than 0v7. And the highest current that will flow between the output terminals - is one that cause a drop of 0v7 across R2. That is: I(max) = (V G· R2) = (0. 7 G· 10) = 70mA. = Consider what would happen if the voltage on the emitter tended to rise above 0v7. The base-emitter junction would no longer be forward biased. So the transistor would begin to turn off. This would lead to a fall in the current flowing through R2 - resulting in a drop in the voltage across it.

This drop in voltage would restore the forward bias to the base-emitter junction - and the current through R2 wou 🔗 External reference

That is - you set a limit on the amount of current available from the output terminals. = The key to limiting the Q1 emitter current - is to set a maximum limit on the transistor`s base voltage. That`s the purpose of D1 & D2 Each diode has a forward voltage drop of about 0v7. The two together prevent the base voltage of Q1 from rising above about 1v4. It may be lower than 1v4 - but it cannot go higher than 1v4. In effect - D1 & D2 are acting like a 1v4 zener diode. = The voltage on the base of a silicon NPN transistor is always about 0v7 higher than the voltage on its emitter.

So - when D1 & D2 prevent the voltage on the base of Q1 from rising above 1v4 - they also prevent the voltage across R2 from rising above about 0v7. It may be lower than 0v7 - but it cannot go higher than 0v7. = If the maximum possible voltage across R2 is 0v7 - then the maximum possible current through it is 0.

7 G· R2. In the drawing - R2 is a 10 ohm resistor. And the maximum current that will flow through it is: - 0. 7 G· 10 = 70mA. = R2 is connected in series with Q1 and the output terminals. If 70mA is the largest current that can flow through R2 - it`s also the largest current that will flow through the transistor. And - it`s the maximum current that will flow between the output terminals - even if they`re shorted together.

= To understand how this works - first consider what would happen if the diodes were not present - and the output terminals were shorted together. = As the base current through R1 begins to turn the transistor on - current will start to flow through both the transistor and R2.

So the voltage across R2 will begin to rise. This causes the voltage on the emitter to rise. And - since the base is always 0v7 higher than the emitter - the voltage on the base is carried upwards by the emitter. = Eventually, virtually the whole of the supply voltage will appears across R2. So - with a 12-volt supply - the maximum current flowing through the output terminals, the transistor and R2 is roughly (V G· R) = (12 G· 10) = 1.

2 amps = Now consider the same situation with D1 & D2 in place. The two diodes prevent the base of Q1 from rising above 1v4. This means that the base voltage cannot ride up on the back of the emitter. = The base cannot go higher than 1v4. So the emitter voltage cannot go higher than 0v7. And the highest current that will flow between the output terminals - is one that cause a drop of 0v7 across R2. That is: I(max) = (V G· R2) = (0. 7 G· 10) = 70mA. = Consider what would happen if the voltage on the emitter tended to rise above 0v7. The base-emitter junction would no longer be forward biased. So the transistor would begin to turn off. This would lead to a fall in the current flowing through R2 - resulting in a drop in the voltage across it.

This drop in voltage would restore the forward bias to the base-emitter junction - and the current through R2 wou 🔗 External reference