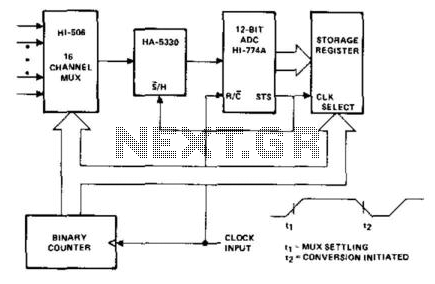

Data Acquisition System I

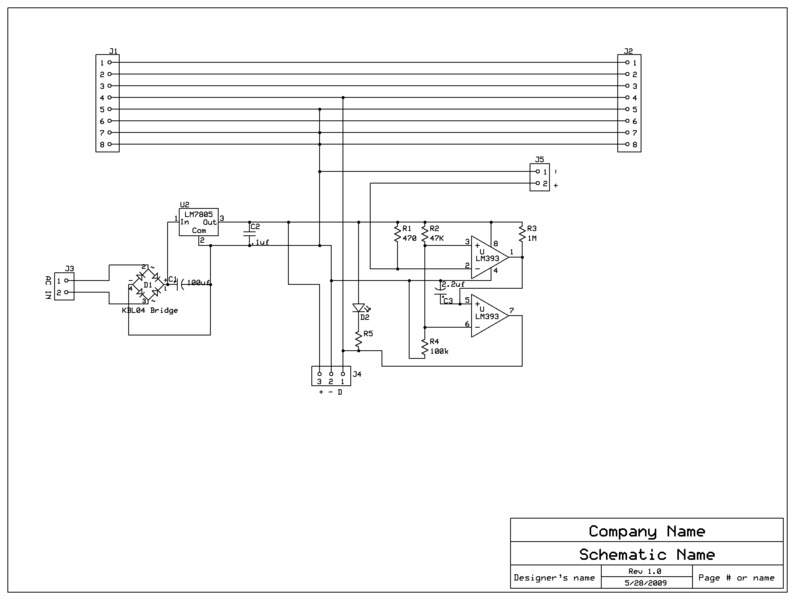

The HI-506 multiplexer functions as an analog input selector, which is controlled by a binary counter to select the appropriate channel. The HA-5330 serves as a high-speed sample and hold circuit. The sample/hold control is connected to the status (STS) output of the HI-774A; during a conversion process, the sample and hold circuit remains in hold mode. A conversion is triggered when the clock input transitions to a low state; when the clock input returns to a high state, the multiplexer address updates. While the ADC is converting the current input, which is held by the sample and hold circuit, the multiplexer acquires the next channel. The clock low duration should range from 225 ns to 6.5 µs, with the overall period exceeding 8.5 µs. With this timing configuration, the T/C signal will be high at the conclusion of a conversion, ensuring that the output data is valid 100 ns prior to the STS signal going low. This timing allows the STS signal to effectively clock the data into the storage register. The register address will be incremented by one; if this presents an issue, a 4-bit latch may be incorporated at the input of the storage register. At a clock rate of 100 kHz, each channel will be sampled every 160 µs.

The HI-506 multiplexer is designed for efficient analog signal routing, enabling the selection of multiple input channels based on binary-coded inputs. This device is particularly useful in applications requiring rapid switching between analog signals, such as in data acquisition systems. The integration of the HA-5330 sample and hold circuit enhances the system's performance by capturing and maintaining the voltage level of the selected input during the analog-to-digital conversion process.

The control logic of the system is crucial for ensuring that the timing relationships between the multiplexer, sample and hold circuit, and the analog-to-digital converter (ADC) are maintained. The connection between the sample and hold control and the STS output of the HI-774A ensures that the sample and hold circuit only updates its output when a conversion is actively taking place. This prevents any erroneous readings that could occur if the input signal were to change during the conversion process.

The specified clock timings are critical to the operation of the system. The low duration of the clock signal must be carefully managed to ensure that the multiplexer can select the next channel while the ADC processes the current input. The timing constraints also guarantee that the T/C signal provides valid data at the correct moment, facilitating seamless data transfer into the storage register.

In scenarios where the incremented register address may lead to complications, the introduction of a 4-bit latch can effectively manage the address offset, ensuring that the data is accurately recorded in the intended register. This additional component can help maintain data integrity and simplify the overall design by allowing for flexible addressing options.

With a clock frequency of 100 kHz, the system is capable of reading each channel every 160 µs, making it suitable for applications that require moderate-speed sampling of multiple analog signals. This operational speed, combined with the effective control logic and signal routing capabilities, positions the HI-506 multiplexer and associated components as a robust solution for analog signal processing tasks in various electronic applications. The HI-506 multiplexer is used as an analog input selector, controlled by a binary counter to address the appropr iate channel. The HA-5330 is a high-speed sample and hold. The sample/hold con- trol is tied to the status (STS) output of the HI-774A; whenever a conversion is in process, the S/H is in the hold mode. A conversion is initiated when the clock input becomes low; when the clock becomes high, the mux address changes.

The mux will be acquiring the next channel while the ADC is converting the present input, held by the S/H. The clock low time should be between 225 ns and 6.5 jus, with the period greater than 8.5 $. With this timing, T/C will be high at the end of a conversion, so the output data will be valid - 100 ns before STS goes low.

This allows STS to clock the data into the storage register. The register address will be offset by one; if this is a problem, a 4-bit latch can be added to the input of the storage register. With a 100-kHz clock rate, each channel will be read every 160us. 🔗 External reference

The HI-506 multiplexer is designed for efficient analog signal routing, enabling the selection of multiple input channels based on binary-coded inputs. This device is particularly useful in applications requiring rapid switching between analog signals, such as in data acquisition systems. The integration of the HA-5330 sample and hold circuit enhances the system's performance by capturing and maintaining the voltage level of the selected input during the analog-to-digital conversion process.

The control logic of the system is crucial for ensuring that the timing relationships between the multiplexer, sample and hold circuit, and the analog-to-digital converter (ADC) are maintained. The connection between the sample and hold control and the STS output of the HI-774A ensures that the sample and hold circuit only updates its output when a conversion is actively taking place. This prevents any erroneous readings that could occur if the input signal were to change during the conversion process.

The specified clock timings are critical to the operation of the system. The low duration of the clock signal must be carefully managed to ensure that the multiplexer can select the next channel while the ADC processes the current input. The timing constraints also guarantee that the T/C signal provides valid data at the correct moment, facilitating seamless data transfer into the storage register.

In scenarios where the incremented register address may lead to complications, the introduction of a 4-bit latch can effectively manage the address offset, ensuring that the data is accurately recorded in the intended register. This additional component can help maintain data integrity and simplify the overall design by allowing for flexible addressing options.

With a clock frequency of 100 kHz, the system is capable of reading each channel every 160 µs, making it suitable for applications that require moderate-speed sampling of multiple analog signals. This operational speed, combined with the effective control logic and signal routing capabilities, positions the HI-506 multiplexer and associated components as a robust solution for analog signal processing tasks in various electronic applications. The HI-506 multiplexer is used as an analog input selector, controlled by a binary counter to address the appropr iate channel. The HA-5330 is a high-speed sample and hold. The sample/hold con- trol is tied to the status (STS) output of the HI-774A; whenever a conversion is in process, the S/H is in the hold mode. A conversion is initiated when the clock input becomes low; when the clock becomes high, the mux address changes.

The mux will be acquiring the next channel while the ADC is converting the present input, held by the S/H. The clock low time should be between 225 ns and 6.5 jus, with the period greater than 8.5 $. With this timing, T/C will be high at the end of a conversion, so the output data will be valid - 100 ns before STS goes low.

This allows STS to clock the data into the storage register. The register address will be offset by one; if this is a problem, a 4-bit latch can be added to the input of the storage register. With a 100-kHz clock rate, each channel will be read every 160us. 🔗 External reference