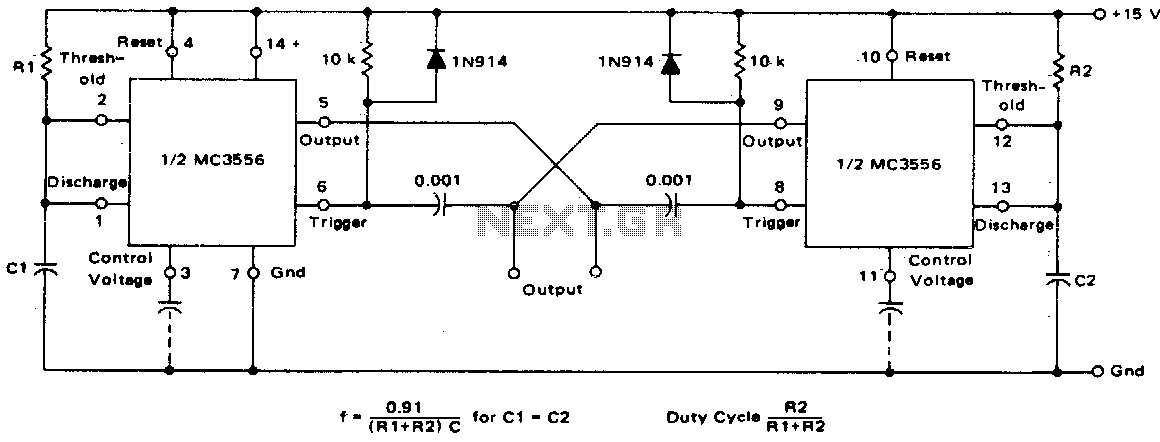

Dual astable multivibrator

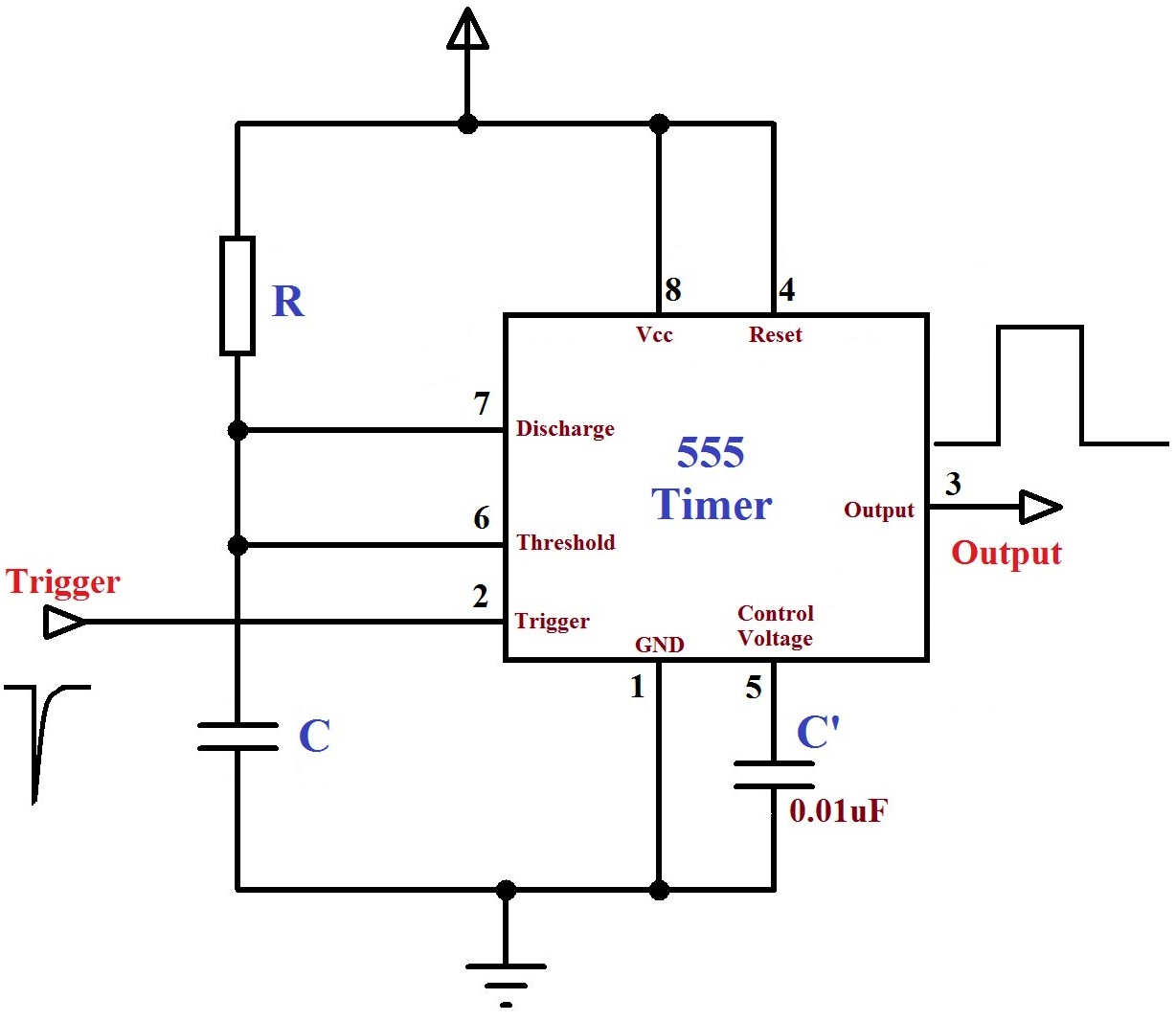

This dual astable multivibrator offers versatility not found in single timer circuits. The duty cycle can be adjusted from 5% to 95%. The two outputs generate two-phase clock signals, which are frequently required in digital systems. Additionally, it can be inhibited via either reset terminal.

The dual astable multivibrator is a fundamental electronic circuit that operates continuously between its high and low states, producing a square wave output. This configuration utilizes two timing resistors and capacitors, allowing for a wide range of duty cycle adjustments. The duty cycle, defined as the ratio of the time the output is high to the total period of the cycle, can be finely tuned from 5% to 95%, making this circuit highly adaptable for various applications in digital electronics.

In many digital systems, two-phase clock signals are essential for synchronizing operations between different components. The dual astable multivibrator provides two outputs that are 180 degrees out of phase, which can be utilized to drive flip-flops, counters, and other sequential logic devices. This feature enhances the circuit's utility in complex digital systems where timing and synchronization are critical.

The circuit includes reset terminals that allow for inhibition of the oscillation. By applying a signal to either reset terminal, the output can be forced to a low state, effectively halting the clock signals. This functionality is particularly useful in situations where it is necessary to pause operations or reset the timing sequence without altering the physical components of the circuit.

Overall, this dual astable multivibrator is a versatile and essential component in the design of digital systems, providing adjustable timing characteristics and dual-phase outputs that facilitate effective synchronization across various electronic applications.This dual astable multivibrator provides versatility not available with single timer circuits. The duty cycle can be adjusted from 5% to 95%. The two outputs provide two phase clock signals often required in digital systems It can also be inhibited by use of either reset terminal. 🔗 External reference

The dual astable multivibrator is a fundamental electronic circuit that operates continuously between its high and low states, producing a square wave output. This configuration utilizes two timing resistors and capacitors, allowing for a wide range of duty cycle adjustments. The duty cycle, defined as the ratio of the time the output is high to the total period of the cycle, can be finely tuned from 5% to 95%, making this circuit highly adaptable for various applications in digital electronics.

In many digital systems, two-phase clock signals are essential for synchronizing operations between different components. The dual astable multivibrator provides two outputs that are 180 degrees out of phase, which can be utilized to drive flip-flops, counters, and other sequential logic devices. This feature enhances the circuit's utility in complex digital systems where timing and synchronization are critical.

The circuit includes reset terminals that allow for inhibition of the oscillation. By applying a signal to either reset terminal, the output can be forced to a low state, effectively halting the clock signals. This functionality is particularly useful in situations where it is necessary to pause operations or reset the timing sequence without altering the physical components of the circuit.

Overall, this dual astable multivibrator is a versatile and essential component in the design of digital systems, providing adjustable timing characteristics and dual-phase outputs that facilitate effective synchronization across various electronic applications.This dual astable multivibrator provides versatility not available with single timer circuits. The duty cycle can be adjusted from 5% to 95%. The two outputs provide two phase clock signals often required in digital systems It can also be inhibited by use of either reset terminal. 🔗 External reference

%2Bdecoder%2BCircuit%2Bschematic%2Busing%2BM8870.png)