monostable multivibrator 555 timer

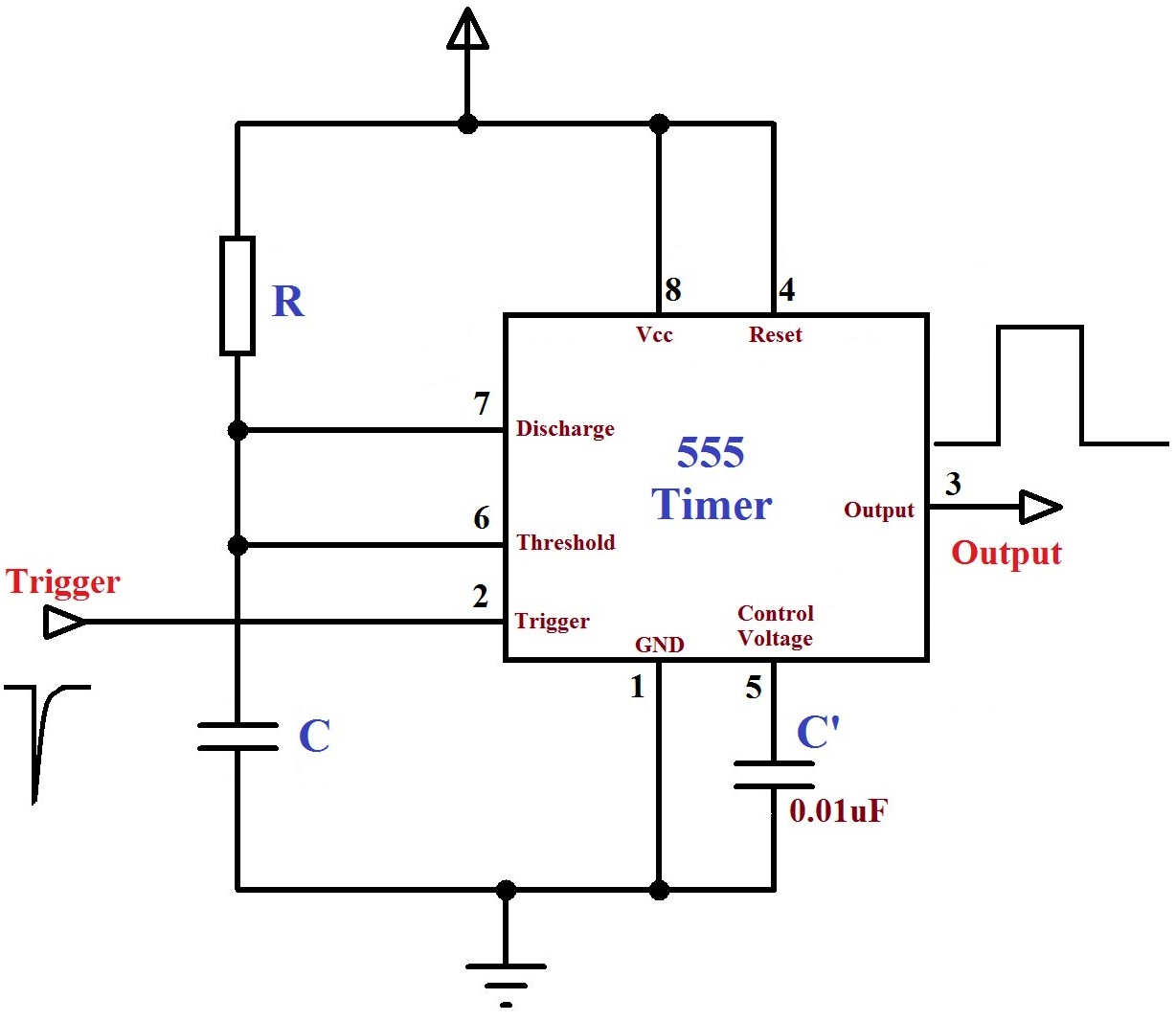

The monostable mode of the 555 Timer operates by having one stable state and switching to an unstable state for a predetermined time period T when triggered. The time period T is determined by the RC time constant in the circuit. This mode is commonly used for generating Pulse Width Modulated (PWM) waves. In this configuration, pin 8 and pin 1 of the 555 Timer are connected to the power supply (Vcc) and ground, respectively. Pin 4 serves as the Reset pin, which is active low and is connected to Vcc to prevent accidental resets. Pin 5 is the Control Voltage pin, which provides an external reference voltage to the internal comparators; it is grounded via a capacitor (0.01 µF) to filter out high-frequency noise. When a negative trigger is applied to the Trigger input of the 555 Timer, the output goes high, and the capacitor begins charging through resistor R. Once the capacitor voltage exceeds 2/3 Vcc, the output goes low, and the capacitor discharges through the Discharge pin of the 555 Timer. The duration of the unstable state is expressed by the formula T = 1.1RC. Upon receiving a negative trigger, the output of the lower comparator becomes high while the upper comparator remains low, resulting in a high output. After the initial trigger, the output of the lower comparator goes low, and the upper comparator stays low, maintaining the output in a high state. When the capacitor voltage reaches above 2/3 Vcc, the output of the upper comparator goes high while the lower comparator remains low, causing the output to switch to low.

The 555 Timer in monostable mode is a versatile component widely used in various applications such as timers, pulse generation, and frequency modulation. The circuit typically consists of the 555 Timer IC, a resistor (R), and a capacitor (C) that determine the time period for which the output remains high after being triggered. The resistor and capacitor values can be selected based on the desired timing requirements, allowing for a wide range of pulse widths.

The operation begins with the application of a negative pulse to the Trigger pin, which momentarily sets the output high. This transition triggers the internal flip-flop of the 555 Timer, which controls the output state. The charging of the capacitor through the resistor R causes the voltage across the capacitor to rise gradually. The time taken for the capacitor voltage to reach 2/3 Vcc can be calculated using the formula T = 1.1RC, where R is the resistance in ohms and C is the capacitance in farads.

The Reset pin is critical in ensuring that the circuit does not inadvertently reset during operation, which could disrupt the timing sequence. Grounding the Control Voltage pin with a capacitor serves to stabilize the internal reference voltage, minimizing the effects of noise that could affect the comparators' performance.

In summary, the monostable mode of the 555 Timer is a reliable and efficient method for generating precise timing pulses, with the output state being controlled by external components and the internal logic of the timer. The design allows for easy adjustments of the timing parameters, making it suitable for a variety of electronic applications.As its name indicates it has one stable state and it switches to unstable state for a predetermined time period T when it istriggered. The time period T is determined by the RC time constant in the circuit. Monostable mode of 555 Timer is commonly used for generating Pulse Width Modulated ( PWM ) waves. This is the circuit diagram of 555 Timer wired in Monostable mode. 8th pin and 1st pin of the 555 timer are used to givenpowerVcc and Ground respectively. 4th pin is the Reset pin of 555 Timer, which is active low so it is connected to Vcc to avoid accidental resets. 5th pin is the Control Voltage pin used to provide external reference voltage to internal comparators.

Since it is not used here, it is grounded via a capacitor C` (0. 01 µF) to avoid high frequency noises. When a negative trigger is applied on the Trigger input of 555, output goes high and capacitor starts charging through resistor R. When the capacitor voltage becomes greater than 2/3 Vcc, ouput goes low and capacitor starts discharging through the Discharge pin of 555 Timer.

Time period of the unstable state is given the tye expression, T = 1. 1RC. When a negative trigger is applied to the Trigger pin of 555 Timer, output of lower comparator will become HIGH and output of upper comparator will be LOW, since the capacitor voltage is zero. This makes the output HIGH. After the negative trigger, output of lower comparator becomes LOW and that of upper comparator remains LOW.

Since both inputs of the SR Flip Flop are LOW, output will not change, so the output is HIGH. When the capacitor voltage will become greater than 2/3 Vcc, output of upper comparator becomes HIGH and that of lower comparator remains LOW, so the output becomes LOW. 🔗 External reference

The 555 Timer in monostable mode is a versatile component widely used in various applications such as timers, pulse generation, and frequency modulation. The circuit typically consists of the 555 Timer IC, a resistor (R), and a capacitor (C) that determine the time period for which the output remains high after being triggered. The resistor and capacitor values can be selected based on the desired timing requirements, allowing for a wide range of pulse widths.

The operation begins with the application of a negative pulse to the Trigger pin, which momentarily sets the output high. This transition triggers the internal flip-flop of the 555 Timer, which controls the output state. The charging of the capacitor through the resistor R causes the voltage across the capacitor to rise gradually. The time taken for the capacitor voltage to reach 2/3 Vcc can be calculated using the formula T = 1.1RC, where R is the resistance in ohms and C is the capacitance in farads.

The Reset pin is critical in ensuring that the circuit does not inadvertently reset during operation, which could disrupt the timing sequence. Grounding the Control Voltage pin with a capacitor serves to stabilize the internal reference voltage, minimizing the effects of noise that could affect the comparators' performance.

In summary, the monostable mode of the 555 Timer is a reliable and efficient method for generating precise timing pulses, with the output state being controlled by external components and the internal logic of the timer. The design allows for easy adjustments of the timing parameters, making it suitable for a variety of electronic applications.As its name indicates it has one stable state and it switches to unstable state for a predetermined time period T when it istriggered. The time period T is determined by the RC time constant in the circuit. Monostable mode of 555 Timer is commonly used for generating Pulse Width Modulated ( PWM ) waves. This is the circuit diagram of 555 Timer wired in Monostable mode. 8th pin and 1st pin of the 555 timer are used to givenpowerVcc and Ground respectively. 4th pin is the Reset pin of 555 Timer, which is active low so it is connected to Vcc to avoid accidental resets. 5th pin is the Control Voltage pin used to provide external reference voltage to internal comparators.

Since it is not used here, it is grounded via a capacitor C` (0. 01 µF) to avoid high frequency noises. When a negative trigger is applied on the Trigger input of 555, output goes high and capacitor starts charging through resistor R. When the capacitor voltage becomes greater than 2/3 Vcc, ouput goes low and capacitor starts discharging through the Discharge pin of 555 Timer.

Time period of the unstable state is given the tye expression, T = 1. 1RC. When a negative trigger is applied to the Trigger pin of 555 Timer, output of lower comparator will become HIGH and output of upper comparator will be LOW, since the capacitor voltage is zero. This makes the output HIGH. After the negative trigger, output of lower comparator becomes LOW and that of upper comparator remains LOW.

Since both inputs of the SR Flip Flop are LOW, output will not change, so the output is HIGH. When the capacitor voltage will become greater than 2/3 Vcc, output of upper comparator becomes HIGH and that of lower comparator remains LOW, so the output becomes LOW. 🔗 External reference