FPGA RS232 Serial Interface Circuit

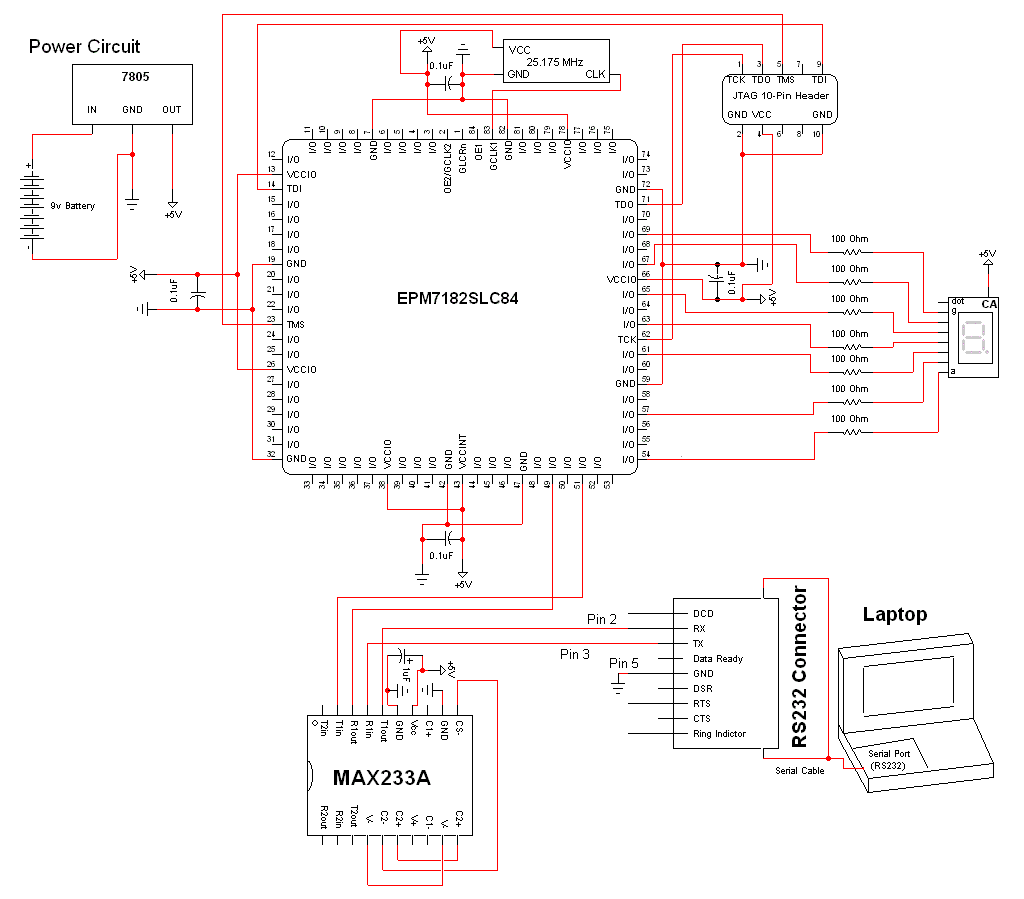

The schematic for this project is a modified version of the CPLD development board schematic. Several new components have been added for this project, and the completed schematic can be viewed below. The main components in the schematic are the CPLD development board, MAX233A, and a 7-segment display. The RS232 interface circuit includes the CPLD, a 5 MHz crystal clock, and the MAX233A. The MAX233A converts the +12V higher voltage RS232 signals into TTL +5V logic that the FPGA can interpret. This protoboard for a CPLD was developed a few years ago. It consists of a PLCC CPLD in a socket with power and JTAG connectors for programming. The oscillator was selected primarily due to availability; it serves as a timing device to maintain a reference time, and any clock above 10 MHz would be suitable for this project.

The project schematic integrates several key components to facilitate communication and processing. The CPLD (Complex Programmable Logic Device) serves as the core of the design, allowing for flexible logic configuration and control. The MAX233A is a critical component responsible for interfacing RS232 signals with the CPLD. It effectively translates the higher voltage levels of RS232 communication, which typically operate at ±12V, into TTL logic levels compatible with the CPLD's inputs and outputs. This translation is essential for ensuring reliable data transmission between the CPLD and any RS232 compliant devices.

The 5 MHz crystal oscillator provides the necessary clock signal for the CPLD, enabling synchronized operations within the circuit. This frequency is adequate for many applications, but higher frequencies can be utilized if required by the specific needs of the project. The selection of the oscillator was made based on availability, demonstrating the importance of having accessible components in the design process.

The 7-segment display is utilized in this schematic to provide a visual output, allowing users to observe the results of the CPLD's processing. The display is driven by the CPLD, which controls each segment's illumination based on the logic implemented in the device. This feature enhances the usability of the project by providing immediate feedback on its operation.

Overall, the modified CPLD development board schematic represents a practical implementation of digital logic design, showcasing the integration of various components to achieve a functional prototype. The choice of parts and their arrangement within the schematic reflects a balance between performance, availability, and ease of use, making this project a valuable reference for similar applications in electronics design.The schematic for this project is a modified version of the CPLD dev board schematic. There are a few new parts added for this project and you can see the completed schematic for this project below. The main parts in the schematic are the CPLD Dev Board, MAX233a and 7 Segment Display. The RS232 interface circuit consists of the CPLD, it`s 25. 17 5 MHz crystal clock and the MAX233A. The MAX233A translates the +12v higher voltage RS232 signals into TTL +5v logic that the FPGA can understand. This protoboard for a cpld was developed by me a few years ago. It`s really just a PLCC CPLD in a socket with power and JTAG connectors for programming. This oscillator was chosen mostly at random. We needed some type of timing device to keep a reference to time and I had this one laying around. Generally if you can find a clock above 10 MHz you`ll be fine for this project. 🔗 External reference

The project schematic integrates several key components to facilitate communication and processing. The CPLD (Complex Programmable Logic Device) serves as the core of the design, allowing for flexible logic configuration and control. The MAX233A is a critical component responsible for interfacing RS232 signals with the CPLD. It effectively translates the higher voltage levels of RS232 communication, which typically operate at ±12V, into TTL logic levels compatible with the CPLD's inputs and outputs. This translation is essential for ensuring reliable data transmission between the CPLD and any RS232 compliant devices.

The 5 MHz crystal oscillator provides the necessary clock signal for the CPLD, enabling synchronized operations within the circuit. This frequency is adequate for many applications, but higher frequencies can be utilized if required by the specific needs of the project. The selection of the oscillator was made based on availability, demonstrating the importance of having accessible components in the design process.

The 7-segment display is utilized in this schematic to provide a visual output, allowing users to observe the results of the CPLD's processing. The display is driven by the CPLD, which controls each segment's illumination based on the logic implemented in the device. This feature enhances the usability of the project by providing immediate feedback on its operation.

Overall, the modified CPLD development board schematic represents a practical implementation of digital logic design, showcasing the integration of various components to achieve a functional prototype. The choice of parts and their arrangement within the schematic reflects a balance between performance, availability, and ease of use, making this project a valuable reference for similar applications in electronics design.The schematic for this project is a modified version of the CPLD dev board schematic. There are a few new parts added for this project and you can see the completed schematic for this project below. The main parts in the schematic are the CPLD Dev Board, MAX233a and 7 Segment Display. The RS232 interface circuit consists of the CPLD, it`s 25. 17 5 MHz crystal clock and the MAX233A. The MAX233A translates the +12v higher voltage RS232 signals into TTL +5v logic that the FPGA can understand. This protoboard for a cpld was developed by me a few years ago. It`s really just a PLCC CPLD in a socket with power and JTAG connectors for programming. This oscillator was chosen mostly at random. We needed some type of timing device to keep a reference to time and I had this one laying around. Generally if you can find a clock above 10 MHz you`ll be fine for this project. 🔗 External reference

Warning: include(partials/cookie-banner.php): Failed to open stream: Permission denied in /var/www/html/nextgr/view-circuit.php on line 713

Warning: include(): Failed opening 'partials/cookie-banner.php' for inclusion (include_path='.:/usr/share/php') in /var/www/html/nextgr/view-circuit.php on line 713