Hardware design overview

The Openbench Logic Sniffer is an open-source logic analyzer designed to support the SUMP logic analyzer software at minimal cost. Source and design files can be downloaded from the Gadget Factory project page. The project originated from discussions in a forum, leading to initial circuit design, PCB layout, development, and testing under the code name Project SUMP PUMP. Many contributors provided ideas and feedback, with the Gadget Factory and Dangerous Prototypes coordinating circuit development and PCB routing. The design heavily utilized the Gadget Factory's Butterfly Platform. The Open Logic Sniffer is a specialized logic analyzer board that prioritizes low cost and high speed, sacrificing some features typical of full-scale development boards to achieve these goals. Assembled units can be purchased from Seeed Studio for $45, including worldwide shipping. SUMP, created by Michael Poppitz, is an open-source Java logic analyzer client that includes a VHDL logic capture engine for FPGAs and a Java client. The latest version of the SUMP client can be found on SourceForge.net. SUMP functions as a sampling logic analyzer, reading the state of input pins and storing samples in internal RAM before sending them to the computer client for analysis. The sample capacity is limited by the FPGA's RAM. SUMP is favored for its well-developed open-source logic analyzer toolchain, featuring professional capabilities such as multi-stage triggers, configurable pre-roll, external trigger, clock synchronization, and protocol analyzers (I2C, UART). Its open-source nature allows for the addition of new features, limited only by the user's imagination and coding skills. While SUMP is typically adapted for general-purpose FPGA development boards, this project takes a different approach by designing hardware specifically for SUMP while minimizing costs. Unlike professional logic analyzers, which offer numerous channels and extremely high speeds, the OLS does not aim to replace these tools for applications requiring high-frequency signal analysis. Various DIY logic analyzer designs exist, including parallel port-based analyzers and microcontroller-based devices, but these often have limitations in speed and performance. USB IO chip-based hobby logic analyzers, such as Saleae Logic and USBee, are currently popular, but they typically rely on software for triggering and processing, with maximum sampling speeds around 24Msps. The Open Logic Sniffer operates at sampling speeds up to 200Msps, independent of USB bus traffic, and features true hardware triggers. It offers more buffered channels than most hobby USB analyzers, although it has a finite sample capacity compared to the theoretically unlimited samples of hobby devices. Future versions of the OLS may include increased sample storage and an infinite sampling mode through firmware updates. A circuit diagram maintained by Uwe Bannow illustrates the basic elements of the Open Logic Sniffer hardware. The FPGA captures logic samples from 32 input pins into internal RAM and transmits the samples via a serial port for analysis on a computer using the SUMP client. A USB microcontroller converts the serial IO to a USB virtual serial port, allowing for upgrades through the USB connection. The microcontroller can program updated designs into the SPI flash data chip and can also be updated via its USB bootloader. A low pin count PIC was selected for its cost-effectiveness compared to other USB bridge options. It is USB 2.0 compliant, with a data transfer rate of up to 12Mbps, and utilizes an open virtual serial port CDC interface for compatibility across various platforms. Although the current SUMP FPGA design only supports a 115200bps serial UART for data transfer, additional connections between the PIC and FPGA allow for a future high-speed SPI interface, which can be implemented by adjusting the SUMP client settings. The project initially divided design work between microcontroller and FPGA sections, using Cadsoft Eagle for circuit and PCB design. The Xilinx Spartan 3E FPGA serves as the central component, sampling data from 16 buffered and 16 unbuffered IO pins and storing samples in internal RAM before transmitting them to a computer via USB.Openbench Logic Sniffer is an open source logic analyzer. It`s designed to support the SUMP logic analyzer software at the lowest possible cost. Download the source and design files from the Gadget Factory project page. This project started in the comments on a post. Initial circuit design, PCB layout, development, and testing continued in t he forum under the code name Project SUMP PUMP. Many, many people contributed ideas and advice, the Gadget Factory and Dangerous Prototypes coordinated circuit development and routed the PCB. We borrowed heavily from the Gadget Factory`s Butterfly Platform. The Open Logic Sniffer is a purpose-built logic analyzer board designed to be low cost but high speed.

It sacrifices a lot of the features you`d look for in a full-scale development board to achieve our primary goals: You can get your own assembled Open Logic Sniffer at Seeed Studio for $45, including worldwide shipping. Continue reading about the design and collaboration below. SUMP is an open source Java logic analyzer client by Michael Poppitz. It consists of two parts, a VHDL logic capture engine for FPGAs, and a Java logic analyzer client. The latest development version of the SUMP client is available from SourceForge. net. SUMP is a sampling logic analyzer. It reads the state of the input pins and stores the samples in internal ram. It then dumps the samples back to the computer client for analysis. The number of samples possible is limited by the RAM in the FPGA. We like SUMP because it`s the best developed open source logic analyzer toolchain currently available.

It has lots of professional features like multi-stage triggers, configurable pre-roll, external trigger and clock sync, and a few protocol analyzers (I2C, UART). It`s open source, so the potential to add cool new features is limited only by your imagination and coding skills.

SUMP is typically ported to a general-purpose FPGA development board. We took a different approach and designed hardware specifically for SUMP, while constraining costs wherever possible. Professional logic analyzers have tons of channels and super high speeds. We`re not trying to make a low cost DIY version of these tools, the OLS isn`t an alternative to these types of tools if you need to sniff 100MHz+ signals and have huge sample sizes.

Being an engineer`s tool, there are plenty of DIY logic analyzer designs. Parallel port based logic analyzers used to be all the rage, but with parallel ports and direct interrupt access disappearing from systems, these are just historical curiosities. Another type of DIY logic analyzer is a microcontroller-based device. There are several with custom interfaces like the PIC Logix, Scanalogic, and AVR Logic Analyzer. The Bus Pirate works with SUMP. Microcontroller analyzers all have one thing in common: they`re really slow, usually sub-megahertz. USB IO chip-based hobby logic analyzers are currently popular. We`ve always been fans of the Saleae Logic, the USBee is similar. These devices are just a USB IO chip like a CY7C68013A-56PVXC, with all trigger and processing logic done in software on a computer.

The hardware part is just a datalogger. The top sampling speed is usually around 24Msps (24MHz), if the conditions on your USB bus are just right. They can take `unlimited` samples because everything is stored on the computer. Current models tend to be 8 channels, more channels would reduce the maximum speed proportionately. These are commercial products with highly polished user interfaces, we don`t know of any that are open source.

The Open Logic Sniffer sits somewhere between hobby analyzers and professional analyzers. The OLS samples up to 200Msps, regardless of the USB bus traffic, and has true hardware triggers. The OLS has twice as many buffered channels as most hobby USB analyzers, and four times more channels overall. The major difference is that the OLS has a limited number of samples, while the hobby USB analyzers can theoretically take infinite samples.

Most of our debugging is done with the first few hundred samples, so this feature isn`t usually important to our work, your situation may be different. Future versions of the OLS will definitely have more sample storage, and we can work an infinite sampling mode into a future firmware update too.

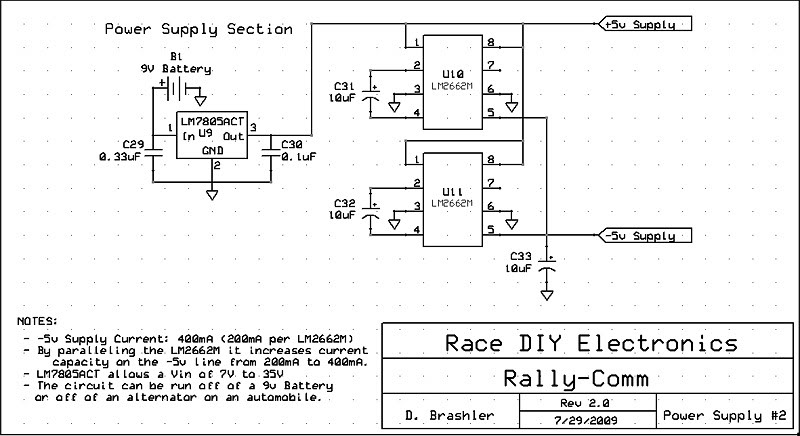

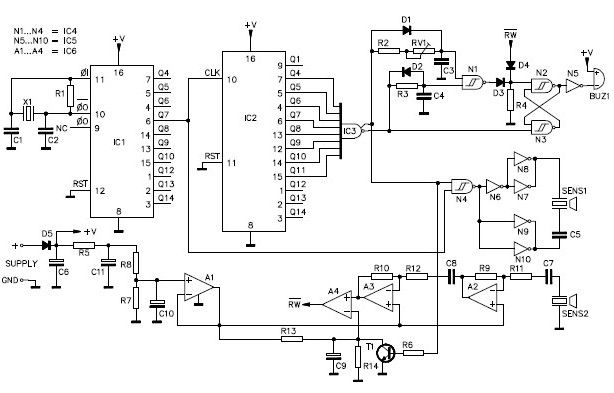

Click for a full size circuit diagram [PNG]. This circuit diagram, maintained by Uwe Bannow, shows the basic elements of the Open Logic Sniffer hardware. The FPGA captures logic samples from 32 input pins into internal RAM. The samples are dumped out a serial port for analysis on a computer. The open source SUMP logic analyzer client is used to capture and visualize the samples. The FPGA only communicates over a serial port, so we used a USB microcontroller to convert the serial IO to a USB virtual serial port.

The entire chain is upgradable through the USB connection. The microcontroller can program updated logic analyzer designs into the SPI flash data chip, and the microcontroller can also be updated from its USB bootloader. We chose a USB microcontroller over a dedicated USB interface chip. A low pincount PIC was cheaper than most other USB bridge options. It`s USB 2. 0 compliant, and can transfer data at up to 12Mbps. We`re using it with the completely open virtual serial port CDC interface, so it will work on almost any platform without proprietary drivers.

The PIC can also implement other USB transfer protocols with a firmware update, faster connection methods can be supported when someone adds support for them to the SUMP client software. Currently the SUMP FPGA design only transfers data over a 115200bps serial UART, the speed between the USB PIC and the computer isn`t a bottleneck.

We routed several extra connections between the PIC and FPGA to implement a high-speed SPI interface in the future. The speed increase of an SPI interface can be supported in the SUMP client just by adding higher serial port speed settings.

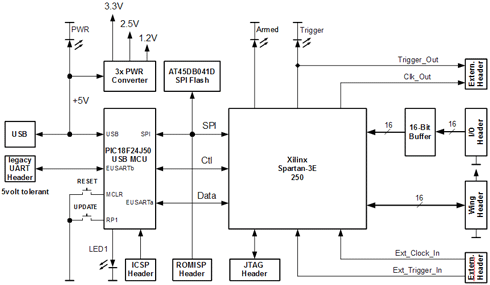

With so much to accomplish already, major modifications to the client to work with untested hardware and custom drivers didn`t seem appealing. Not if the project were ever going to get finished. The PIC seemed like the best route for the first version. Click for a large image of the schematic [PNG]. The schematic is divided into a microcontroller part [PNG] and a FPGA part [PNG]. These sections are where Ian and Jack initially split the design work. We used the freeware version of Cadsoft Eagle to make the circuit and PCB. Download the latest files from the Gadget Factory project page. A Xilinx Spartan 3E field programmable gate array ( FPGA ) is the central component of the logic analyzer.

The FPGA samples data from 16 buffered and 16 unbuffered IO pins, and stores the samples in internal RAM. The samples are later dumped out a serial UART to the PIC, and from the PIC to a computer via USB. . 🔗 External reference

It sacrifices a lot of the features you`d look for in a full-scale development board to achieve our primary goals: You can get your own assembled Open Logic Sniffer at Seeed Studio for $45, including worldwide shipping. Continue reading about the design and collaboration below. SUMP is an open source Java logic analyzer client by Michael Poppitz. It consists of two parts, a VHDL logic capture engine for FPGAs, and a Java logic analyzer client. The latest development version of the SUMP client is available from SourceForge. net. SUMP is a sampling logic analyzer. It reads the state of the input pins and stores the samples in internal ram. It then dumps the samples back to the computer client for analysis. The number of samples possible is limited by the RAM in the FPGA. We like SUMP because it`s the best developed open source logic analyzer toolchain currently available.

It has lots of professional features like multi-stage triggers, configurable pre-roll, external trigger and clock sync, and a few protocol analyzers (I2C, UART). It`s open source, so the potential to add cool new features is limited only by your imagination and coding skills.

SUMP is typically ported to a general-purpose FPGA development board. We took a different approach and designed hardware specifically for SUMP, while constraining costs wherever possible. Professional logic analyzers have tons of channels and super high speeds. We`re not trying to make a low cost DIY version of these tools, the OLS isn`t an alternative to these types of tools if you need to sniff 100MHz+ signals and have huge sample sizes.

Being an engineer`s tool, there are plenty of DIY logic analyzer designs. Parallel port based logic analyzers used to be all the rage, but with parallel ports and direct interrupt access disappearing from systems, these are just historical curiosities. Another type of DIY logic analyzer is a microcontroller-based device. There are several with custom interfaces like the PIC Logix, Scanalogic, and AVR Logic Analyzer. The Bus Pirate works with SUMP. Microcontroller analyzers all have one thing in common: they`re really slow, usually sub-megahertz. USB IO chip-based hobby logic analyzers are currently popular. We`ve always been fans of the Saleae Logic, the USBee is similar. These devices are just a USB IO chip like a CY7C68013A-56PVXC, with all trigger and processing logic done in software on a computer.

The hardware part is just a datalogger. The top sampling speed is usually around 24Msps (24MHz), if the conditions on your USB bus are just right. They can take `unlimited` samples because everything is stored on the computer. Current models tend to be 8 channels, more channels would reduce the maximum speed proportionately. These are commercial products with highly polished user interfaces, we don`t know of any that are open source.

The Open Logic Sniffer sits somewhere between hobby analyzers and professional analyzers. The OLS samples up to 200Msps, regardless of the USB bus traffic, and has true hardware triggers. The OLS has twice as many buffered channels as most hobby USB analyzers, and four times more channels overall. The major difference is that the OLS has a limited number of samples, while the hobby USB analyzers can theoretically take infinite samples.

Most of our debugging is done with the first few hundred samples, so this feature isn`t usually important to our work, your situation may be different. Future versions of the OLS will definitely have more sample storage, and we can work an infinite sampling mode into a future firmware update too.

Click for a full size circuit diagram [PNG]. This circuit diagram, maintained by Uwe Bannow, shows the basic elements of the Open Logic Sniffer hardware. The FPGA captures logic samples from 32 input pins into internal RAM. The samples are dumped out a serial port for analysis on a computer. The open source SUMP logic analyzer client is used to capture and visualize the samples. The FPGA only communicates over a serial port, so we used a USB microcontroller to convert the serial IO to a USB virtual serial port.

The entire chain is upgradable through the USB connection. The microcontroller can program updated logic analyzer designs into the SPI flash data chip, and the microcontroller can also be updated from its USB bootloader. We chose a USB microcontroller over a dedicated USB interface chip. A low pincount PIC was cheaper than most other USB bridge options. It`s USB 2. 0 compliant, and can transfer data at up to 12Mbps. We`re using it with the completely open virtual serial port CDC interface, so it will work on almost any platform without proprietary drivers.

The PIC can also implement other USB transfer protocols with a firmware update, faster connection methods can be supported when someone adds support for them to the SUMP client software. Currently the SUMP FPGA design only transfers data over a 115200bps serial UART, the speed between the USB PIC and the computer isn`t a bottleneck.

We routed several extra connections between the PIC and FPGA to implement a high-speed SPI interface in the future. The speed increase of an SPI interface can be supported in the SUMP client just by adding higher serial port speed settings.

With so much to accomplish already, major modifications to the client to work with untested hardware and custom drivers didn`t seem appealing. Not if the project were ever going to get finished. The PIC seemed like the best route for the first version. Click for a large image of the schematic [PNG]. The schematic is divided into a microcontroller part [PNG] and a FPGA part [PNG]. These sections are where Ian and Jack initially split the design work. We used the freeware version of Cadsoft Eagle to make the circuit and PCB. Download the latest files from the Gadget Factory project page. A Xilinx Spartan 3E field programmable gate array ( FPGA ) is the central component of the logic analyzer.

The FPGA samples data from 16 buffered and 16 unbuffered IO pins, and stores the samples in internal RAM. The samples are later dumped out a serial UART to the PIC, and from the PIC to a computer via USB. . 🔗 External reference